U.A.6

SEL-421 Relay User’s Guide Date Code 20090715

Firmware and Manual Versions

Firmware

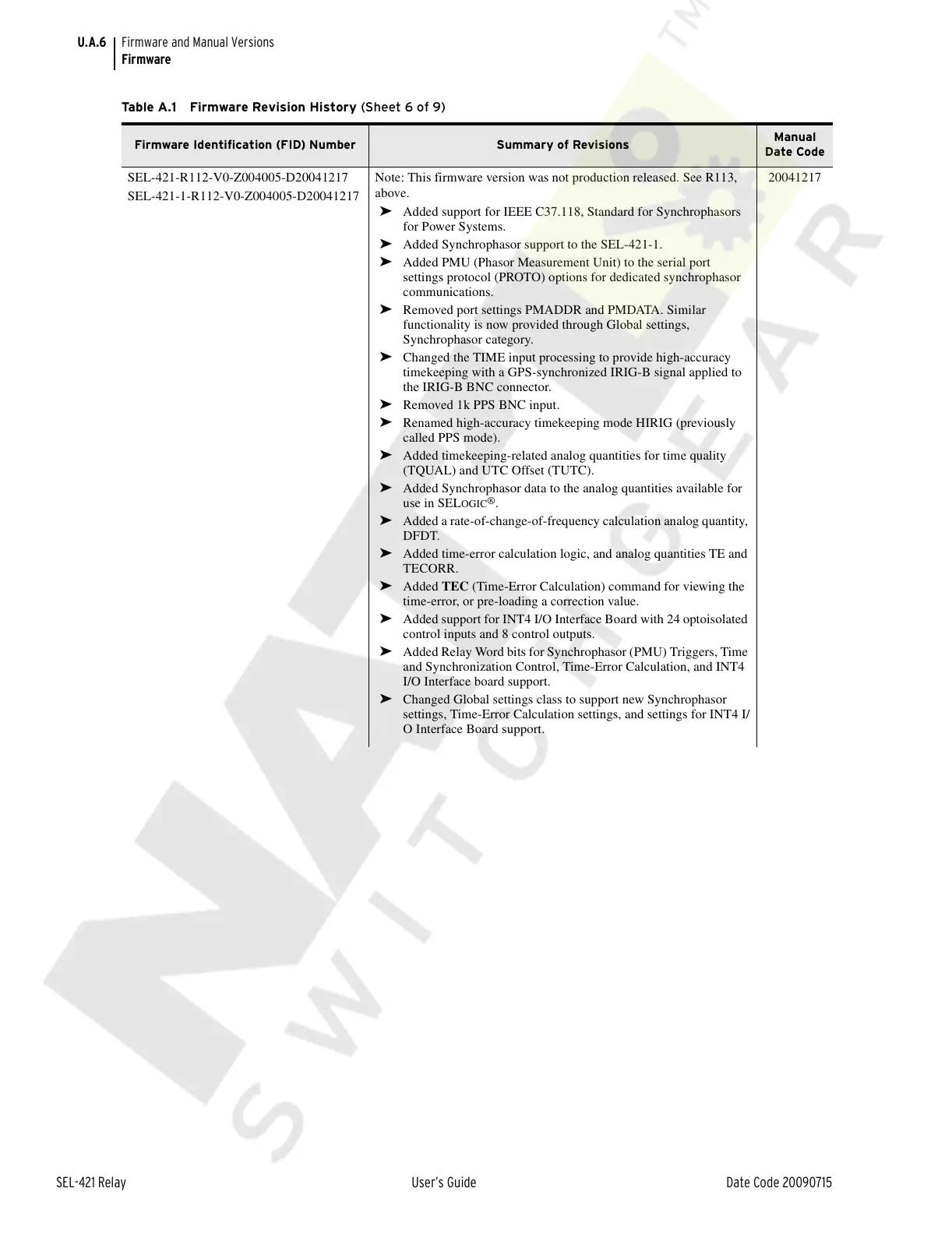

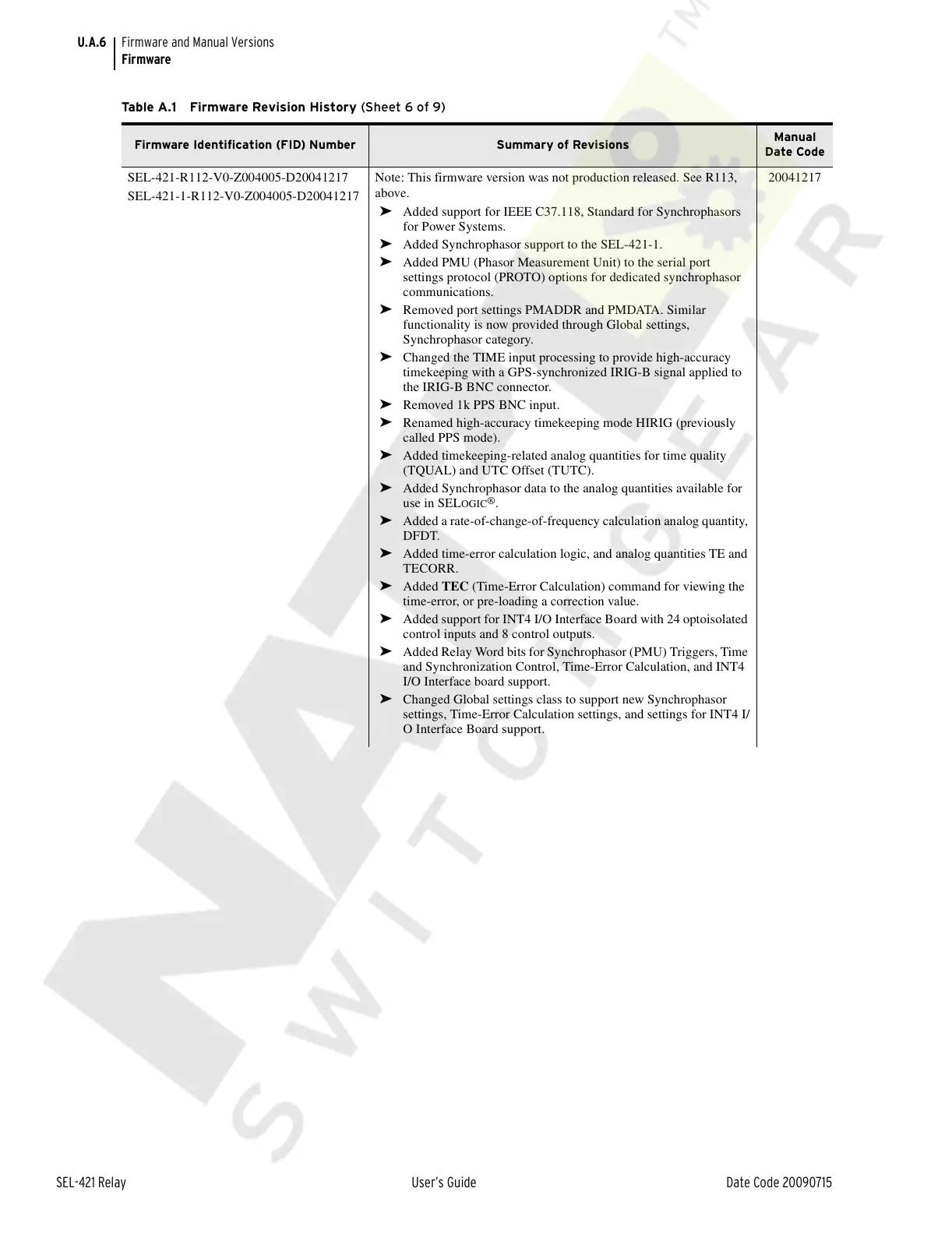

SEL-421-R112-V0-Z004005-D20041217

SEL-421-1-R112-V0-Z004005-D20041217

Note: This firmware version was not production released. See R113,

above.

➤ Added support for IEEE C37.118, Standard for Synchrophasors

for Power Systems.

➤ Added Synchrophasor support to the SEL-421-1.

➤ Added PMU (Phasor Measurement Unit) to the serial port

settings protocol (PROTO) options for dedicated synchrophasor

communications.

➤ Removed port settings PMADDR and PMDATA. Similar

functionality is now provided through Global settings,

Synchrophasor category.

➤ Changed the TIME input processing to provide high-accuracy

timekeeping with a GPS-synchronized IRIG-B signal applied to

the IRIG-B BNC connector.

➤ Removed 1k PPS BNC input.

➤ Renamed high-accuracy timekeeping mode HIRIG (previously

called PPS mode).

➤ Added timekeeping-related analog quantities for time quality

(TQUAL) and UTC Offset (TUTC).

➤ Added Synchrophasor data to the analog quantities available for

use in SEL

OGIC

®

.

➤ Added a rate-of-change-of-frequency calculation analog quantity,

DFDT.

➤ Added time-error calculation logic, and analog quantities TE and

TECORR.

➤ Added TEC (Time-Error Calculation) command for viewing the

time-error, or pre-loading a correction value.

➤ Added support for INT4 I/O Interface Board with 24 optoisolated

control inputs and 8 control outputs.

➤ Added Relay Word bits for Synchrophasor (PMU) Triggers, Time

and Synchronization Control, Time-Error Calculation, and INT4

I/O Interface board support.

➤ Changed Global settings class to support new Synchrophasor

settings, Time-Error Calculation settings, and settings for INT4 I/

O Interface Board support.

20041217

Table A.1 Firmware Revision History (Sheet 6 of 9)

Firmware Identification (FID) Number Summary of Revisions

Manual

Date Code

Courtesy of NationalSwitchgear.com

Loading...

Loading...