RM0453 Rev 2 1405/1454

RM0453 Debug support (DBG)

1441

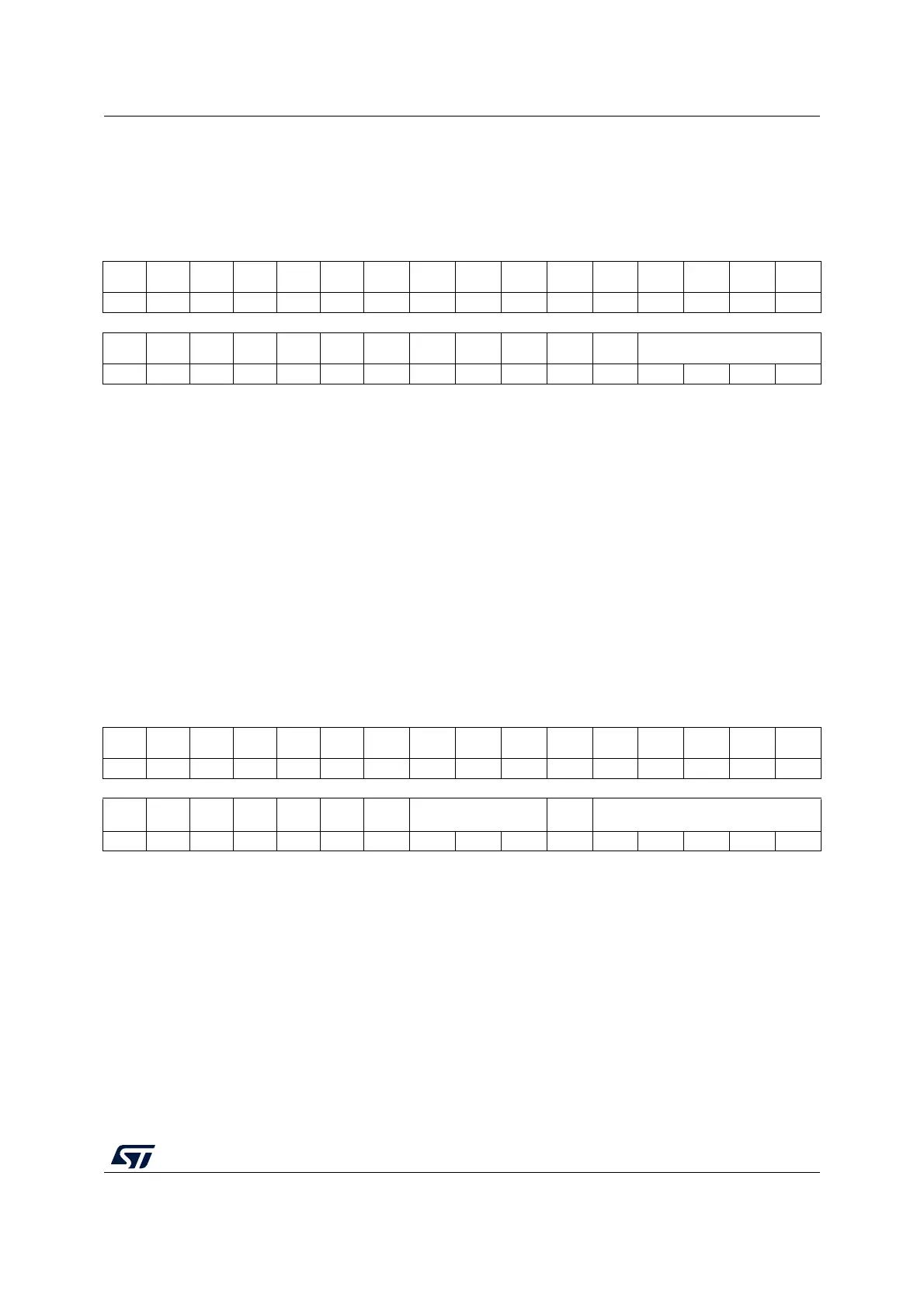

38.11.9 TPIU claim tag clear register (TPIU_CLAIMCLR)

Address offset: 0xFA4

Reset value: 0x0000 0000

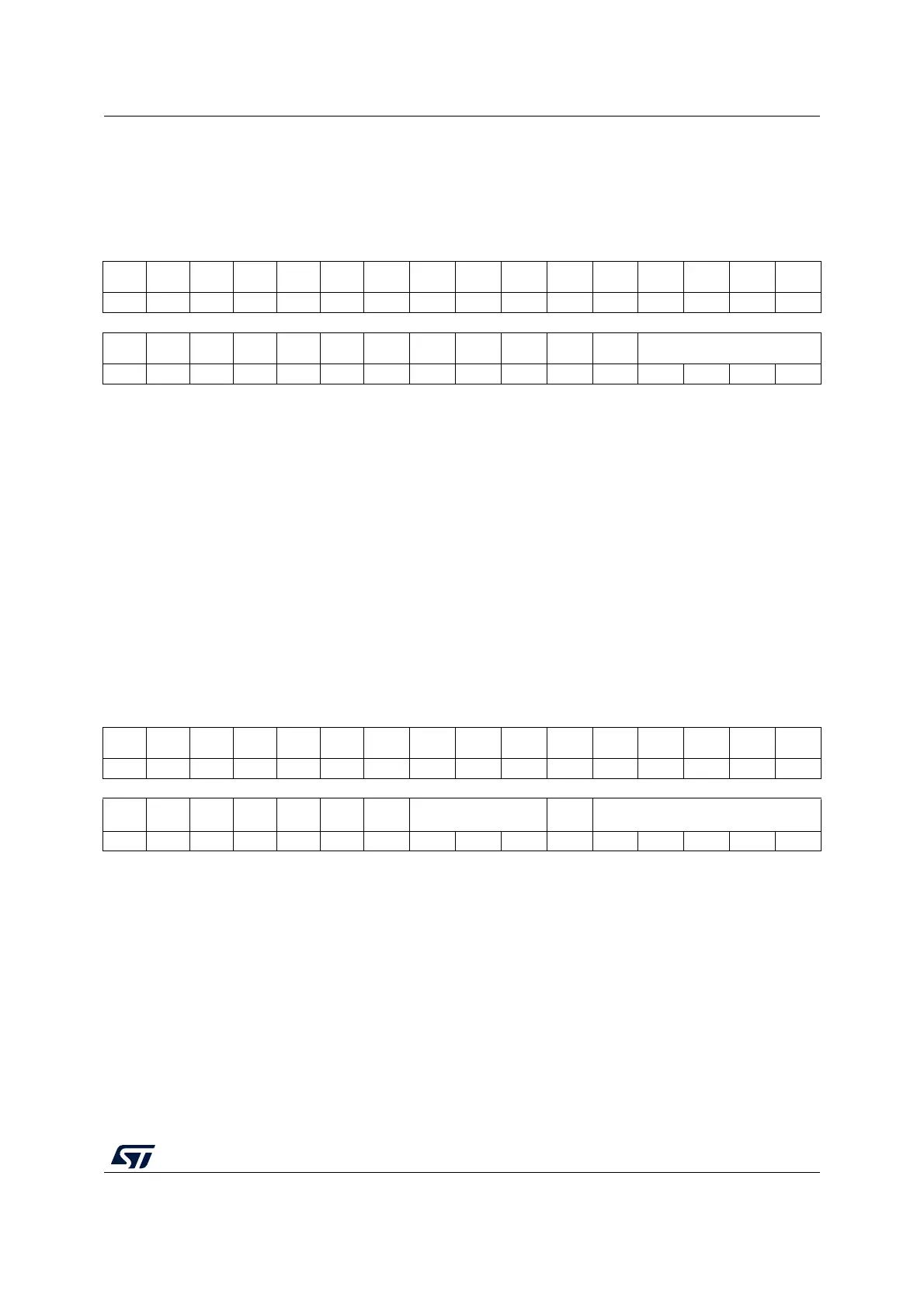

38.11.10 TPIU device configuration register (TPIU_DEVIDR)

Address offset: 0xFC8

Reset value: 0x0000 0CA0

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. CLAIMCLR[3:0]

rw rw rw rw

Bits 31:4 Reserved, must be kept at reset value.

Bits 3:0 CLAIMCLR[3:0]: resets claim tag bits

Write:

0000: No effect

xxx1: Clears bit 0.

xx1x: Clears bit 1.

x1xx: Clears bit 2.

1xxx: Clears bit 3.

Read: Returns current value of claim tag.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res.

SWON

RZ

SWOM

AN

TCLKD

ATA

FIFOSIZE[2:0]

CLKRE

LAT

MAXNUM[4:0]

rrrrrrrrrrrr

Bits 31:12 Reserved, must be kept at reset value.

Bit 11 SWONRZ: indicates whether serial-wire output, NRZ, is supported

1: Supported

Bit 10 SWOMAN: indicates whether serial-wire output, Manchester encoded format, is supported

1: Supported

Bit 9 TCLKDATA: indicates whether trace clock plus data is supported

0: Supported

Loading...

Loading...