RM0453 Rev 2 1421/1454

RM0453 Debug support (DBG)

1441

ROM2 occupies a 4-Kbyte, 32-bit wide chunk of APB-D address space, from 0xE00FF000

to 0xE00FFFFC.

The topology for the CoreSight components in the CPU2 subsystem is shown in Figure 392.

0xF0000008 Not used - - - 0x00002002

0xF000000C Not used - - - 0x10000002

0xF0000010 Top of table - - - 0x00000000

0xF000000C to

0xF0000FC8

Reserved - - - 0x00000000

0xF0000FCC to

0xF0000FFC

ROM table registers - - - See Table 285

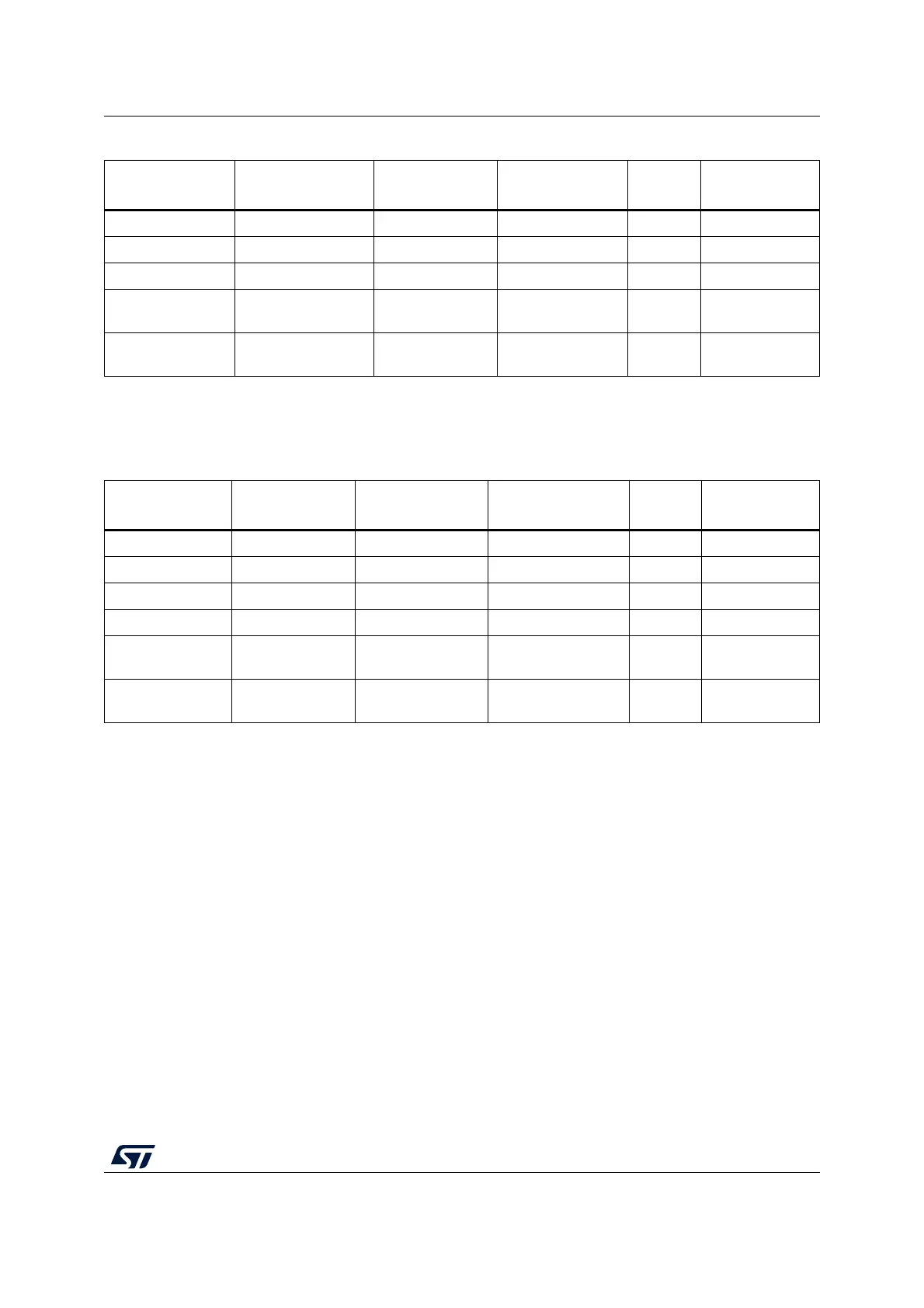

Table 283. ROM1 table

Address in ROM

table

Component name

Component base

address

Component

address offset

Size Entry

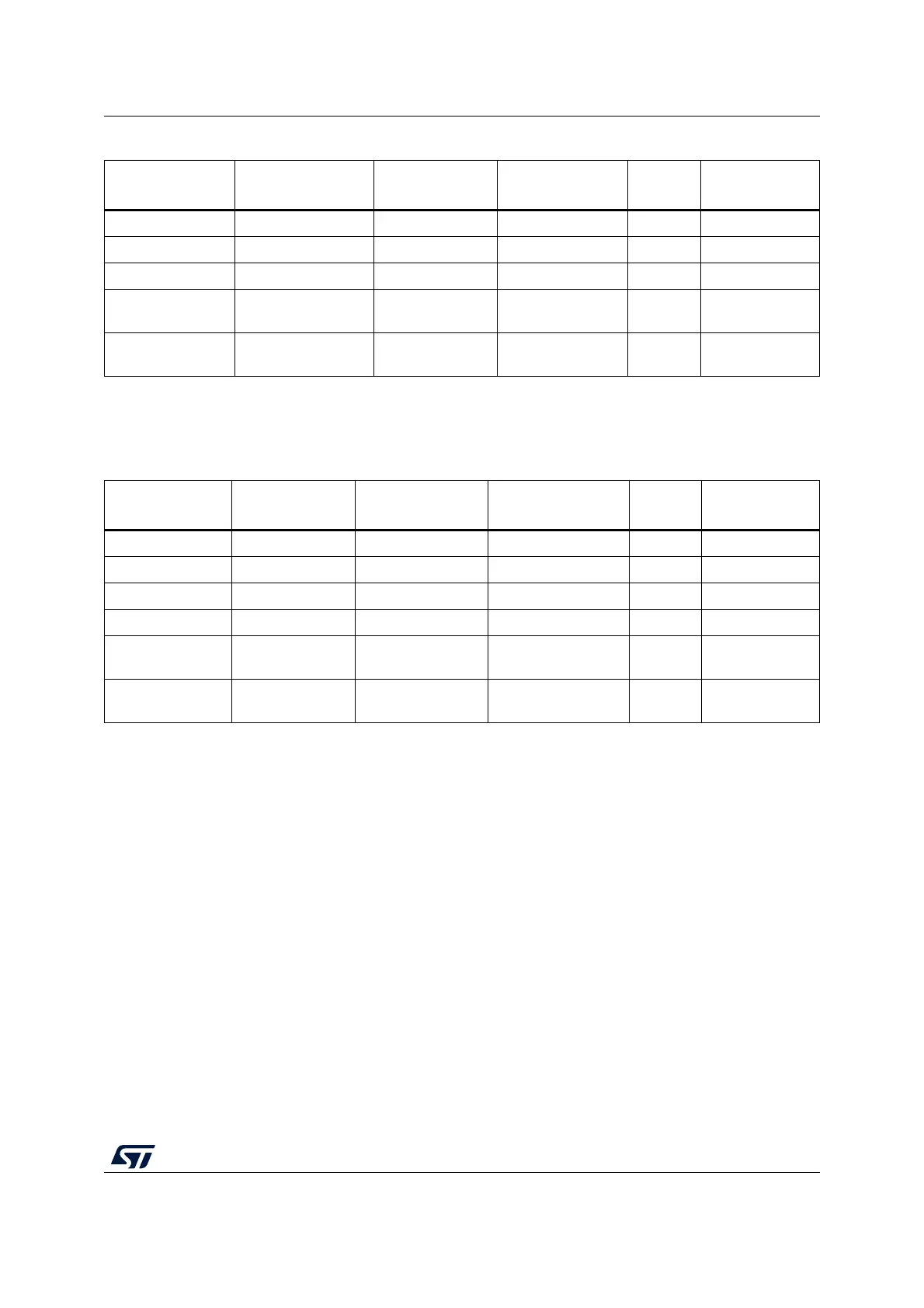

Table 284. ROM2 table

Address in ROM

table

Component

name

Component base

address

Component

address offset

Size Entry

0xE00FF000 SCS 0xE000E000 0xFFF0F000 4 KB 0xFFF0F003

0xE00FF004 DWT 0xE0001000 0xFFF02000 4 KB 0xFFF02003

0xE00FF008 BPU 0xE0002000 0xFFF03000 4 KB 0xFFF03003

0xE00FF00C Top of table - - - 0x00000000

0xE00FF010 to

0xE00FFFC8

Reserved - - - 0x00000000

0xE00FFFCC to

0xE00FFFFC

ROM table

registers

---See Table 286

Loading...

Loading...