General-purpose I/Os (GPIO) RM0453

412/1454 RM0453 Rev 2

10.4.17 GPIOC output data register (GPIOC_ODR)

Address offset: 0x0814

Reset value: 0x0000 0000

Bit 13 ID13: Port PC13 input data bit

Bits 12:7 Reserved, must be kept at reset value.

Bit 6 ID6: Port PC6 input data bit

Bit 5 ID5: Port PC5 input data bit

Bit 4 ID4: Port PC4 input data bit

Bit 3 ID3: Port PC3 input data bit

Bit 2 ID2: Port PC2 input data bit

Bit 1 ID1: Port PC1 input data bit

Bit 0 ID0: Port PC0 input data bit

These bits are read-only. They contain the input value of the corresponding I/O port.

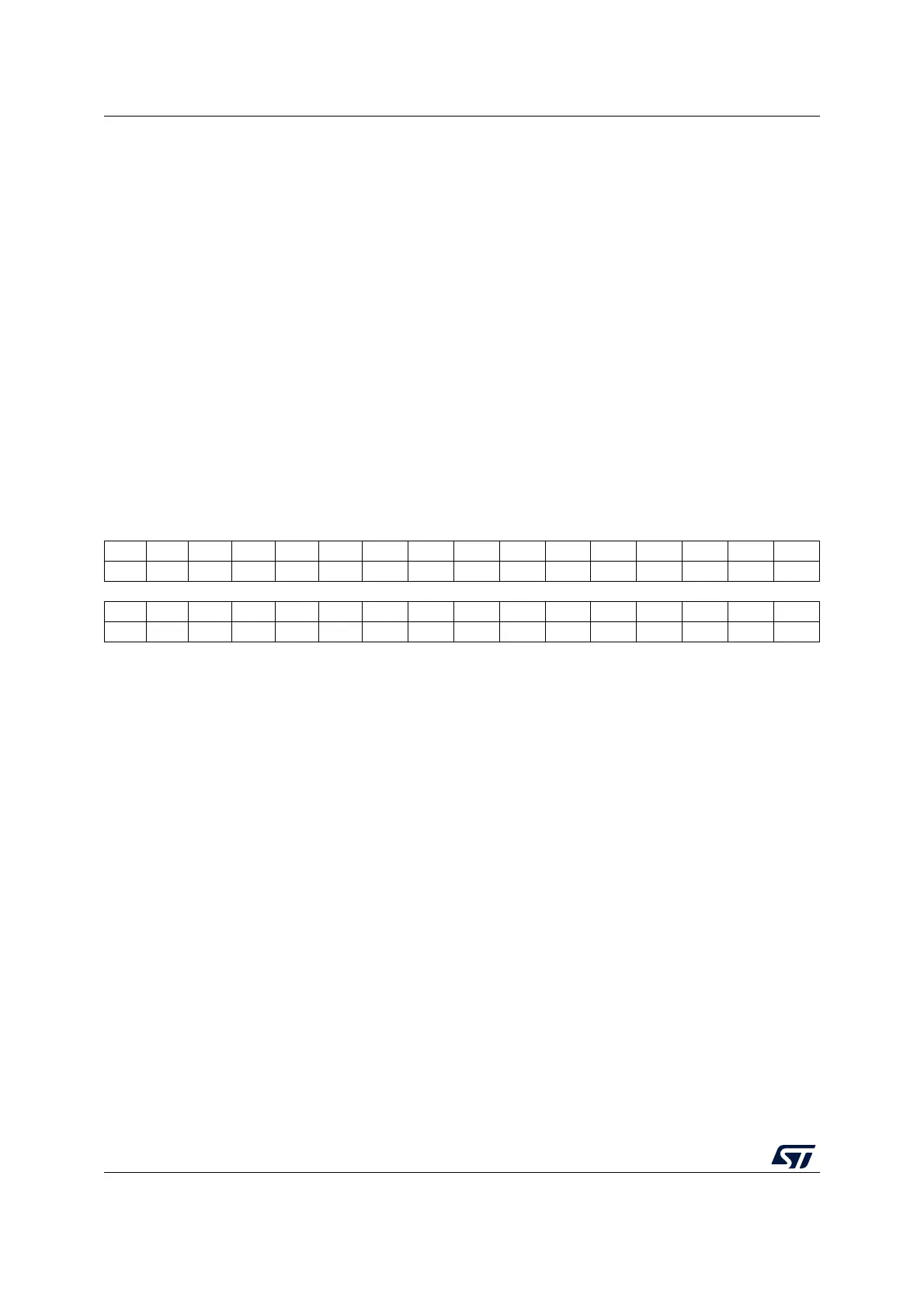

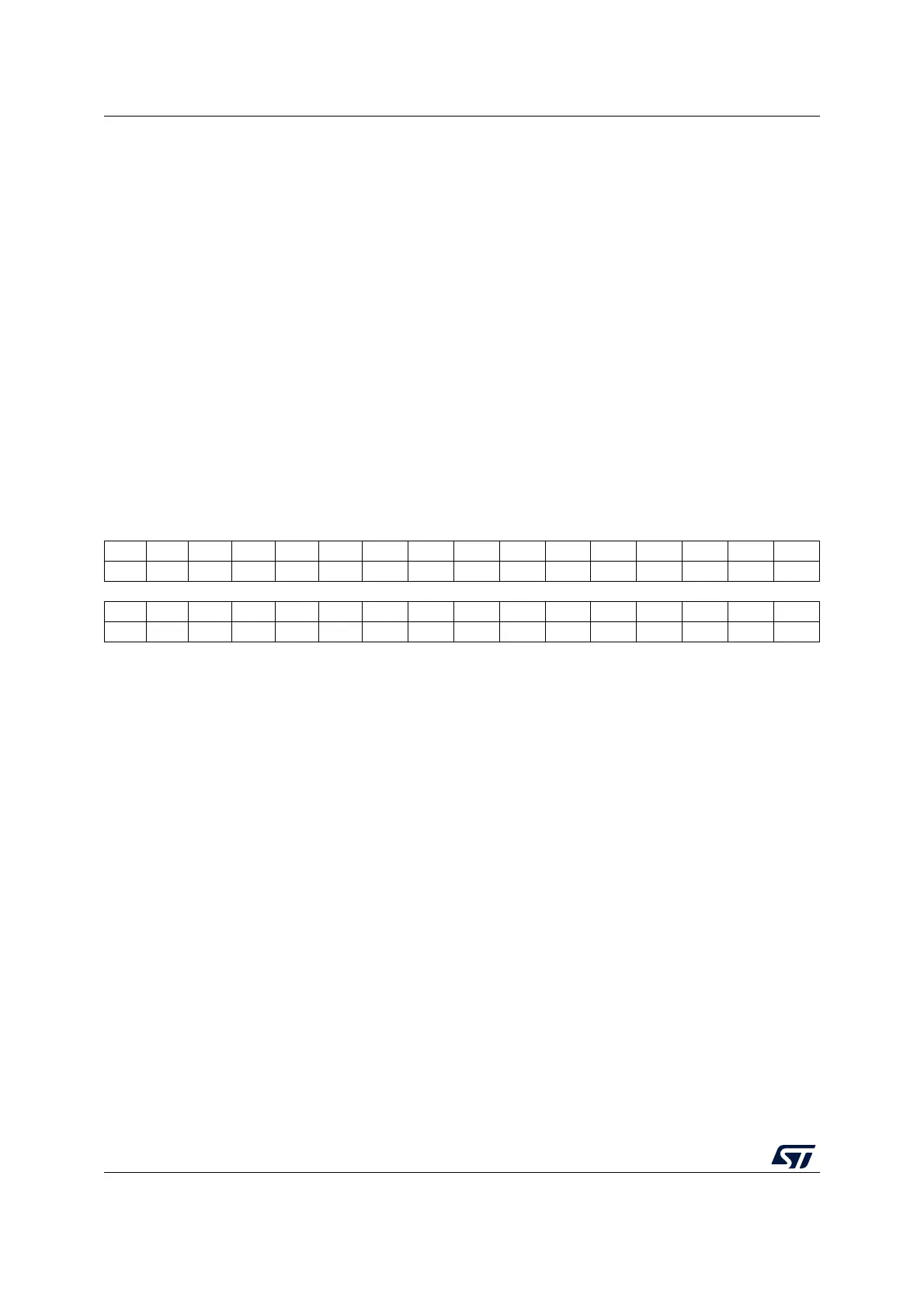

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

OD15 OD14 OD13 Res. Res. Res. Res. Res. Res. OD6 OD5 OD4 OD3 OD2 OD1 OD0

rw rw rw rw rw rw rw rw rw rw

Bits 31:16 Reserved, must be kept at reset value.

Bit 15 OD15: Port PC15 output data bit

Bit 14 OD14: Port PC14 output data bit

Bit 13 OD13: Port PC13 output data bit

Bits 12:7 Reserved, must be kept at reset value.

Bit 6 OD6: Port PC6 output data bit

Bit 5 OD5: Port PC5 output data bit

Bit 4 OD4: Port PC4 output data bit

Bit 3 OD3: Port PC3 output data bit

Bit 2 OD2: Port PC2 output data bit

Bit 1 OD1: Port PC1 output data bit

Bit 0 OD0: Port PC0 output data bit

These bits can be read and written by software.

Note: For atomic bit set/reset, OD bits can be individually set and/or reset by writing to the

GPIOC_BSRR and GPIOC_BRR registers.

Loading...

Loading...