RM0453 Rev 2 417/1454

RM0453 General-purpose I/Os (GPIO)

426

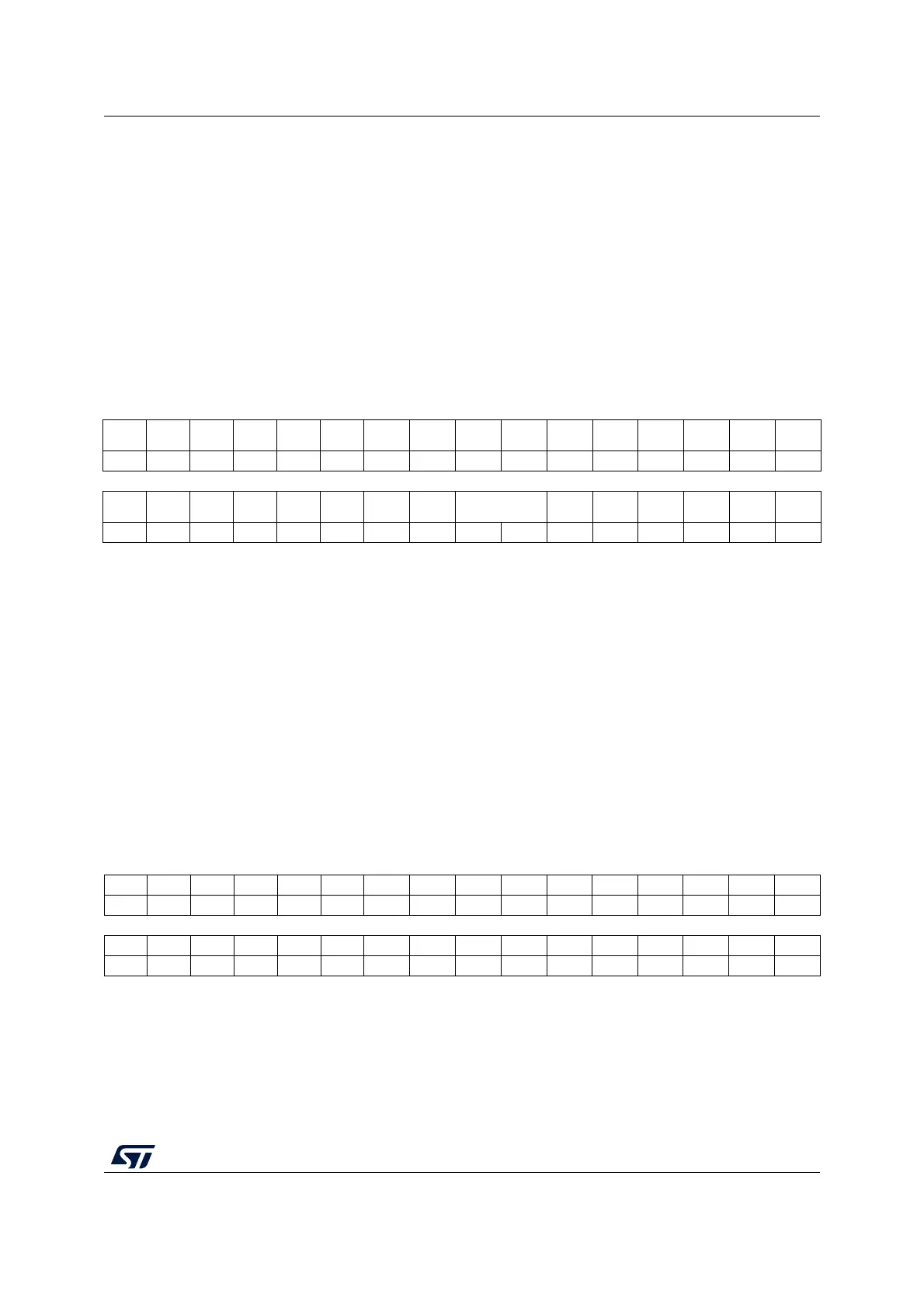

10.4.23 GPIOH mode register (GPIOH_MODER)

Address offset: 0x1C00

Reset value: 0x0000 00C0

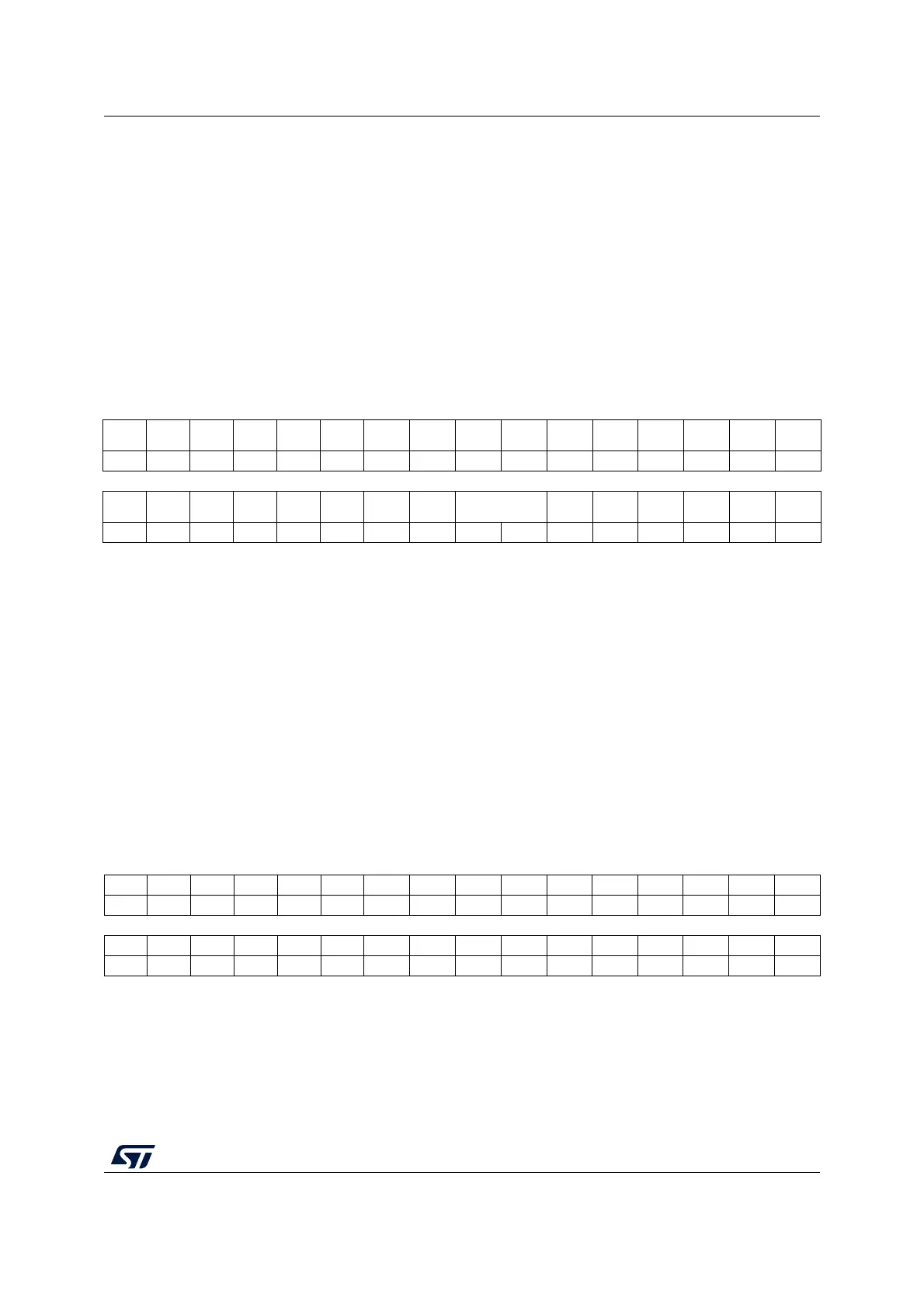

10.4.24 GPIO H output type register (GPIOH_OTYPER)

Address offset: 0x1C04

Reset value: 0x0000 0000

Bit 2 BR2: Port PC2 reset output data bit [2] in GPIOC_ODR

Bit 1 BR1: Port PC1 reset output data bit [1] in GPIOC_ODR

Bit 0 BR0: Port PC0 reset output data bit [0] in GPIOC_ODR

These bits are read clear-write 1. A read to this bit returns the value 0.

0: No action on the corresponding GPIOC_ODR.OD0

1: Resets the corresponding GPIOC_ODR.OD0.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. MODE3[1:0] Res. Res. Res. Res. Res. Res.

rw rw

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:6 MODE3[1:0]: Port PH3 IO type configuration

These bits are written by software to configure the I/O mode.

00: Input mode

01: General purpose output mode

10: Alternate function mode

11: Analog mode (reset state)

Bits 5:0 Reserved, must be kept at reset value.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. OT3 Res. Res. Res.

rw

Loading...

Loading...