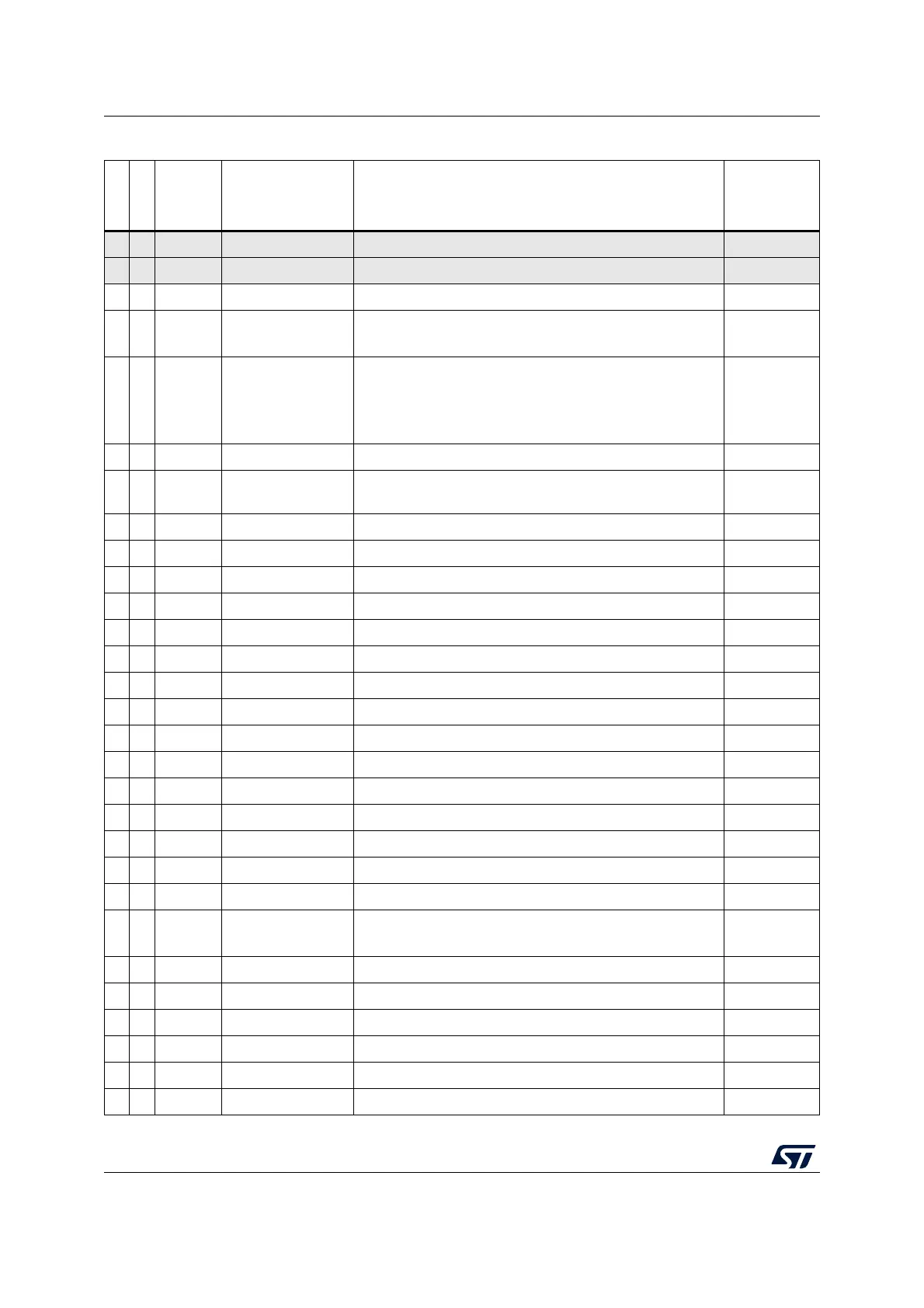

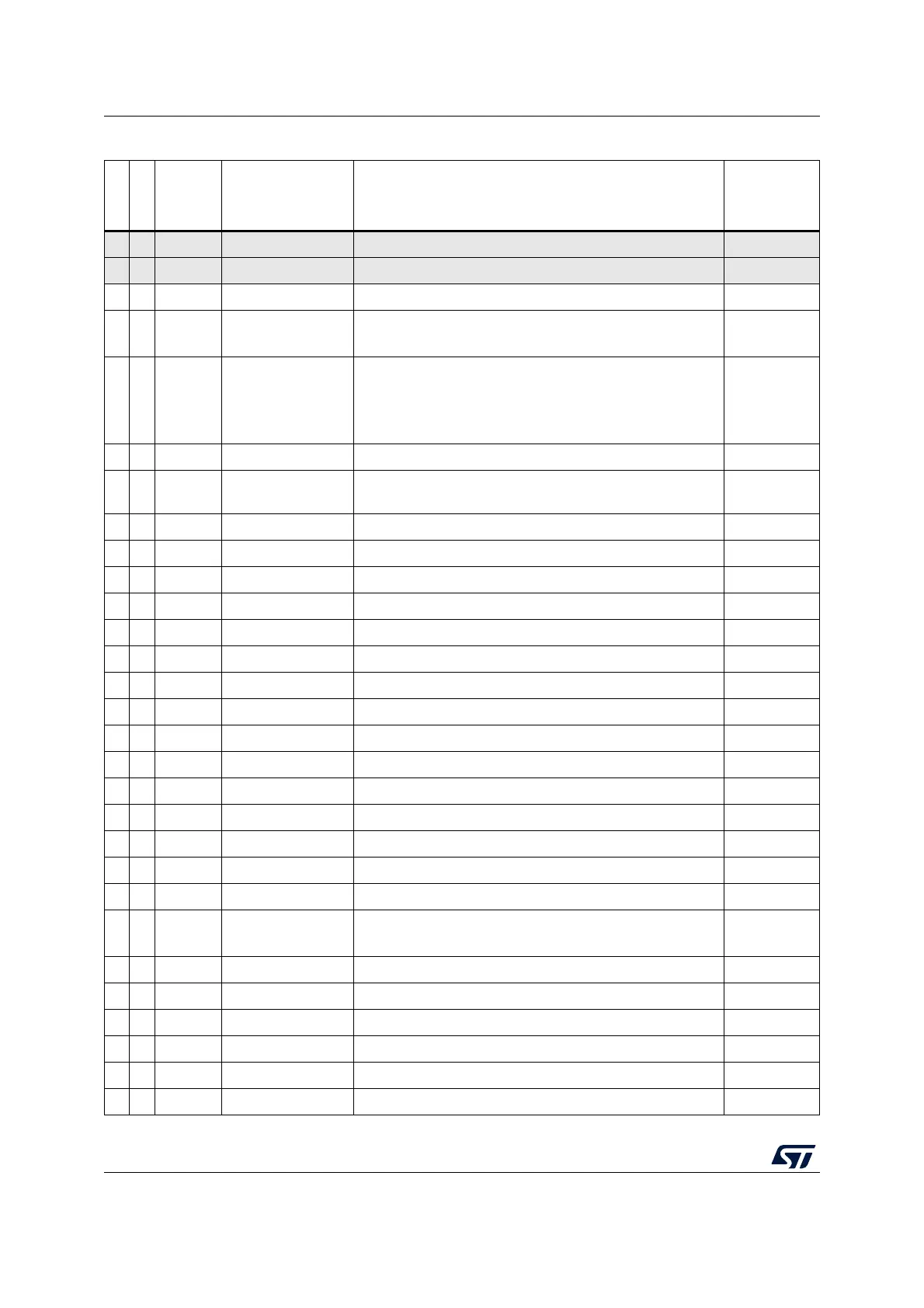

Nested vectored interrupt controller (NVIC) RM0453

500/1454 RM0453 Rev 2

- 5 Settable PendSV Pendable request for system service 0x0000 0038

- 6 Settable SysTick SysTick timer 0x0000 003C

0 7 Settable WWDG Window watchdog early wakeup 0x0000 0040

18Settable

PVD,

PVM[3]

PVD through EXTI[16] (IMR2[20])

PVM[3] through EXTI[34] (IMR2[18])

0x0000 0044

29Settable

TAMP,

RTC_STAMP,

LSE_CSS,

RTC_SSRU

TAMP tamper

RTC timestamp

LSECSS interrupt (IMR1[0])

RTC SSR underflow interrupt (IMR1[2])

0x0000 0048

3 10 Settable RTC_WKUP RTC wakeup interrupt 0x0000 004C

4 11 Settable FLASH

Flash memory global interrupt and Flash memory ECC

single error interrupt

0x0000 0050

5 12 Settable RCC RCC global interrupt 0x0000 0054

6 13 Settable EXTI0 EXTI line 0 interrupt through EXTI[0] 0x0000 0058

7 14 Settable EXTI1 EXTI line 1 interrupt through EXTI[1] 0x0000 005C

8 15 Settable EXTI2 EXTI line 2 interrupt through EXTI[2] 0x0000 0060

9 16 Settable EXTI3 EXTI line 3 interrupt through EXTI[3] 0x0000 0064

10 17 Settable EXTI4 EXTI line 4 interrupt through EXTI[4] 0x0000 0068

11 18 Settable DMA1_CH1 DMA1 channel 1 non-secure interrupt 0x0000 006C

12 19 Settable DMA1_CH2 DMA1 channel 2 non-secure interrupt 0x0000 0070

13 20 Settable DMA1_CH3 DMA1 channel 3 non-secure interrupt 0x0000 0074

14 21 Settable DMA1_CH4 DMA1 channel 4 non-secure interrupt 0x0000 0078

15 22 Settable DMA1_CH5 DMA1 channel 5 non-secure interrupt 0x0000 007C

16 23 Settable DMA1_CH6 DMA1 channel 6 non-secure interrupt 0x0000 0080

17 24 Settable DMA1_CH7 DMA1 channel 7 non-secure interrupt 0x0000 0084

18 25 Settable ADC ADC global interrupt 0x0000 0088

19 26 Settable DAC DAC global interrupt 0x0000 008C

20 27 Settable

C2SEV,

PWR_C2H

CPU2 SEV through EXTI[40]

PWR CPU2 HOLD wakeup interrupt

0x0000 0090

21 28 Settable COMP COMP2 and COMP1 interrupt through EXTI[22:21] 0x0000 0094

22 29 Settable EXTI[9:5] EXTI line [9:5] interrupt through EXTI[9:5] (IMR1[25:21]) 0x0000 0098

23 30 Settable TIM1_BRK Timer 1 break interrupt 0x0000 009C

24 31 Settable TIM1_UP Timer 1 Update 0x0000 00A0

25 32 Settable TIM1_TRG_COM Timer 1 trigger and communication 0x0000 00A4

26 33 Settable TIM1_CC Timer 1 capture compare interrupt 0x0000 00A8

Table 89. CPU1 vector table (continued)

Position

Priority

Type of

priority

Acronym Description

(1)(2)

Address

Loading...

Loading...