RM0453 Rev 2 787/1454

RM0453 Advanced-control timer (TIM1)

822

25.4.3 TIM1 slave mode control register (TIM1_SMCR)

Address offset: 0x08

Reset value: 0x0000 0000

Bit 2 CCUS: Capture/compare control update selection

0: When capture/compare control bits are preloaded (CCPC=1), they are updated by setting

the COMG bit only

1: When capture/compare control bits are preloaded (CCPC=1), they are updated by setting

the COMG bit or when an rising edge occurs on TRGI

Note: This bit acts only on channels that have a complementary output.

Bit 1 Reserved, must be kept at reset value.

Bit 0 CCPC: Capture/compare preloaded control

0: CCxE, CCxNE and OCxM bits are not preloaded

1: CCxE, CCxNE and OCxM bits are preloaded, after having been written, they are updated

only when a commutation event (COM) occurs (COMG bit set or rising edge detected on

TRGI, depending on the CCUS bit).

Note: This bit acts only on channels that have a complementary output.

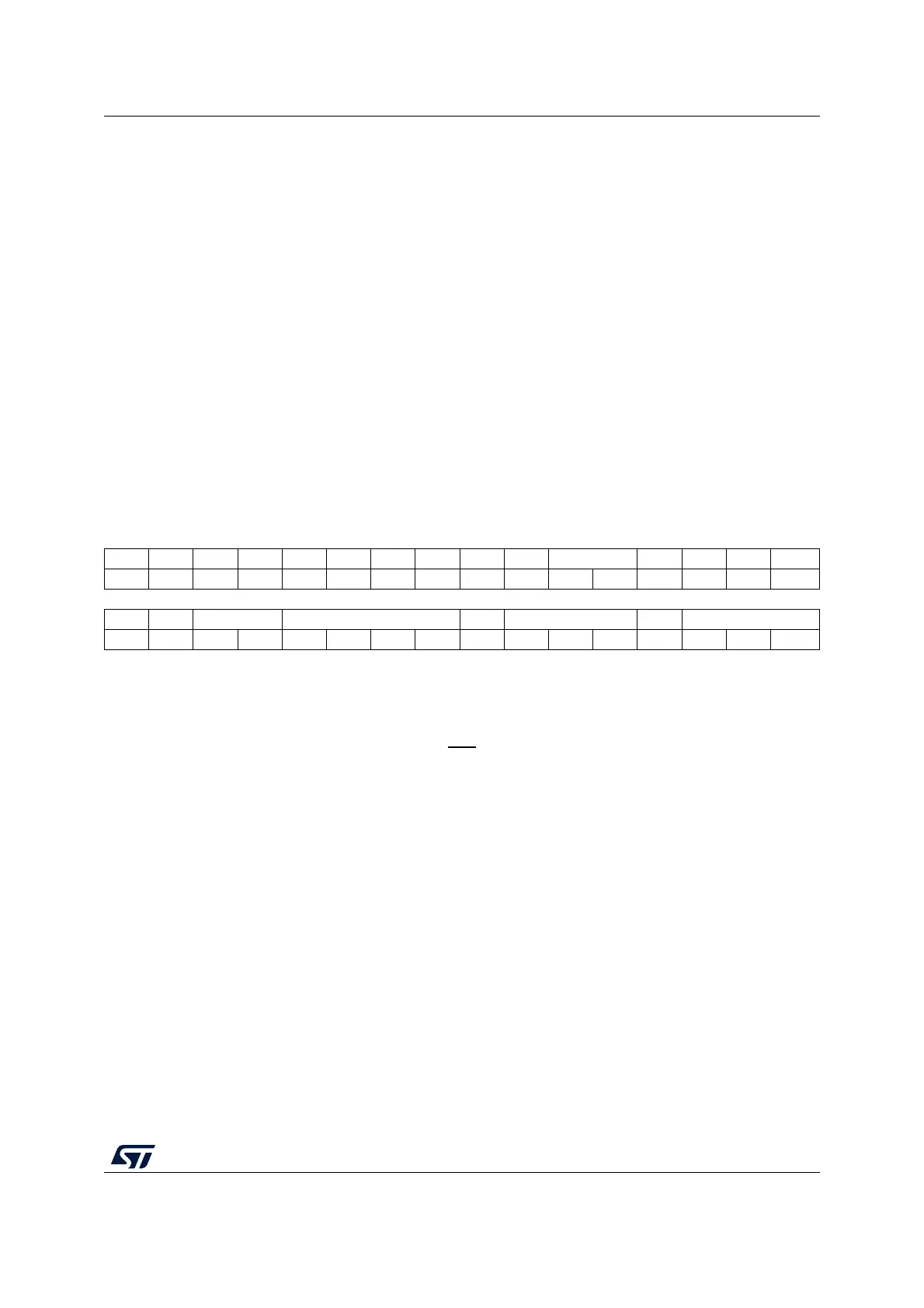

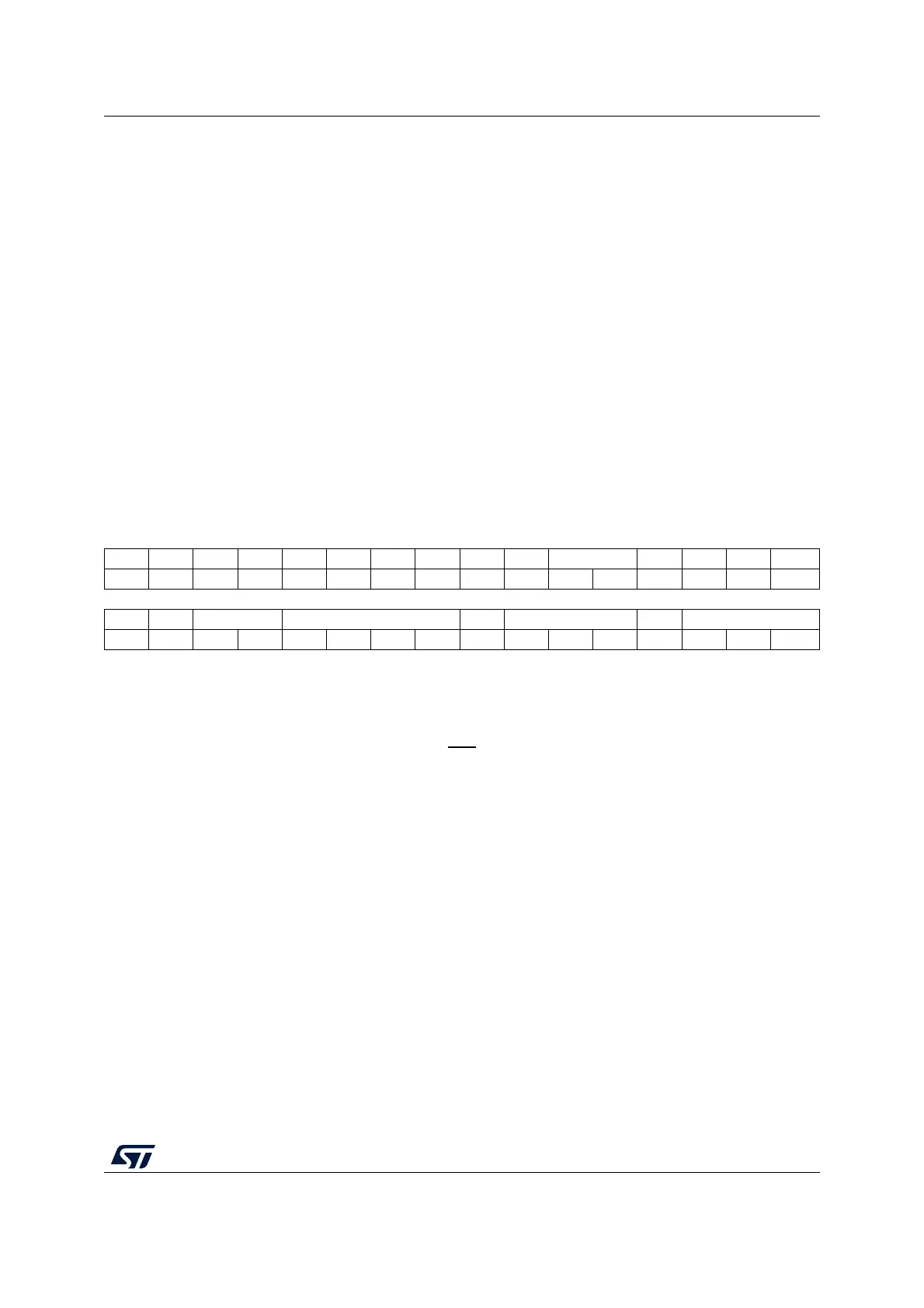

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. TS[4:3] Res. Res. Res. SMS[3]

rw rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

ETP ECE ETPS[1:0] ETF[3:0] MSM TS[2:0] OCCS SMS[2:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:22 Reserved, must be kept at reset value.

Bits 19:17 Reserved, must be kept at reset value.

Bit 15 ETP: External trigger polarity

This bit selects whether ETR or ETR

is used for trigger operations

0: ETR is non-inverted, active at high level or rising edge.

1: ETR is inverted, active at low level or falling edge.

Bit 14 ECE: External clock enable

This bit enables External clock mode 2.

0: External clock mode 2 disabled

1: External clock mode 2 enabled. The counter is clocked by any active edge on the ETRF

signal.

Note: Setting the ECE bit has the same effect as selecting external clock mode 1 with TRGI

connected to ETRF (SMS=111 and TS=00111).

It is possible to simultaneously use external clock mode 2 with the following slave

modes: reset mode, gated mode and trigger mode. Nevertheless, TRGI must not be

connected to ETRF in this case (TS bits must not be 00111).

If external clock mode 1 and external clock mode 2 are enabled at the same time, the

external clock input is ETRF.

Loading...

Loading...