7 Series FPGAs SelectIO Resources User Guide www.xilinx.com 131

UG471 (v1.10) May 8, 2018

OLOGIC Resources

• At time T

ODCK

before Clock Event 1, the output signal becomes valid-high at the D1

input of the output register and is reflected at the OQ output at time T

OCKQ

after

Clock Event 1.

Clock Event 4

At time T

OSRCK

before Clock Event 4, the S/R signal (configured as synchronous reset in

this case) becomes valid-High, resetting the output register and reflected at the OQ output

at time T

RQ

after Clock Event 4.

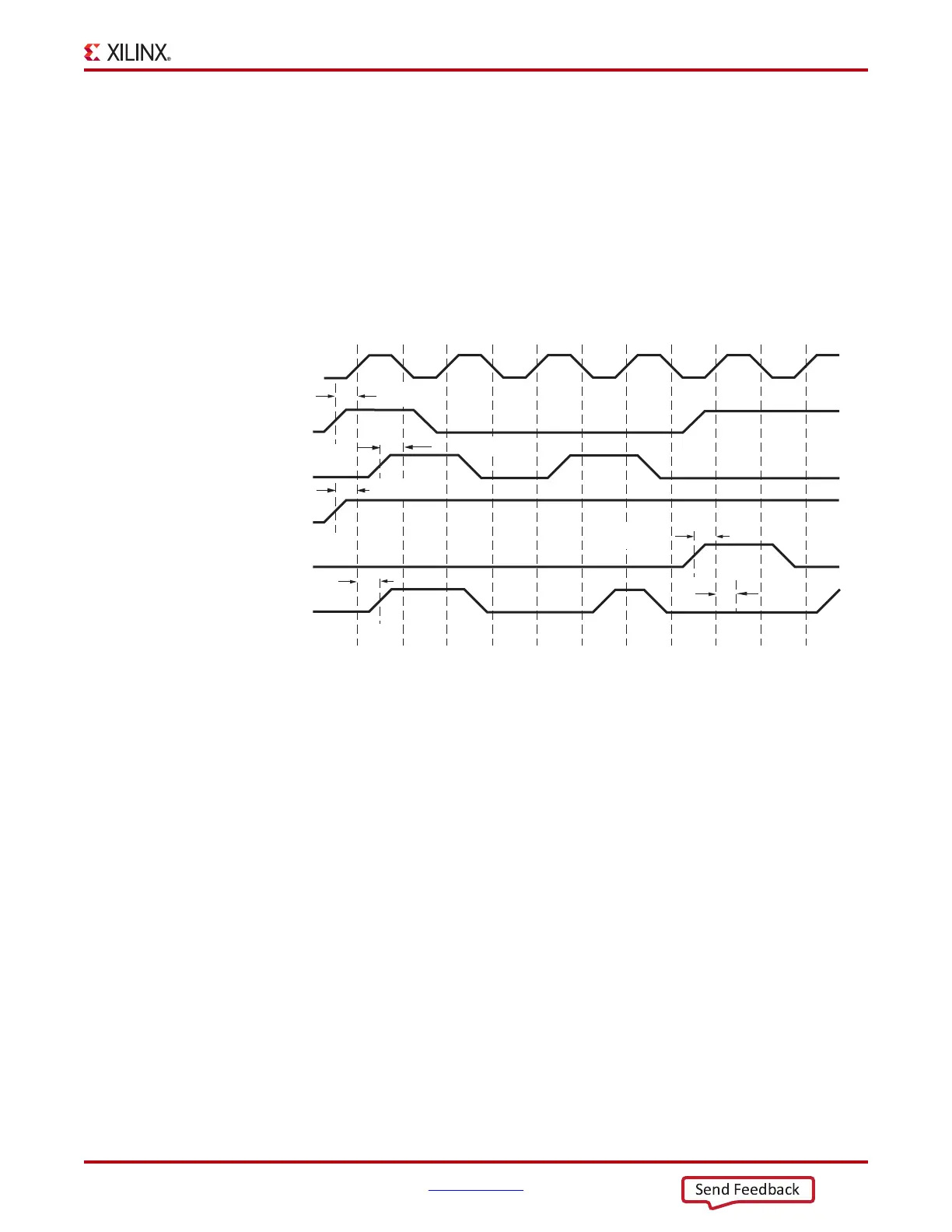

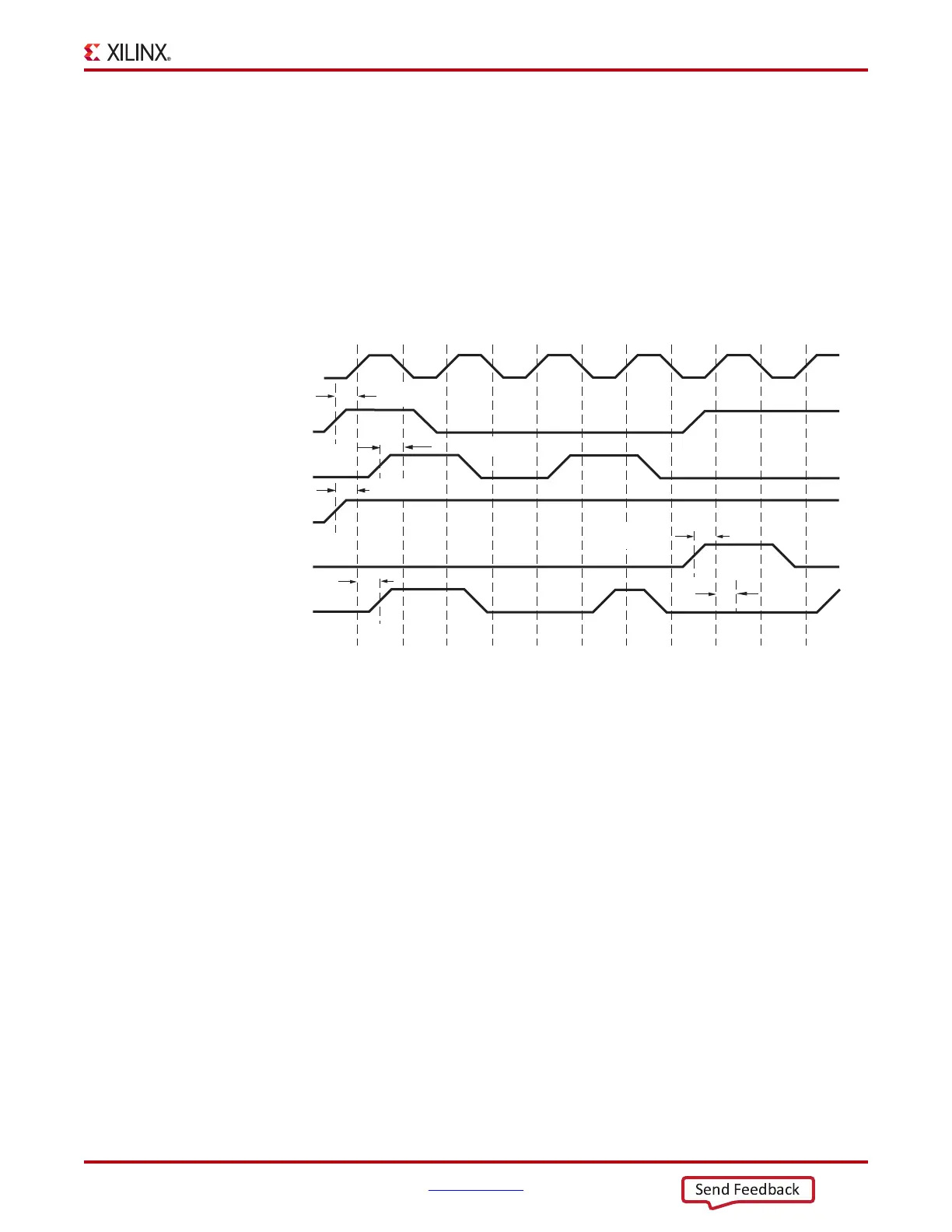

Figure 2-22 illustrates the OLOGIC ODDR register timing.

Clock Event 1

• At time T

OOCECK

before Clock Event 1, the ODDR clock enable signal becomes

valid-High at the OCE input of the ODDR, enabling ODDR for incoming data. Care

must be taken to toggle the OCE signal of the ODDR register between the rising edges

and falling edges of CLK as well as meeting the register setup-time relative to both

clock edges.

•At time T

ODCK

before Clock Event 1 (rising edge of CLK), the data signal D1 becomes

valid-high at the D1 input of ODDR register and is reflected on the OQ output at time

T

OCKQ

after Clock Event 1.

Clock Event 2

•At time T

ODCK

before Clock Event 2 (falling edge of CLK), the data signal D2 becomes

valid-high at the D2 input of ODDR register and is reflected on the OQ output at time

T

OCKQ

after Clock Event 2 (no change at the OQ output in this case).

Clock Event 9

At time T

OSRCK

before Clock Event 9 (rising edge of CLK), the S/R signal (configured as

synchronous reset in this case) becomes valid-high resetting ODDR register, reflected at the

OQ output at time T

RQ

after Clock Event 9 (no change at the OQ output in this case) and

X-Ref Target - Figure 2-2 2

Figure 2-22: OLOGIC ODDR Register Timing Characteristics

(OPPOSITE_EDGE Mode)

123 4567891011

T

ODCK

T

OOCECK

T

ODCK

T

OSRCK

T

RQ

CLK

D1

D2

OCE

S/R

OQ

T

OCKQ

ug471_c2_20_081215

Loading...

Loading...