396

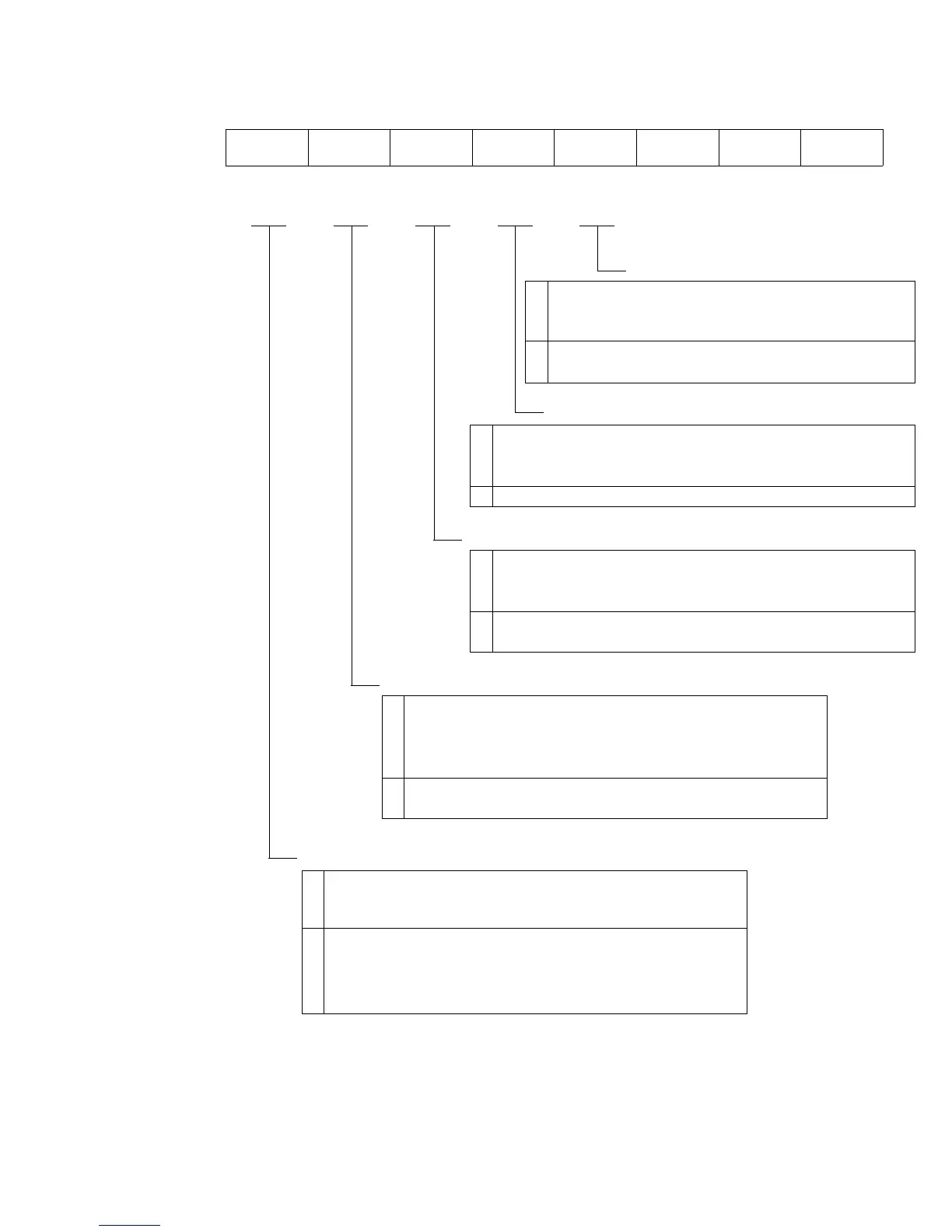

SSR—Serial Status Register H'FFDC SCI

Bit 76543210

TDRE RDRF ORER FER PER — — —

Initial value 10000111

Read/Write R/(W)* R/(W)* R/(W)* R/(W)* R/(W)* ———

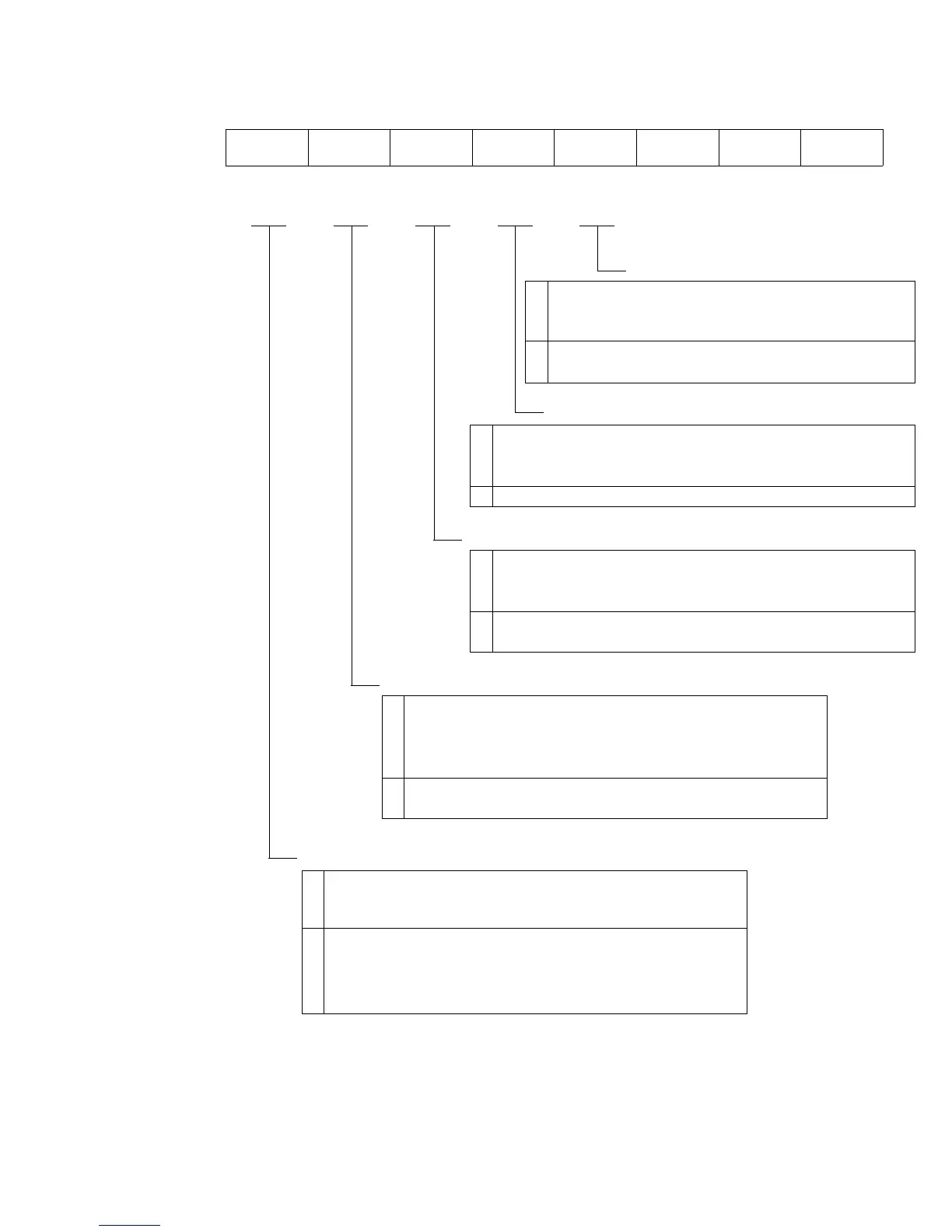

Parity Error

0 Cleared from 1 to 0 when:

1. CPU reads PER = 1, then writes 0 in PER.

2. The chip is reset or enters a standby mode.

1 Set to 1 when a parity error occurs (parity of

receive data does not match parity selected by bit).

Framing Error

0 Cleared from 1 to 0 when:

1. CPU reads FER = 1, then writes 0 in FER.

2. The chip is reset or enters a standby mode.

1 Set to 1 when a framing error occurs (stop bit is 0).

Overrun Error

0 Cleared from 1 to 0 when:

1. CPU reads ORER = 1, then writes 0 in ORER.

2. The chip is reset or enters a standby mode.

1 Set to 1 when an overrun error occurs (next data is

completely received while RDRF bit is set to 1).

Receive Data Register Full

0 Cleared from 1 to 0 when:

1. CPU reads RDRF = 1, then writes 0 in RDRF.

2. RDR is read by the DTC.

3. The chip is reset or enters a standby mode.

1 Set to 1 when one character is received normally and

transferred from RSR to RDR.

* Only writing of 0 to clear the flag is enabled.

Transmit Data Register Empty

0 Cleared from 1 to 0 when:

1. CPU reads TDRE = 1, then writes 0 in TDRE.

2. The DTC writes data in TDR.

1 Set to 1 when:

1. The chip is reset or enters a standby mode.

2. Data is transferred from TDR to TSR.

3. CPU reads TDRE = 0, then clears 0 in TE.

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...