399

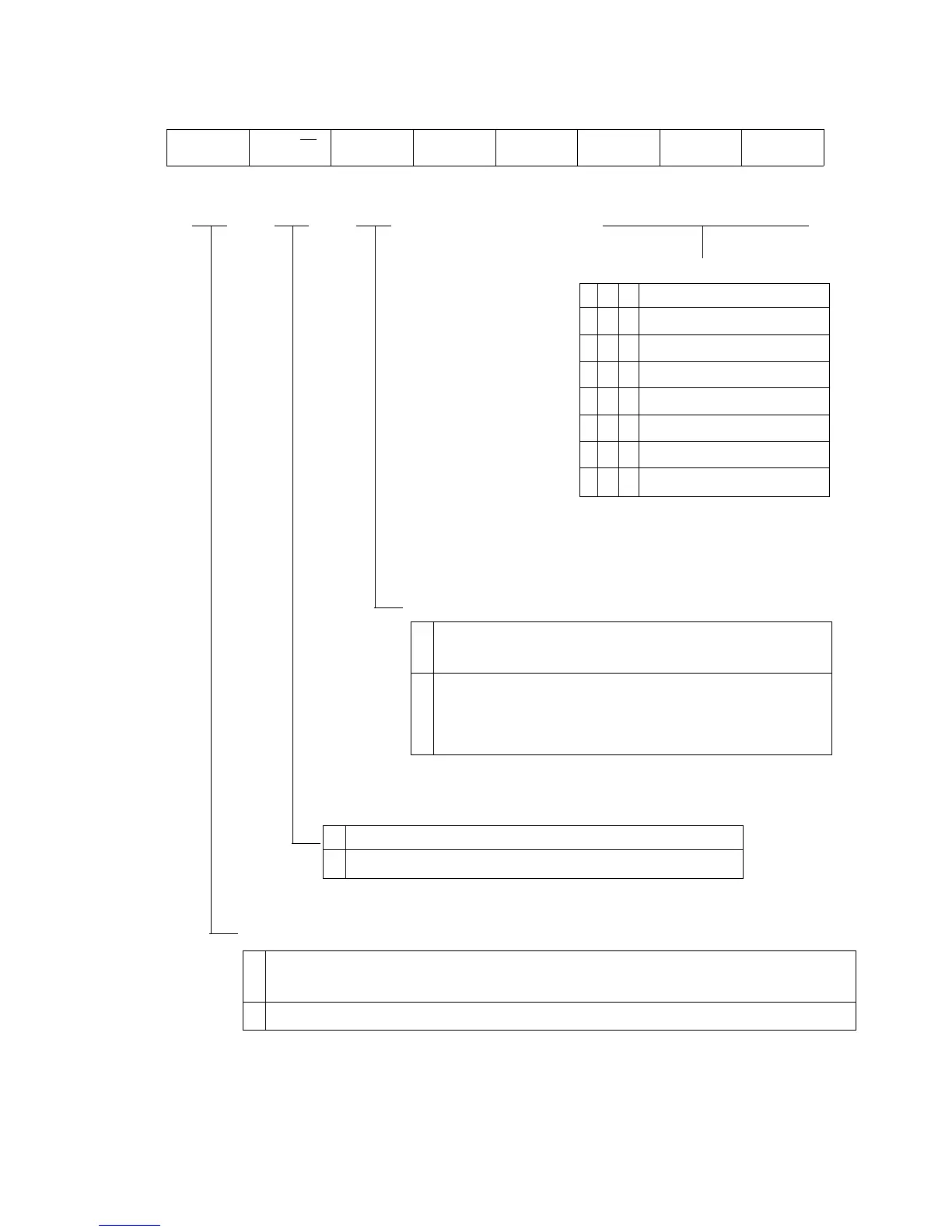

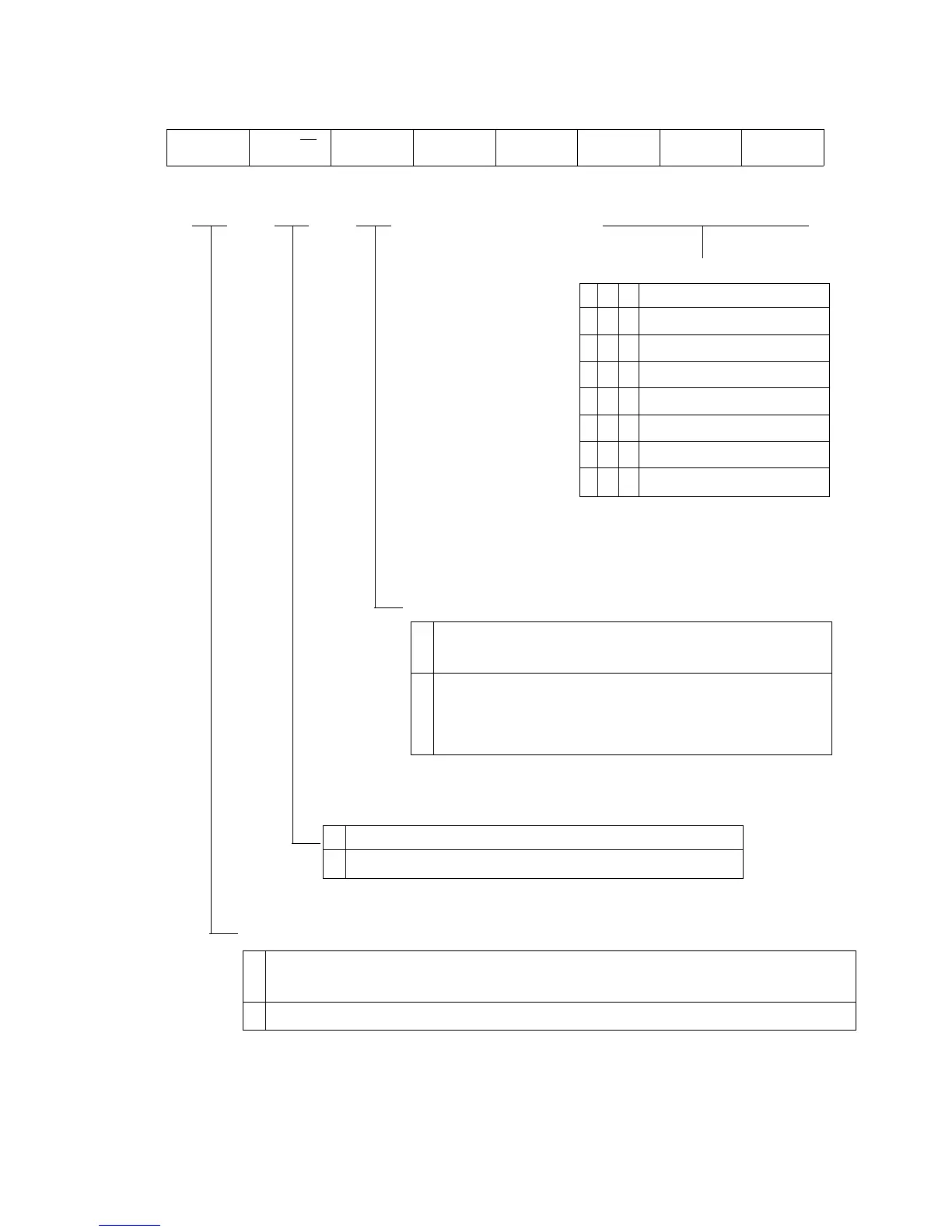

TCSR—Timer Status/Control Register H'FFEC

*1

, H'FFED

*2

WDT

Bit 76543210

OVF WT/IT TME — — CKS2 CKS1 CKS0

Initial value 00011000

Read/Write R/(W)

*3

R/W R/W — — R/W R/W R/W

Timer Enable

0 Timer is disabled.

• TCNT is initialized to H'00 and stopped.

1 Timer is enabled.

• TCNT starts incrementing.

• CPU interrupt request is enabled.

Timer Mode Select

0 Interval timer mode (IRQ0 interrupt request)

1 Watchdog timer mode (NMI interrupt request)

*1 Read address

*2 Write address

*3 Only writing of 0 to clear the flag is enabled.

*4 Times in parentheses are the times for TCNT to increment from H'00 to H'FF and change to

H'00 again when ø = 10MHz.

Overflow Flag

0 Cleared from 1 to 0 when CPU reads OVF = 1, then wtites 0

in OVF.

1 Set to 1 when TCNT changes from H'FF to H'00.

Clock Select

0 0 0 ø/2 (51.2µs)

*4

0 0 1 ø/32 (819.2µs)

0 1 0 ø/64 (1.6ms)

0 1 1 ø/128 (3.3ms)

1 0 0 ø/256 (6.6ms)

1 0 1 ø/512 (13.1ms)

1 1 0 ø/2048 (52.4ms)

1 1 1 ø/4096 (104.9ms)

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...