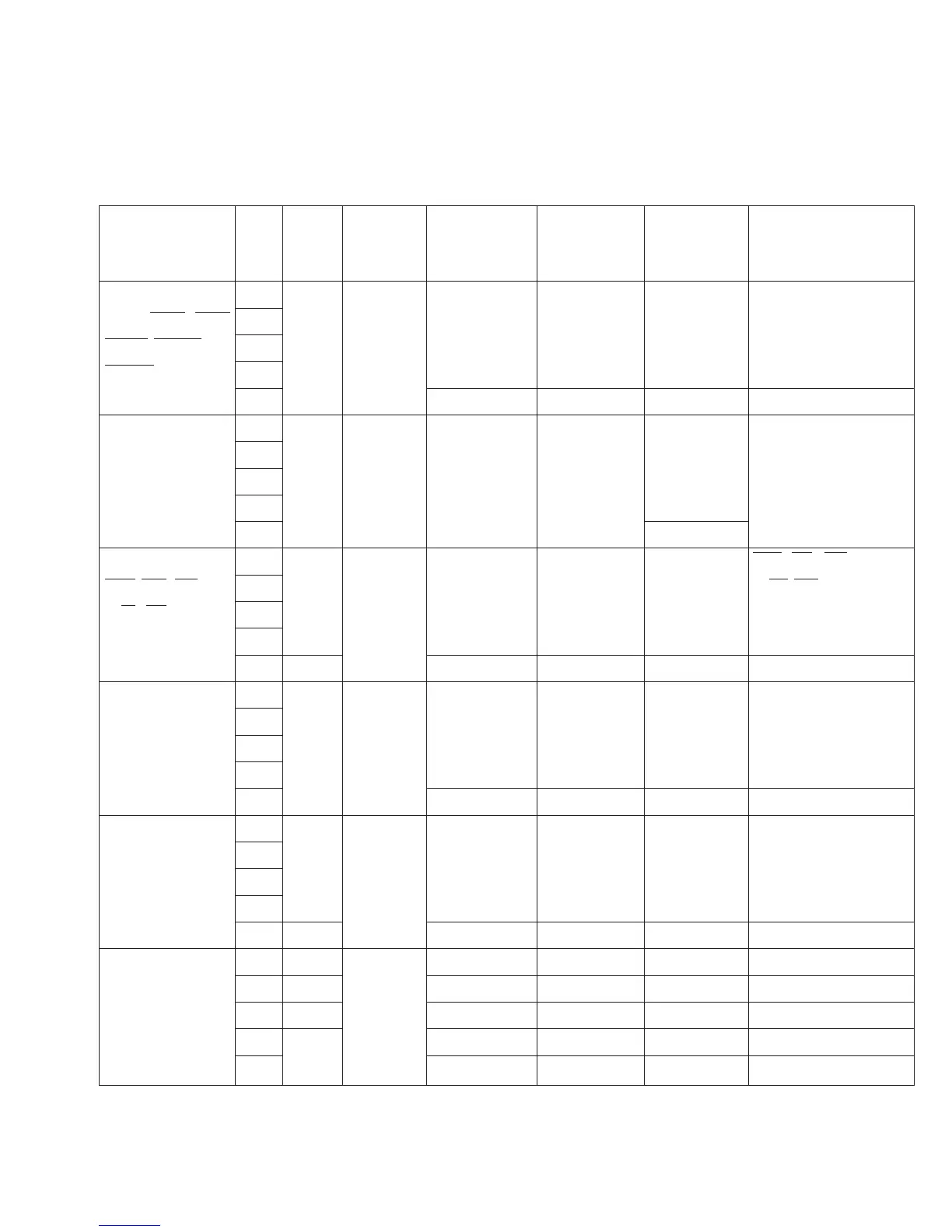

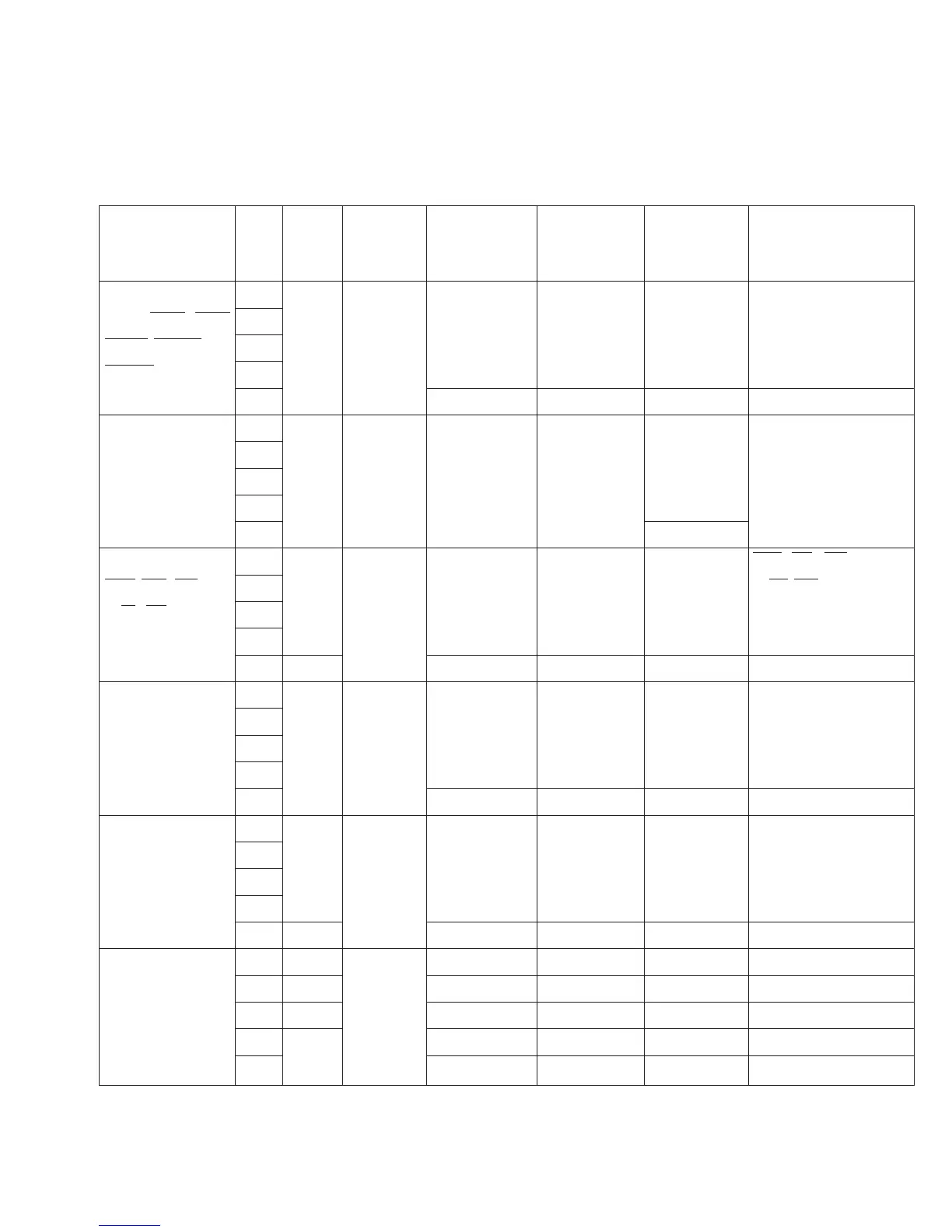

Appendix E Pin State

E.1 Port State of Each Pin State

Table E-1 Port State

Hardware

Port Standby Software Bus-right Program Execution

Pin Name Mode Reset Mode Standby mode Sleep Mode Release Mode

State (Normal Operation)

P17 to P12 1 Input/Output port or

TMO, IRQ1, IRQ0 2 Control signal Input/

WAIT, BREQ, 3 T T keep

*

1

keep

*

3

keep

*

4

Output

BACK 4

7 keep

*

2

keep --- Input/Output port

P11/E 1 (DDR = 1) (DDR = 1) (DDR = 1) (DDR = 1)

P10/ø 2 Clock ø = H Clock output Clock output Clock output

3 output T E = L (DDR = 0) (DDR = 0) (DDR = 0)

4 (DDR = 0) T T Input port

7 T ---

P24 to P20 1 WR, RD, DS,

WR, RD, DS, 2 H T H T R/W, AS

R/W, AS 3

4

7 T keep keep --- Input/Output port

P37 to P30 1

D7 to D0 2 TTTD7 to D0

3T T

4

7 keep keep --- Input/Output port

P47 to P40 1

A7 to A0 2L TLTA7 to A0

3T

4

7 T keep keep --- Input/Output port

P57 to P50 1L T L T' A15 to A8

A15 to A8 2T T

*

6

*

5

T

*

6

Address/Input port

3L T T L T A15 to A8

4T T

*

6

*

5

T

*

6

Address/Input port

7 keep keep --- Input/Output port

431

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...