Section 7: Command reference Model 2651A High Power System SourceMeter® Instrument Reference Manual

7-282 2651A-901-01 Rev. A / March 2011

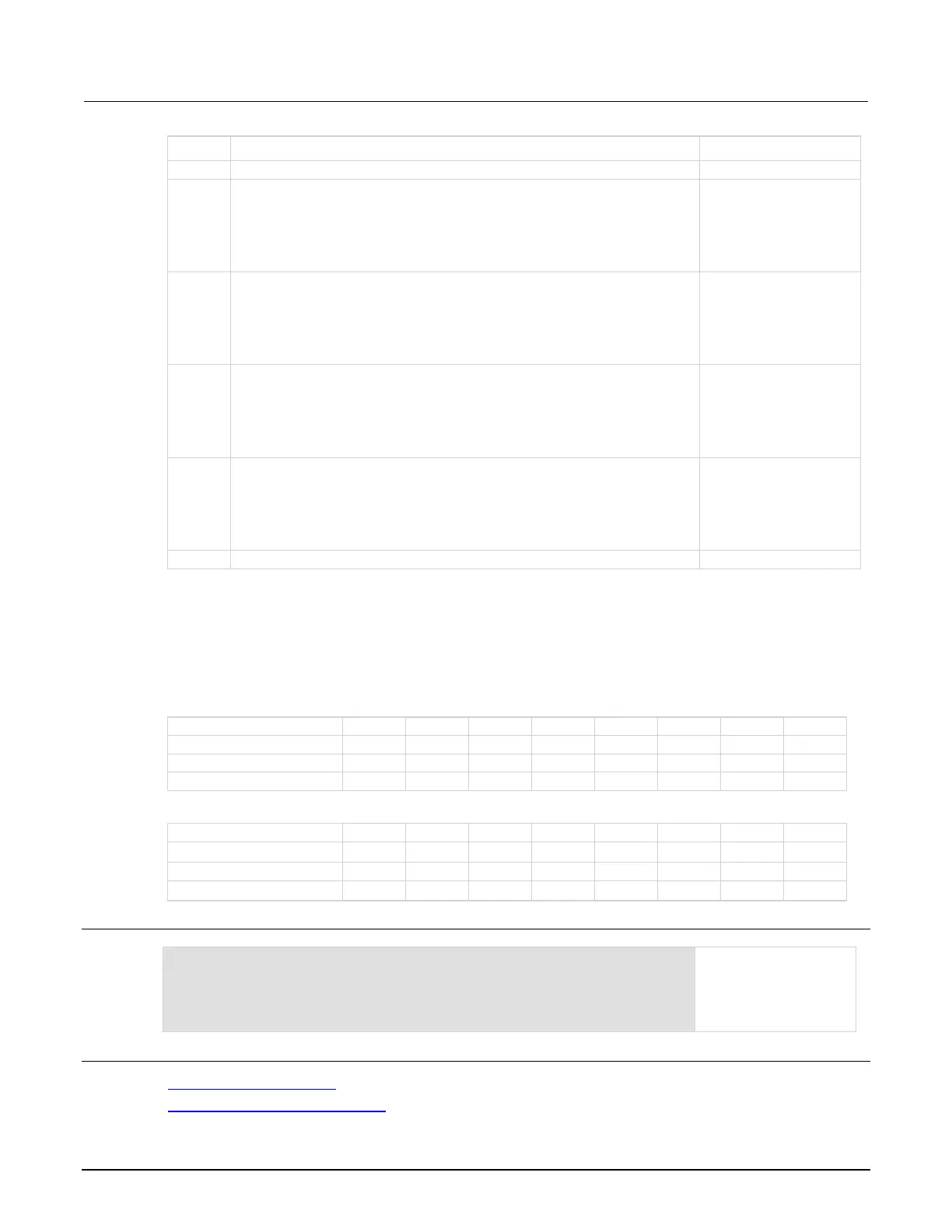

Bit Value Description

B0 Not used Not applicable.

B1

status.operation.instrument.smuX.trigger_overrun.ARM

Set bit indicates that the

arm event detector of the

SMU was already in the

detected state when a

trigger was received.

Bit B1 decimal value: 2

B2

status.operation.instrument.smuX.trigger_overrun.SRC

Set bit indicates that the

source event detector of

the SMU was already in

the detected state when a

trigger was received.

Bit B2 decimal value: 4

B3

status.operation.instrument.smuX.trigger_overrun.MEAS

Set bit indicates that the

measure event detector of

the SMU was already in

the detected state when a

trigger was received.

Bit B3 decimal value: 8

B4

status.operation.instrument.smuX.trigger_overrun.ENDP

Set bit indicates that the

end pulse event detector of

the SMU was already in

the detected state when a

trigger was received.

Bit B4 decimal value: 16

B5-B15 Not used Not applicable.

As an example, to set bit B1 of the operation status SMU A trigger overrun enable register, set

status.operation.instrument.smua.trigger_overrun.enable =

status.operation.instrument.smua.trigger_overrun.ARM.

In addition to the above constants, operationRegister can be set to the numeric equivalent of the bit to set.

To set more than one bit of the register, set operationRegister to the sum of their decimal weights. For

example, to set bits B1 and B4, set operationRegister to 18 (which is the sum of 2 + 16).

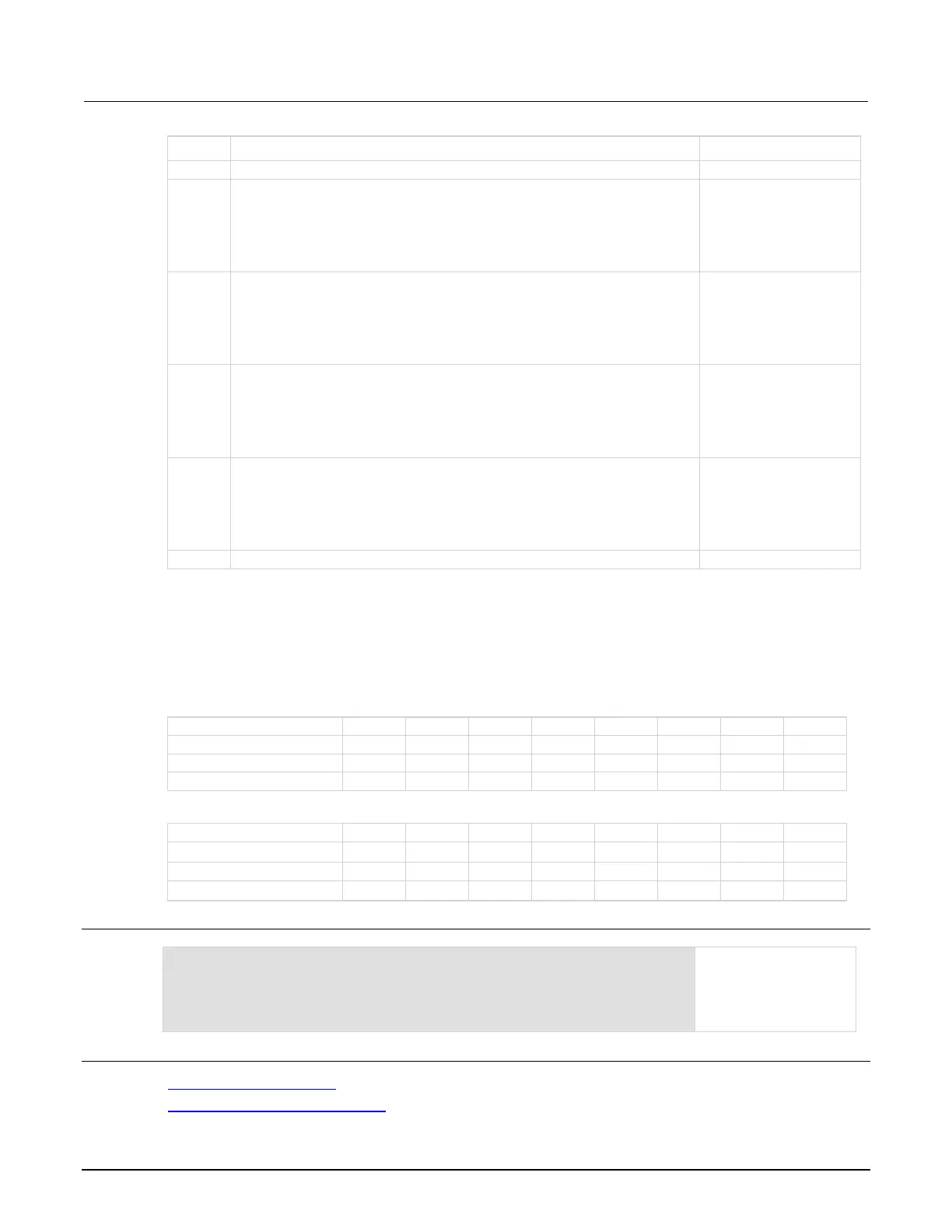

Bit B7 B6 B5 B4 B3 B2 B1 B0

Binary value 0/1 0/1 0/1 0/1 0/1 0/1 0/1 0/1

Decimal 128 64 32 16 8 4 2 1

Weights (2

7

) (2

6

) (2

5

) (2

4

) (2

3

) (2

2

) (2

1

) (2

0

)

Bit B15 B14 B13 B12 B11 B10 B9 B8

Binary value 0/1 0/1 0/1 0/1 0/1 0/1 0/1 0/1

Decimal 32,768 16,384 8,192 4,096 2,048 1024 512 256

Weights (2

15

) (2

14

) (2

13

) (2

12

) (2

11

) (2

10

) (2

9

) (2

8

)

Example

status.operation.instrument.smua.trigger_overrun.enable =

status.operation.instrument.smua.trigger_overrun.ARM

Sets the ARM bit of the

operation status SMU A

trigger overrun enable

register using a

constant.

Also see

Operation Status Registers (on page E-20)

status.operation.instrument.smuX.*

(on page 7-279)

Loading...

Loading...