Because RFL™ and Hubbell® have a policy of continuous product improvement, we reserve the right to change designs and specifications without notice.

RFL DA-91I RFL Electronics Inc.

March 6, 2002 8 (973) 334-3100

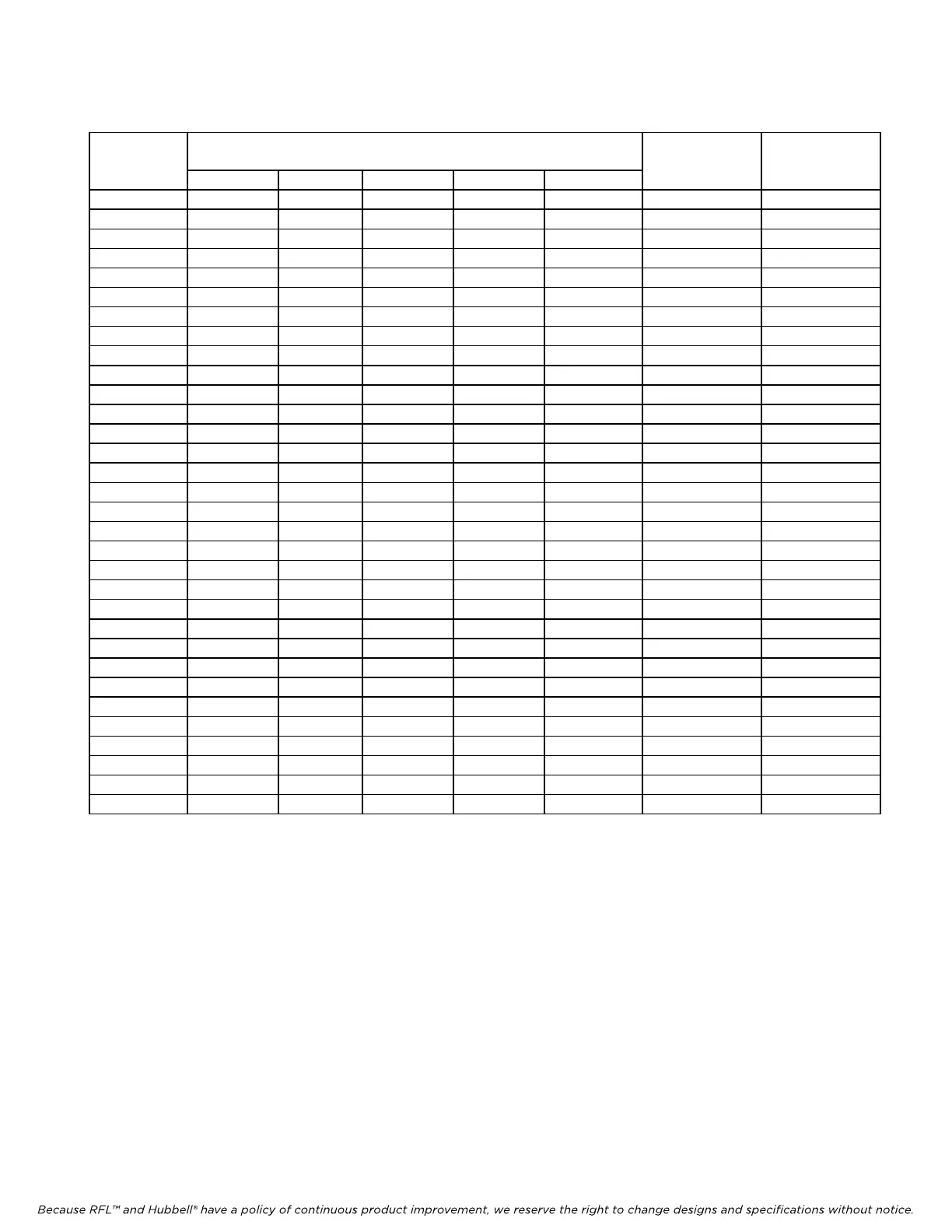

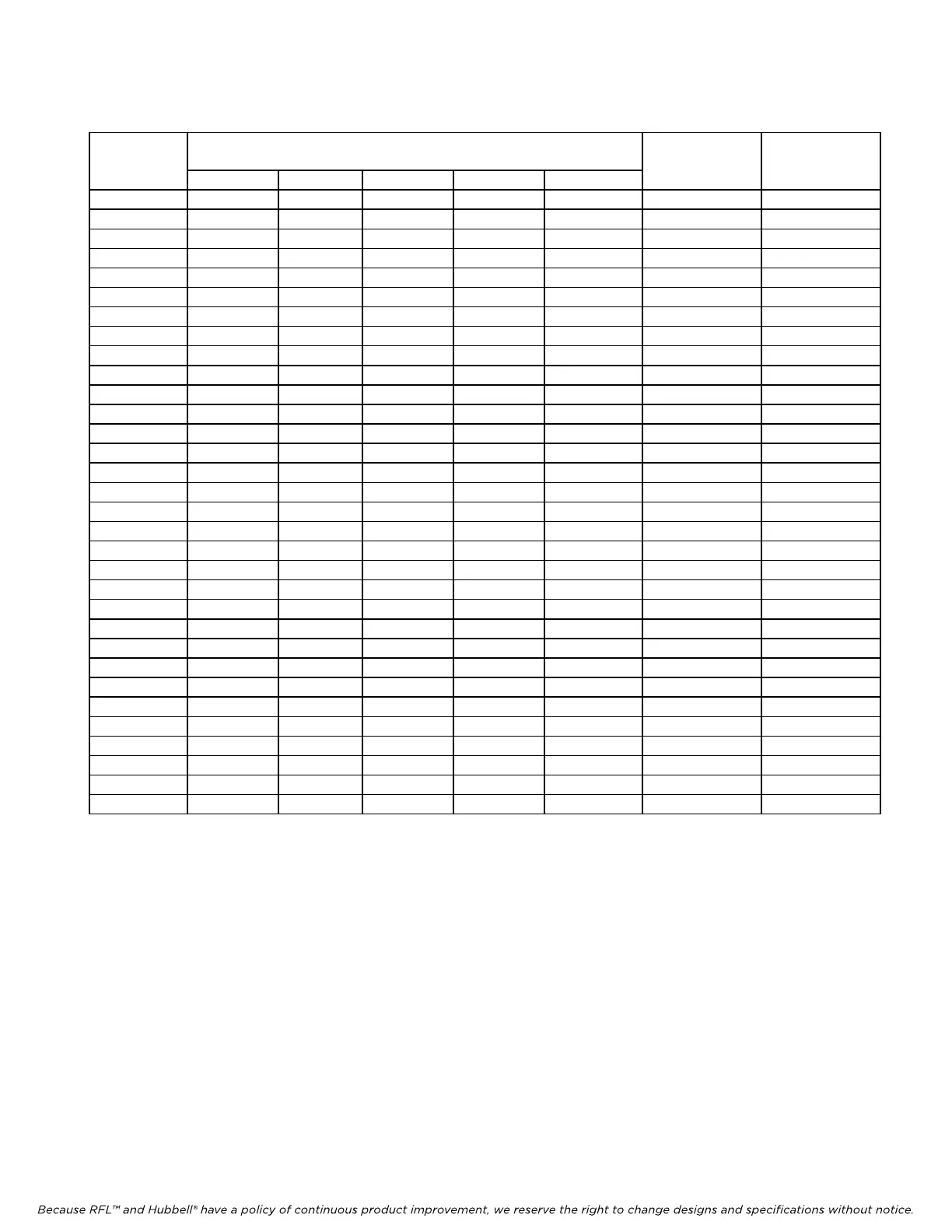

Table 4. Time Slot Select for RFL DA-91I module

Switch Switch Settings T1 E1

Code

(Decimal) SW2-1 SW2-2 SW2-3 SW2-4 SW2-5

0 DOWN DOWN DOWN DOWN DOWN * *

1 DOWN DOWN DOWN DOWN UP 1 1

2 DOWN DOWN DOWN UP DOWN 2 2

3 DOWN DOWN DOWN UP UP 3 3

4 DOWN DOWN UP DOWN DOWN 4 4

5 DOWN DOWN UP DOWN UP 5 5

6 DOWN DOWN UP UP DOWN 6 6

7 DOWN DOWN UP UP UP 7 7

8 DOWN UP DOWN DOWN DOWN 8 8

9 DOWN UP DOWN DOWN UP 9 9

10 DOWN UP DOWN UP DOWN 10 10

11 DOWN UP DOWN UP UP 11 11

12 DOWN UP UP DOWN DOWN 12 12

13 DOWN UP UP DOWN UP 13 13

14 DOWN UP UP UP DOWN 14 14

15 DOWN UP UP UP UP 15 15

16 UP DOWN DOWN DOWN DOWN 16 16****

17 UP DOWN DOWN DOWN UP 17 17

18 UP DOWN DOWN UP DOWN 18 18

19 UP DOWN DOWN UP UP 19 19

20 UP DOWN UP DOWN DOWN 20 20

21 UP DOWN UP DOWN UP 21 21

22 UP DOWN UP UP DOWN 22 22

23 UP DOWN UP UP UP 23 23

24 UP UP DOWN DOWN DOWN 24** 24

25 UP UP DOWN DOWN UP * 25

26 UP UP DOWN UP DOWN * 26

27 UP UP DOWN UP UP * 27

28 UP UP UP DOWN DOWN * 28

29 UP UP UP DOWN UP * 29

30 UP UP UP UP DOWN * 30**

31 UP UP UP UP UP * 31***

Notes: * This setting is not allowed . Setting switches to this code will cause the module’s service to be disabled.

**A T1 or E1 network utilizing fast reframing cannot utilize this time slot for voice channel.

*** An E1 network utilizing inter-node communications (NMX) cannot use timeslot 31 for voice channel.

**** Not

valid if signaling is enabled in E1. Time slot 16 is reserved for CAS.

14. Set DIP switch SW3-5 to enable or disable Time Slot Sharing.

Place SW3-5 to the ON position to enable Time Slot Sharing. The TX data outputs

on the T1 bus are deactivated unless RTS1 or RTS2 or both are active. This setting

allows multiple DA-91I cards to use the same time slot in the same multiplexer

chassis. Only a single RTS signal on any of the cards may be active at one time.

Place SW3-5 to the OFF position to disable Time Slot Sharing. The TX data

outputs on the T1 bus are always active, regardless of RTS1 or RTS2. “IDLE”

data bits are inserted onto the TX data output corresponding to an inactive RTS

signal.

Loading...

Loading...