A

B

C

C

A

B

S

R

Q

A

A

B

B

Y

X

X

Y

A

B

C

A

B

C

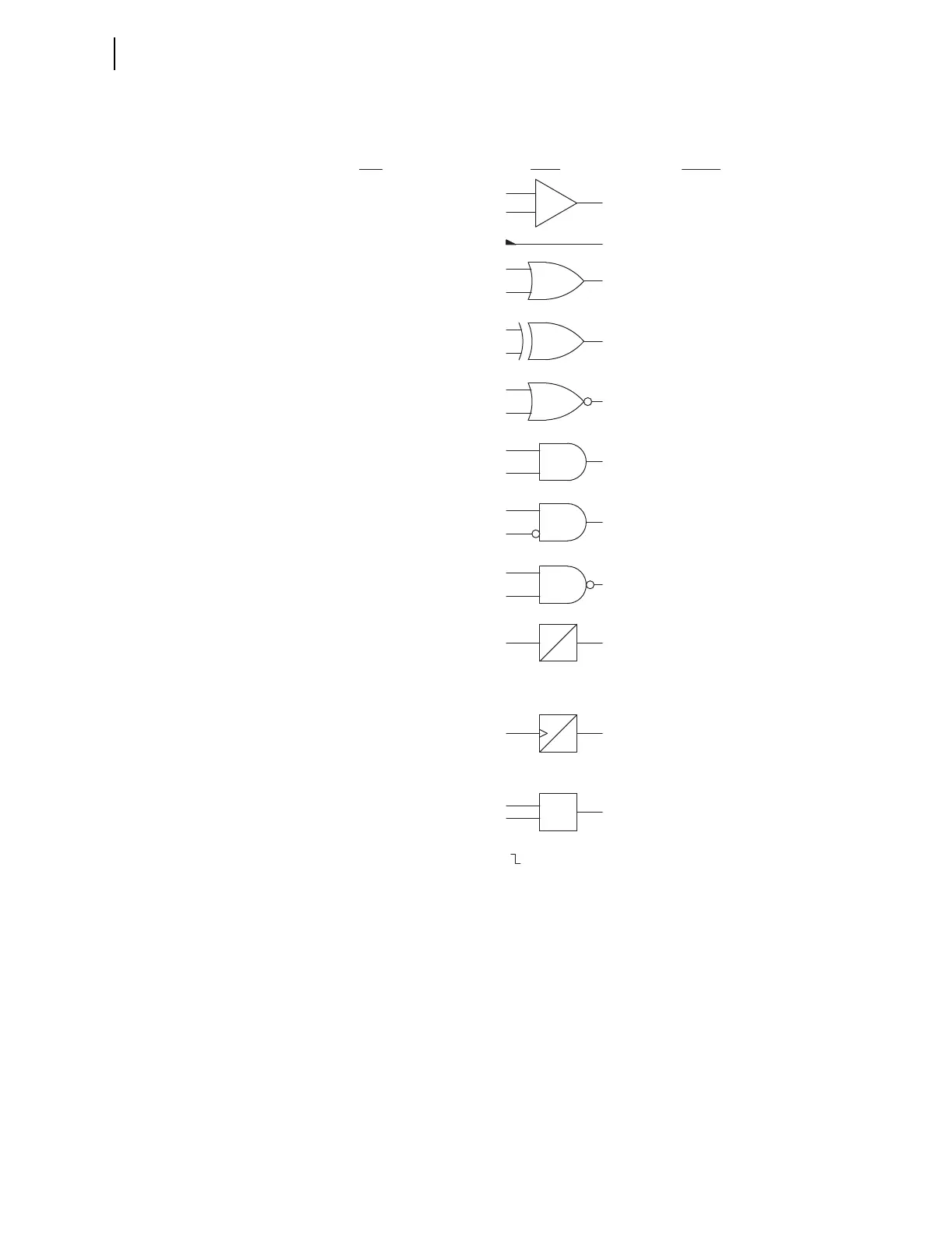

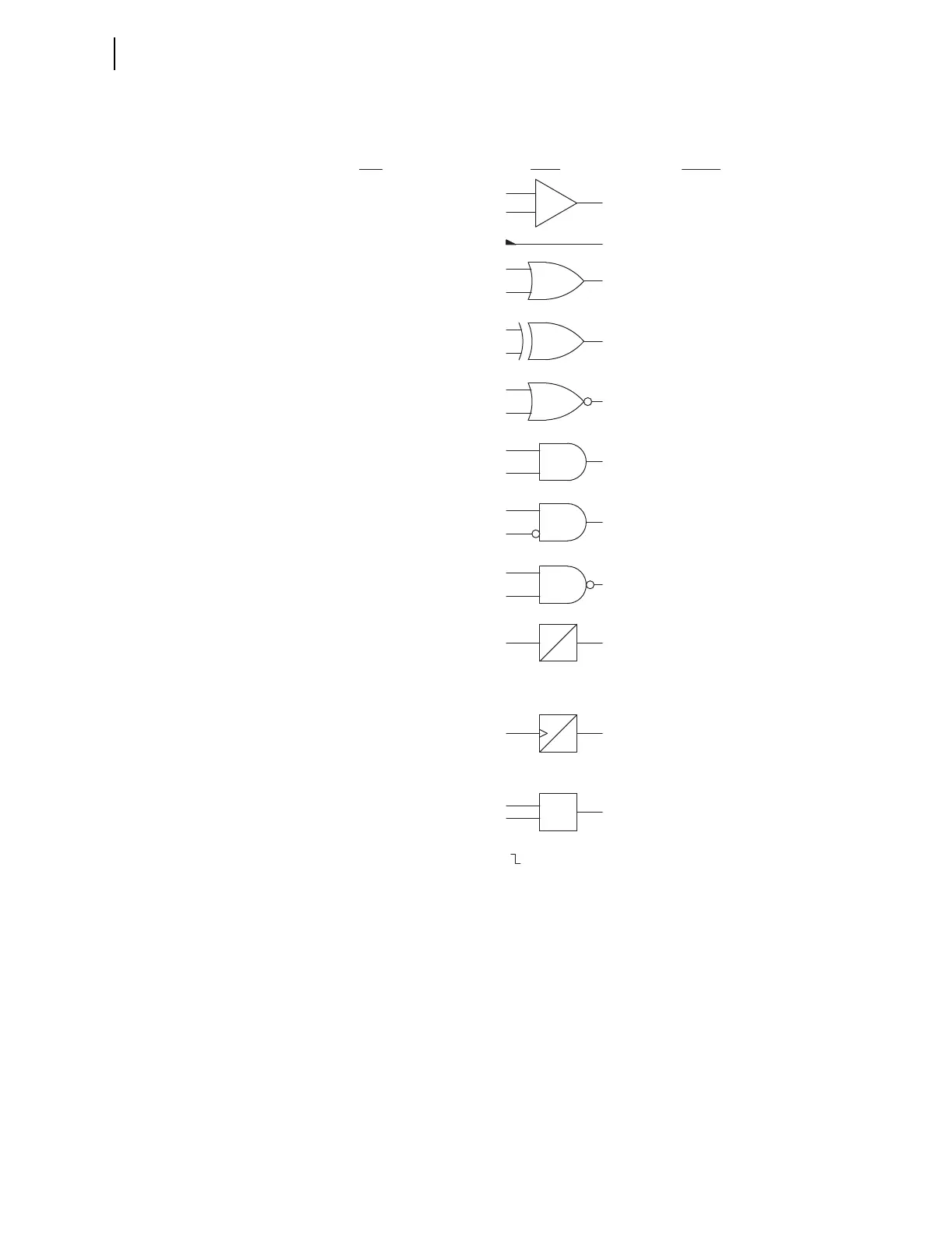

NAME SYMBOL FUNCTION

COMPARATOR

OR

AND

NAND

TIME DELAYED PICK UP AND/OR

TIME DELAYED DROP OUT

EDGE TRIGGER TIMER

SET RESET FLIP FLOP

Input A is compared to input B. Output C

asserts if A is greater than B.

Either input A or input B asserted cause

output C to assert.

Input A and input B must assert to

assert output C.

If A and/or B are deasserted, output C is

asserted.

X is a time-delay-pickup value;

Y is a time-delay-dropout value.

B asserts time X after input A asserts;

B will not assert if A does not remain

asserted for time X. If X is zero, B

will assert when A asserts. If Y is

zero, B will deassert when A deasserts.

Rising edge of A starts timers. Output B

will assert time X after the rising edge of

A. B will remain asserted for time Y. If

Y is zero, B will assert for a single processing

interval. Input A is ignored while the timers

are running.

Input S asserts output Q until input R asserts.

Output Q deasserts or resets when R asserts.

EXCLUSIVE OR

B

A

If either A or B is asserted, output C is

asserted. If A and B are of the same state,

C is deasserted.

C

NOR

B

A

If neither A nor B asserts, output C asserts.

C

AND W/ INVERTED INPUT

B

A

If input A is asserted and input B

is deasserted, output C asserts. Inverter "O"

inverts any input or output on any gate.

C

INPUT FLAG

Input A comes from other logic.

A

—

+

B asserts at the falling edge of input A.

FALLING EDGE

A

B

Loading...

Loading...