R.7.19

Date Code 20111215 Reference Manual SEL-421 Relay

Synchrophasors

Synchrophasor Relay Word Bits

Synchrophasor Relay Word Bits

Tab le 7.9 and Tab le 7.10 list the SEL-421 Relay Word bits that are related to

synchrophasor measurement.

The Synchrophasor Trigger Relay Word bits in Table 7.9 follow the state of

the SEL

OGIC control equations of the same name, listed at the bottom of

Tab le 7.1. These Relay Word bits are included in the IEEE C37.118

synchrophasor data frame STAT field. See Table 7.7 for standard definitions

for these settings.

The Time Synchronization Relay Word bits in Table 7.10 indicate the present

status of the high-accuracy timekeeping function of the SEL-421. See

Configuring High-Accuracy Timekeeping on page U.4.71.

When using the relay as a synchrophasor client, the Relay Word bits in

Tab le 7.11 indicate the state of the synchronization.

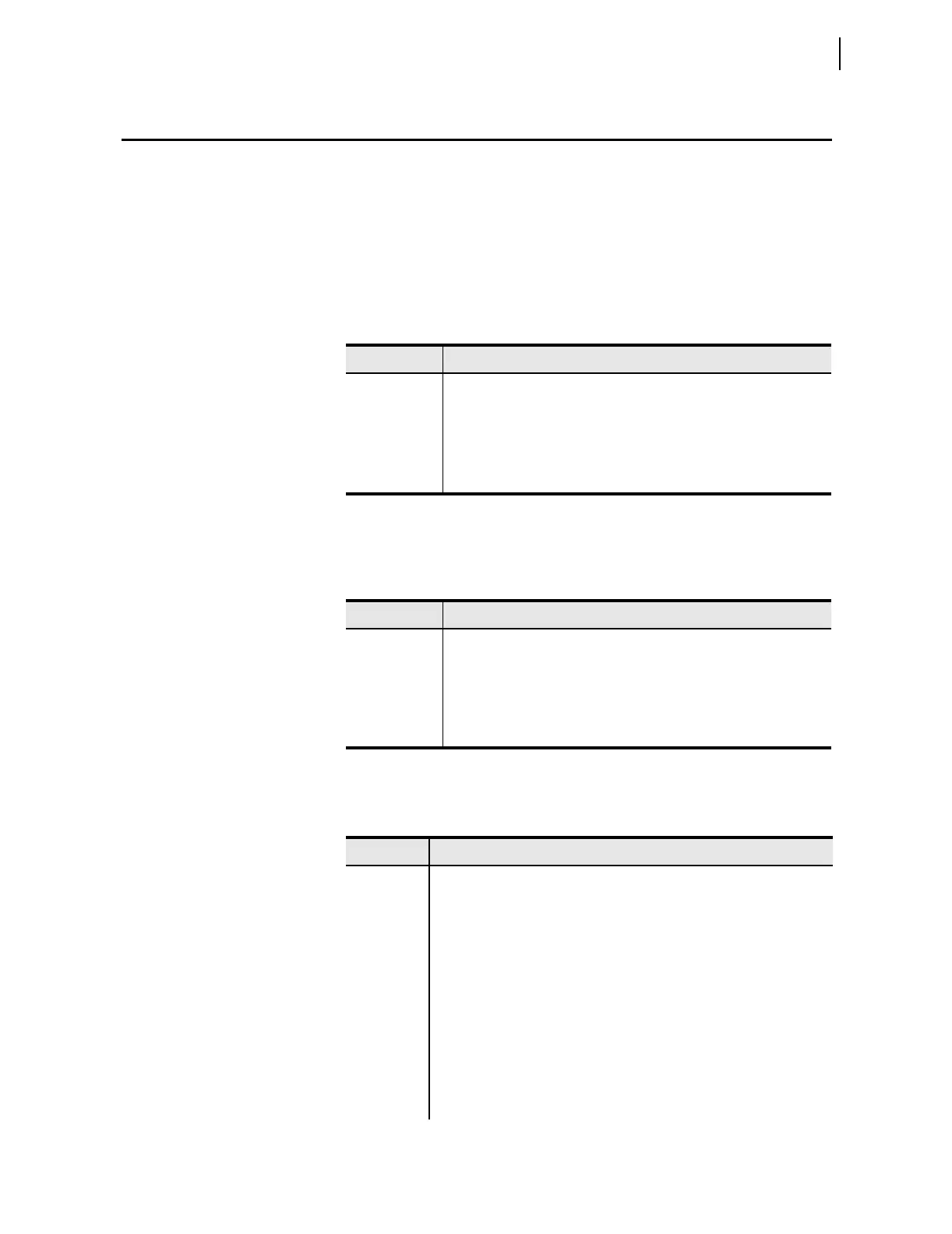

Table 7.9 Synchrophasor Trigger Relay Word Bits

Name Description

PMTRIG Trigger (SELOGIC Equation).

TREA4 Trigger Reason Bit 4 (SELOGIC Equation)

TREA3 Trigger Reason Bit 3 (SEL

OGIC Equation)

TREA2 Trigger Reason Bit 2 (SEL

OGIC Equation)

TREA1 Trigger Reason Bit 1 (SEL

OGIC Equation)

Table 7.10 Time Synchronization Relay Word Bits

Name Description

TIRIG Asserts while relay time is based on IRIG-B time source.

TSOK Time Synchronization OK. Asserts while time is based on high-accu-

racy IRIG-B time source (HIRIG mode) of sufficient accuracy for syn-

chrophasor measurement.

PMDOK Phasor Measurement Data OK. Asserts when the SEL-421 is enabled

and synchrophasors are enabled (Global setting EPMU := Y).

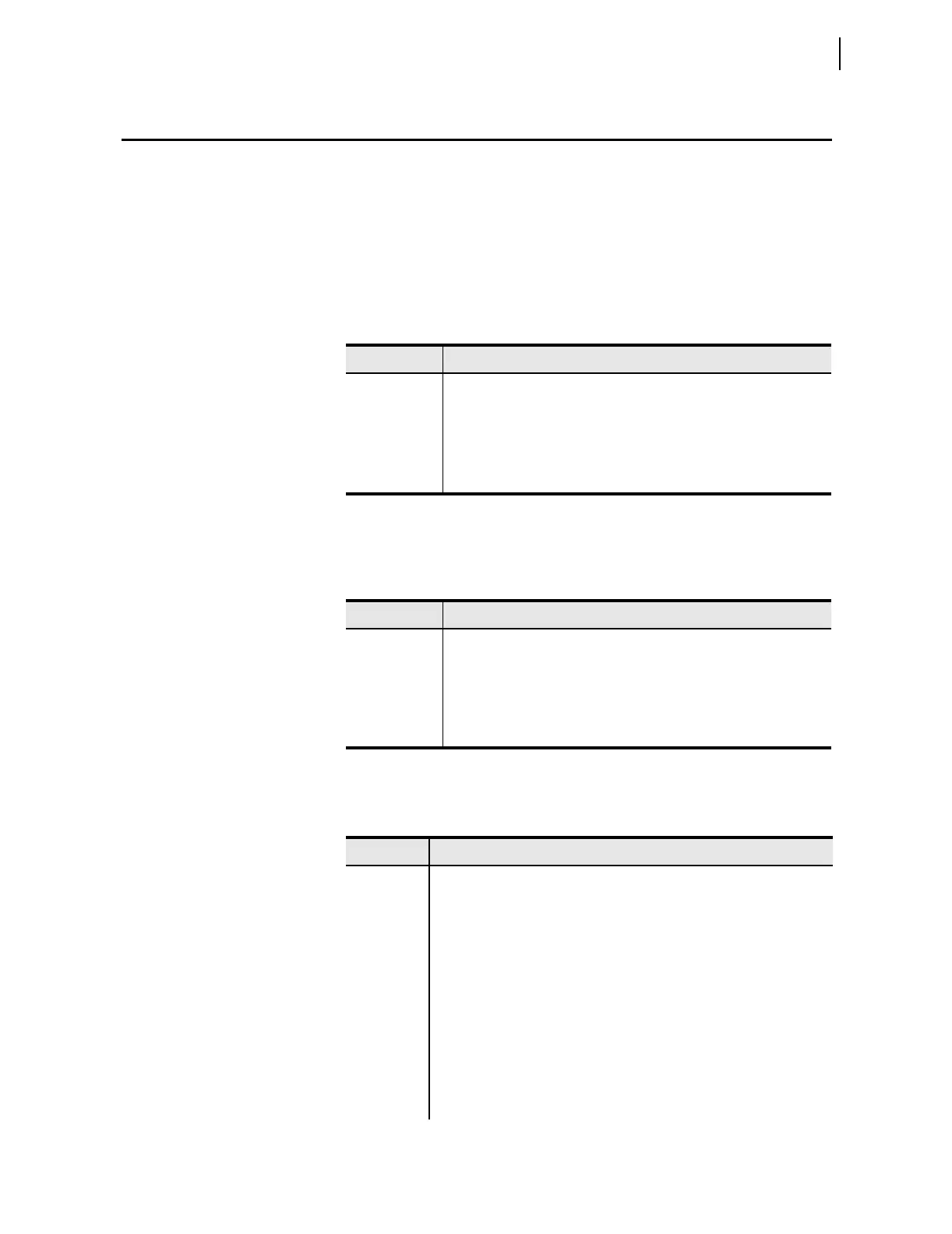

Table 7.11 Synchrophasor Client Status Bits (Sheet 1 of 2)

Name Description

RTCENA Asserts for one processing interval when a valid message is received on

channel A

RTCENB Asserts for one processing interval when a valid message is received on

channel B

RTCROKA Asserts for one processing interval when data is aligned for channel A.

Use this bit to condition usage of the channel A data.

RTCROKB Asserts for one processing interval when data is aligned for channel B.

Use this bit to condition usage of the channel B data.

RTCROK Asserts for one processing interval when data for all enabled channels are

aligned. Use this bit to condition general usage of the aligned synchropha-

sor data.

RTCDLYA This bit is asserted when the last received valid message on channel A is

older than MRTCDLY.

Loading...

Loading...