RM0453 Rev 2 1345/1454

RM0453 Debug support (DBG)

1441

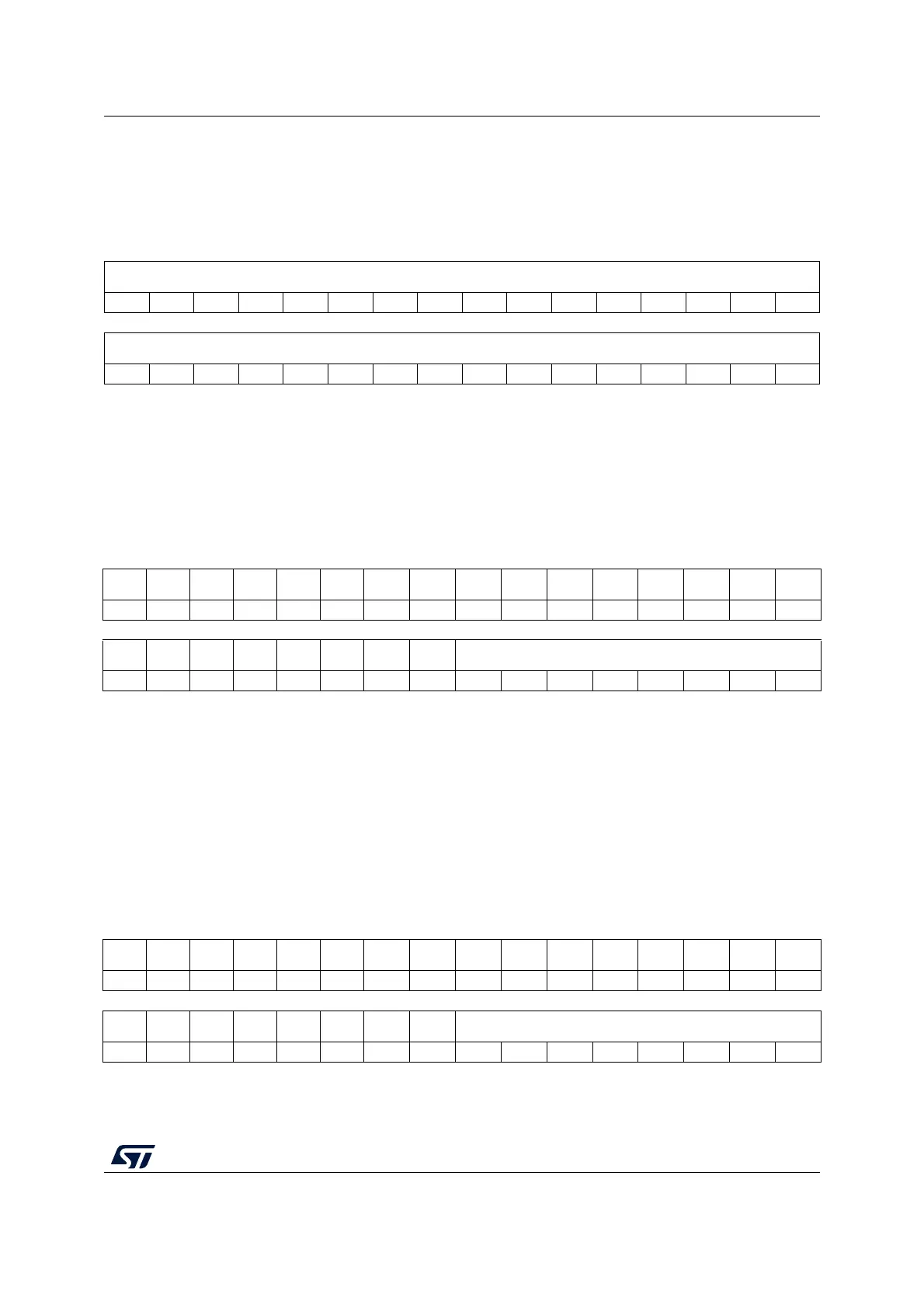

38.6.2 DWT cycle count register (DWT_CYCCNTR)

Address offset: 0x004

Reset value: 0x0000 0000

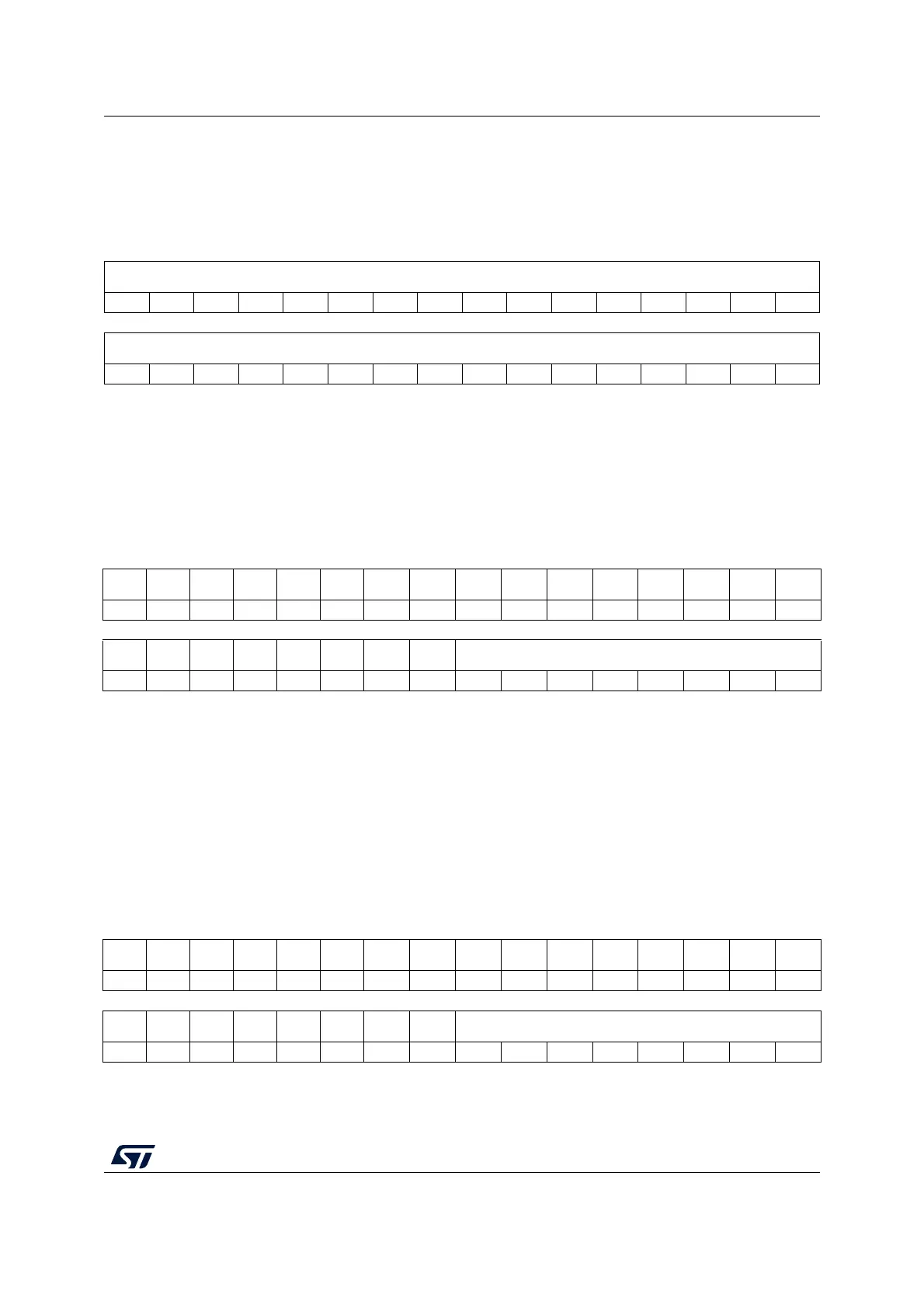

38.6.3 DWT CPI count register (DWT_CPICNTR)

Address offset: 0x008

Reset value: 0x0000 0000

38.6.4 DWT exception count register (DWT_EXCCNTR)

Address offset: 0x00C

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

CYCCNT[31:16]

rrrrrrrrrrrrrrrr

1514131211109876543210

CYCCNT[15:0]

rrrrrrrrrrrrrrrr

Bits 31:0 CYCCNT[31:0]: processor clock cycle counter

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. CPICNT[7:0]

rw rw rw rw rw rw rw rw

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0 CPICNT[7:0]: CPI counter

Counts additional cycles required to execute multi-cycle instructions (except those recorded

by DWT_LSUCNTR) and counts any instruction fetch stalls.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. EXCCNT[7:0]

rw rw rw rw rw rw rw rw

Loading...

Loading...