Debug support (DBG) RM0453

1346/1454 RM0453 Rev 2

38.6.5 DWT sleep count register (DWT_SLPCNTR)

Address offset: 0x010

Reset value: 0x0000 0000

38.6.6 DWT LSU count register (DWT_LSUCNTR)

Address offset: 0x014

Reset value: 0x0000 0000

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0 EXCCNT[7:0]: exception overhead cycle counter

Counts the number of cycles spent in exception processing.

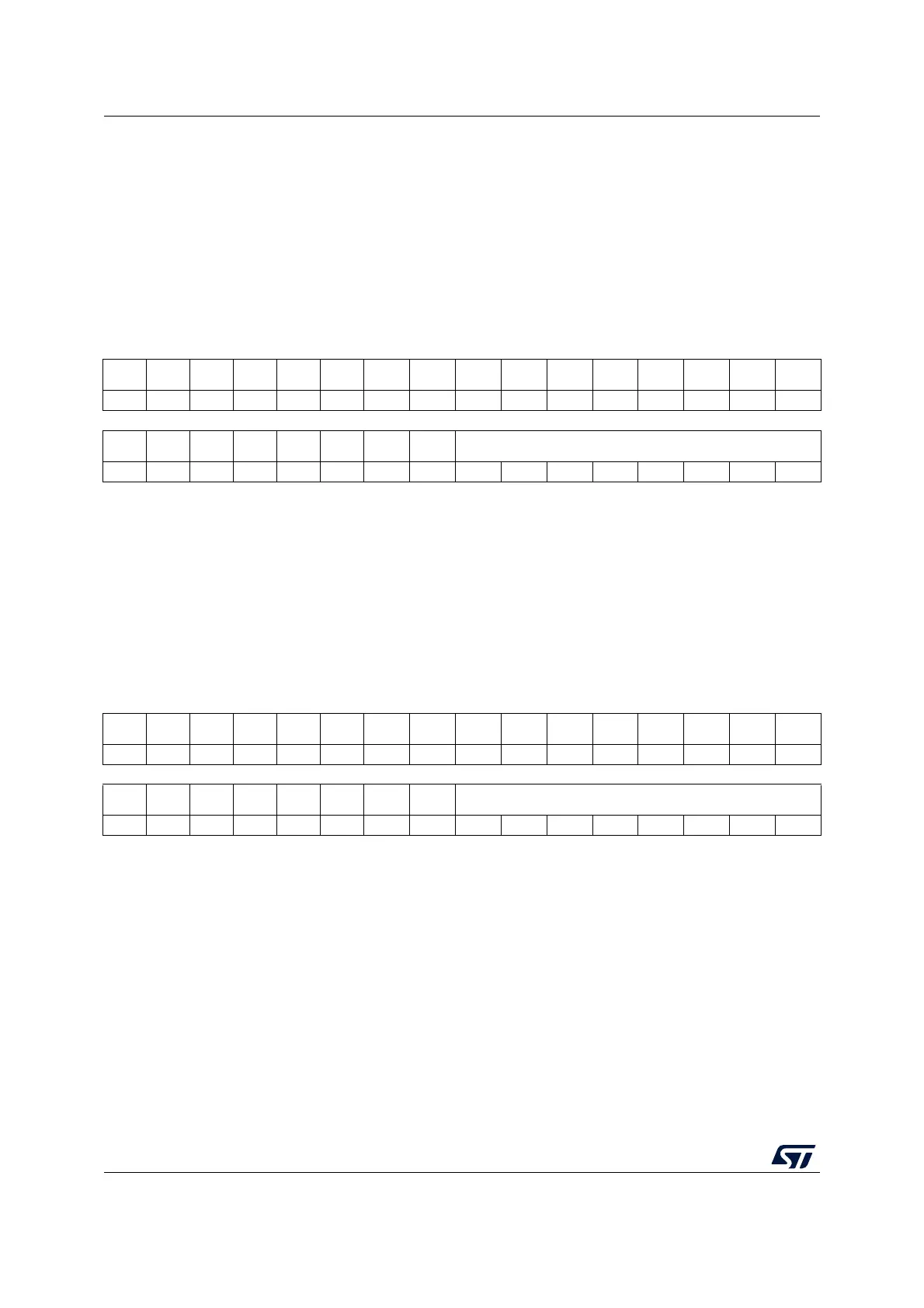

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. SLEEPCNT[7:0]

rw rw rw rw rw rw rw rw

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0 SLEEPCNT[7:0]: sleep cycle counter

Counts the number of cycles spent in sleep mode (WFI, WFE, sleep-on-exit).

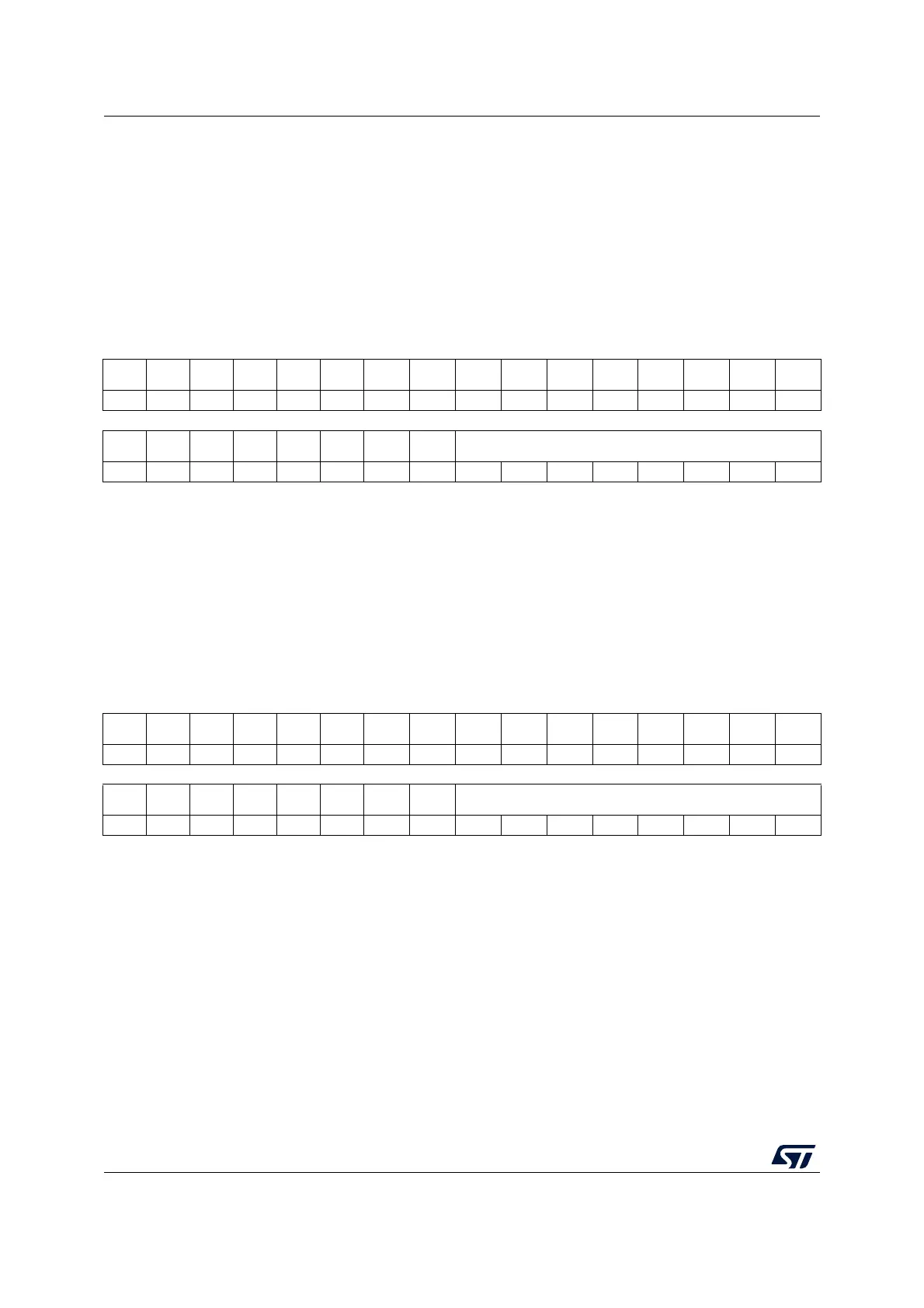

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. LSUCNT[7:0]

rw rw rw rw rw rw rw rw

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0 LSUCNT[7:0]: load store counter

Counts additional cycles required to execute load and store instructions.

Loading...

Loading...