Debug support (DBG) RM0453

1414/1454 RM0453 Rev 2

38.12.3 DBGMCU CPU1 APB1 peripheral freeze register 1

(DBGMCU_APB1FZR1)

Address offset: 0x03C

Reset value: 0x0000 0000

Bits 31:3 Reserved, must be kept at reset value.

Bit 2 DBG_STANDBY: Allows debug in Standby mode

This bit does not influence CPU2 operation, CPU2 cannot be debugged in Standby mode

even when this bit is enabled.

0: Normal operation. All clocks are disabled and the domain powered down automatically in

Standby mode.

1: Automatic clock stop/power down disabled. All active clocks and oscillators continue to run

during Standby mode and the domain supply is maintained, allowing full debug capability. On

exit from Standby mode, a domain reset is performed.

Bit 1 DBG_STOP: Allows debug in Stop mode

This bit does not influence CPU2 operation, CPU2 cannot be debugged in Stop mode even

when this bit is enabled.

0: Normal operation. All clocks are disabled automatically in Stop mode.

1: Automatic clock stop disabled. All active clocks and oscillators continue to run during Stop

mode, allowing full debug capability. On exit from Stop mode, the clock settings are set to the

Stop mode exit state.

Bit 0 DBG_SLEEP: Allows CPU1 debug in Sleep mode

0: Normal operation. Processor clock is stopped automatically in Sleep mode.

1: Automatic clock stop disabled. Processor clock continue to run, allowing full debug

capability.

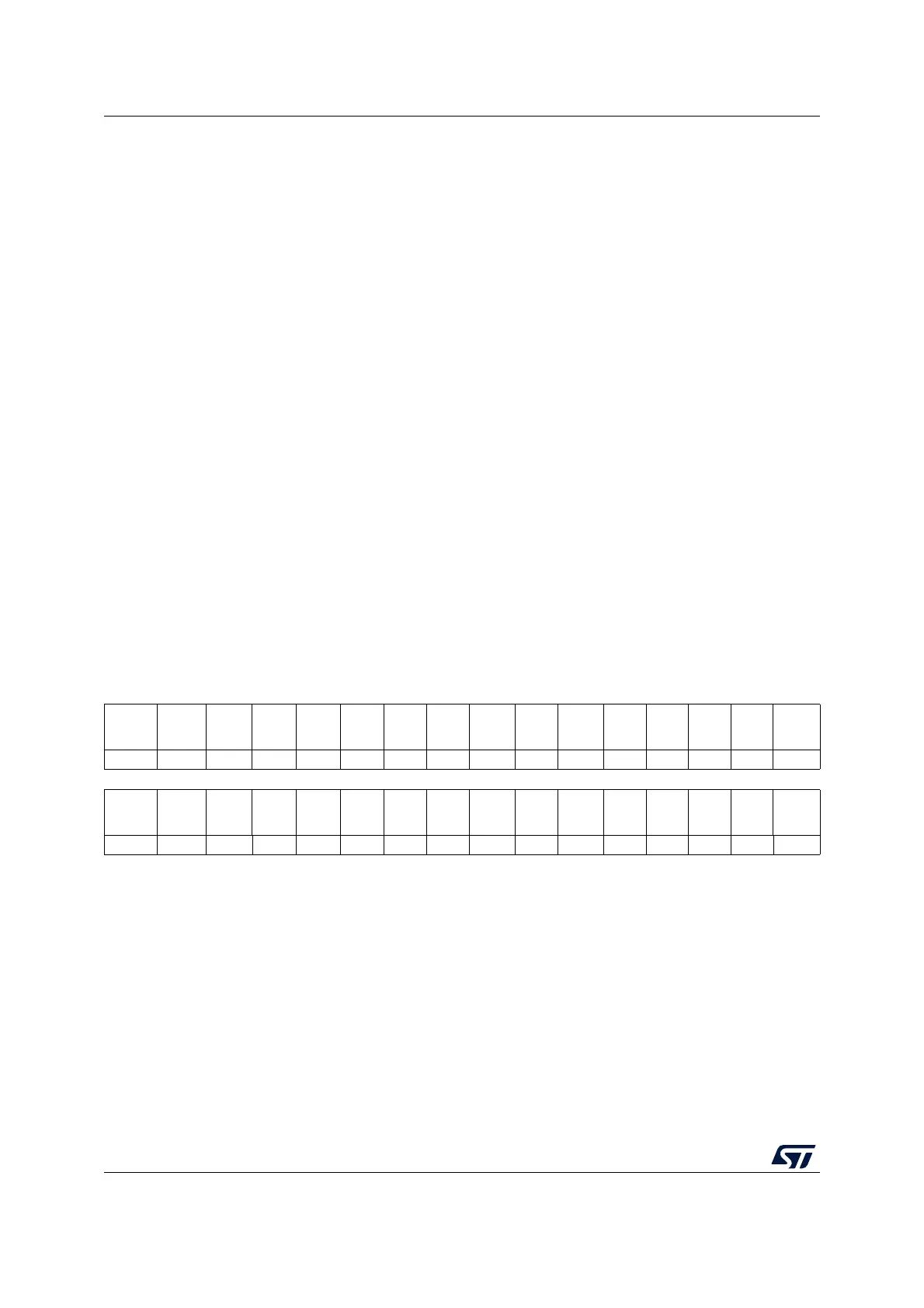

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

DBG_

LPTIM1

_STOP

Res. Res. Res. Res. Res. Res. Res.

DBG_

I2C3

_STOP

DBG_

I2C2

_STOP

DBG_

I2C1

_STOP

Res. Res. Res. Res. Res.

rw rw rw rw

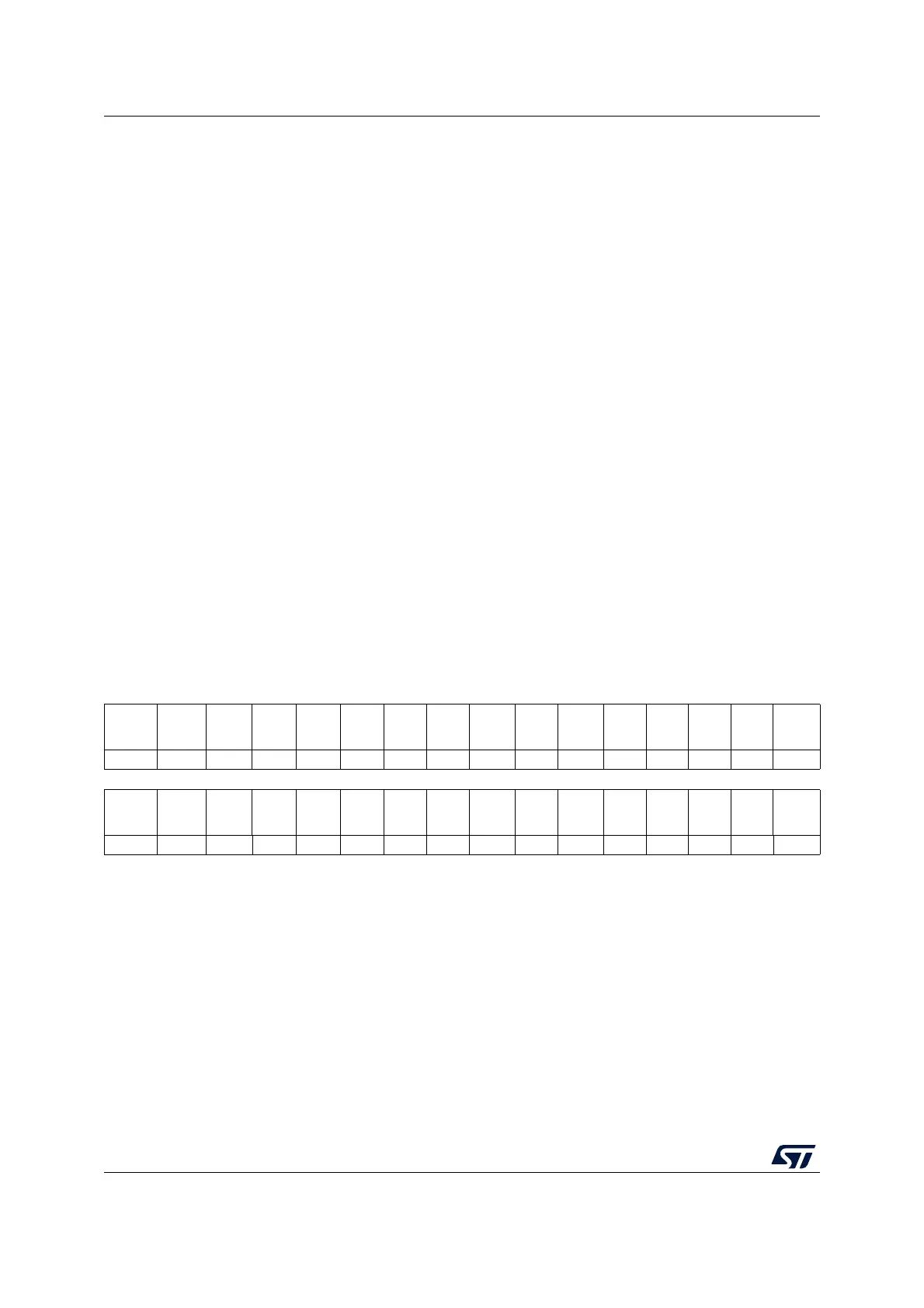

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res.

DBG_

IWDG

_STOP

DBG_

WWDG

_STOP

DBG_

RTC

_STOP

Res. Res. Res. Res. Res. Res. Res. Res. Res.

DBG_

TIM2

_STOP

rw rw rw rw

Bit 31 DBG_LPTIM1_STOP: LPTIM1 stop in CPU1 debug

0: Normal operation. LPTIM1 continues to operate while CPU1 is in debug mode.

1: Stop in debug. LPTIM1 is frozen while CPU1 is in debug mode.

Bits 30:24 Reserved, must be kept at reset value.

Bit 23 DBG_I2C3_STOP: I2C3 SMBUS timeout stop in CPU1 debug

0: Normal operation. I2C3 SMBUS timeout continues to operate while CPU1 is in debug

mode.

1: Stop in debug. I2C3 SMBUS timeout is frozen while CPU1 is in debug mode.

Loading...

Loading...