RM0453 Rev 2 1415/1454

RM0453 Debug support (DBG)

1441

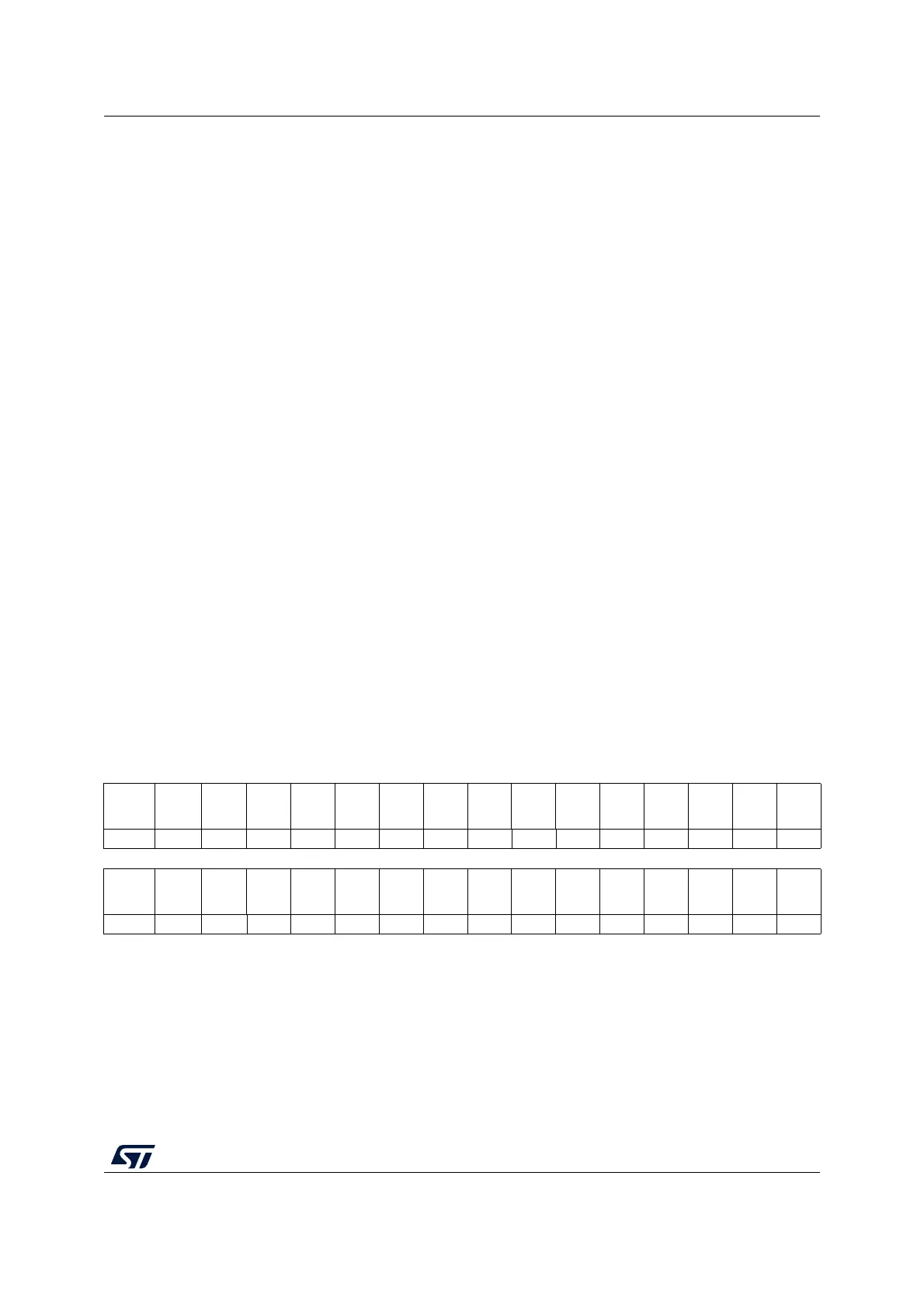

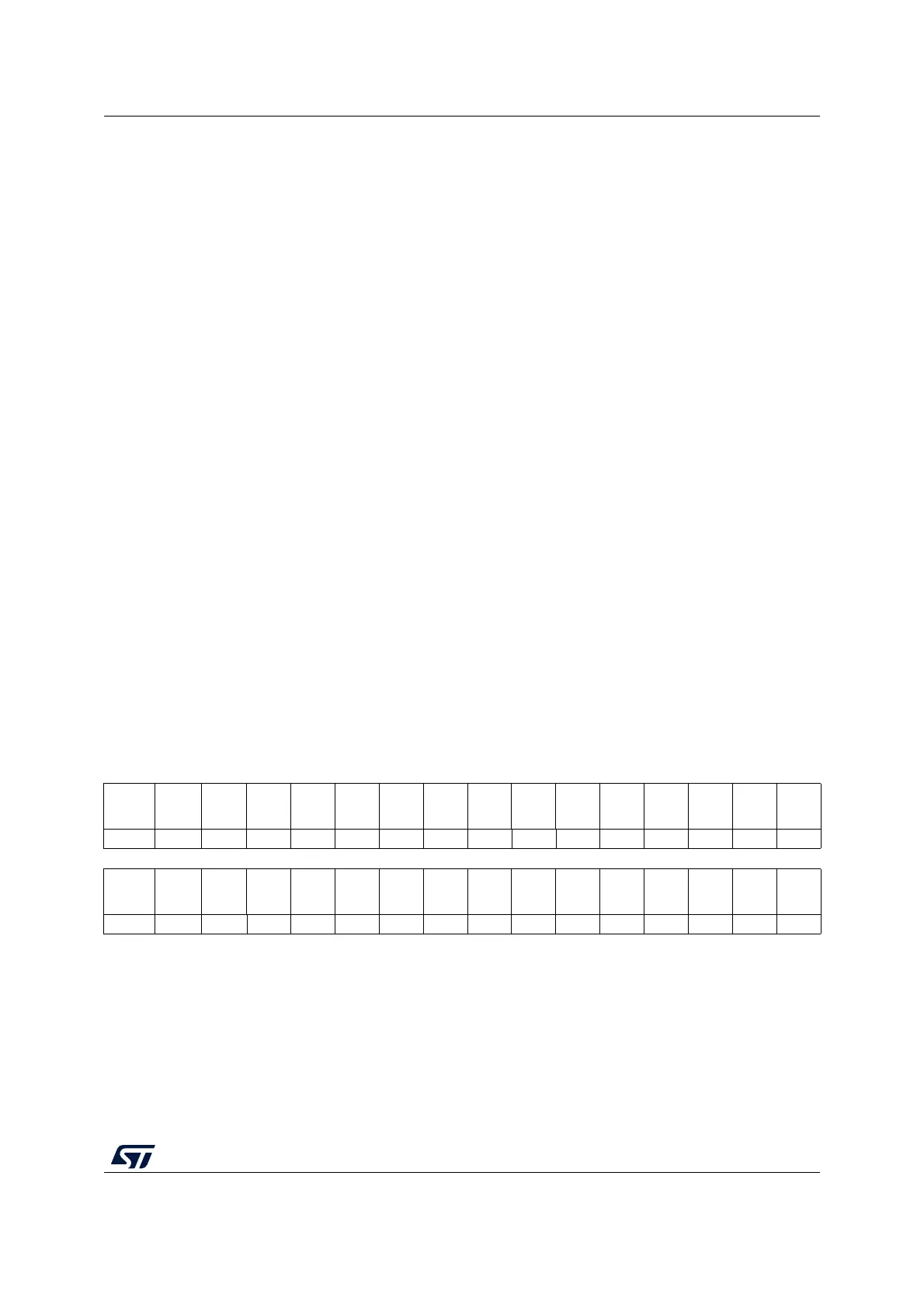

38.12.4 DBGMCU CPU2 APB1 peripheral freeze register 1

(DBGMCU_C2APB1FZR1)

Address offset: 0x040

Reset value: 0x0000 0000

Bit 22 DBG_I2C2_STOP: I2C2 SMBUS timeout stop in CPU1 debug

0: Normal operation. I2C2 SMBUS timeout continues to operate while CPU1 is in debug

mode.

1: Stop in debug. I2C2 SMBUS timeout is frozen while CPU1 is in debug mode.

Bit 21 DBG_I2C1_STOP: I2C1 SMBUS timeout stop in CPU1 debug

0: Normal operation. I2C1 SMBUS timeout continues to operate while CPU1 is in debug

mode.

1: Stop in debug. I2C1 SMBUS timeout is frozen while CPU1 is in debug mode.

Bits 20:13 Reserved, must be kept at reset value.

Bit 12 DBG_IWDG_STOP: IWDG stop in CPU1 debug

0: Normal operation. IWDG continues to operate while CPU1 is in debug mode.

1: Stop in debug. IWDG is frozen while CPU1 is in debug mode.

Bit 11 DBG_WWDG_STOP: WWDG stop in CPU1 debug

0: Normal operation. WWDG continues to operate while CPU1 is in debug mode.

1: Stop in debug. WWDG is frozen while CPU1 is in debug mode.

Bit 10 DBG_RTC_STOP: RTC stop in CPU1 debug

0: Normal operation. RTC continues to operate while CPU1 is in debug mode.

1: Stop in debug. RTC is frozen while CPU1 is in debug mode.

Bits 9:1 Reserved, must be kept at reset value.

Bit 0 DBG_TIM2_STOP: TIM2 stop in CPU1 debug

0: Normal operation. TIM2 continues to operate while CPU1 is in debug mode.

1: Stop in debug. TIM2 is frozen while CPU1 is in debug mode.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

DBG_

LPTIM1

_STOP

Res. Res. Res. Res. Res. Res. Res.

DBG_

I2C3_

STOP

DBG_

I2C2

_STOP

DBG_

I2C1

_STOP

Res. Res. Res. Res. Res.

rw rw rw rw

1514131211109876543210

Res. Res. Res.

DBG_

IWDG

_STOP

Res.

DBG_

RTC

_STOP

Res. Res. Res. Res. Res. Res. Res. Res. Res.

DBG_

TIM2

_STOP

rw rw rw

Loading...

Loading...