Debug support (DBG) RM0453

1418/1454 RM0453 Rev 2

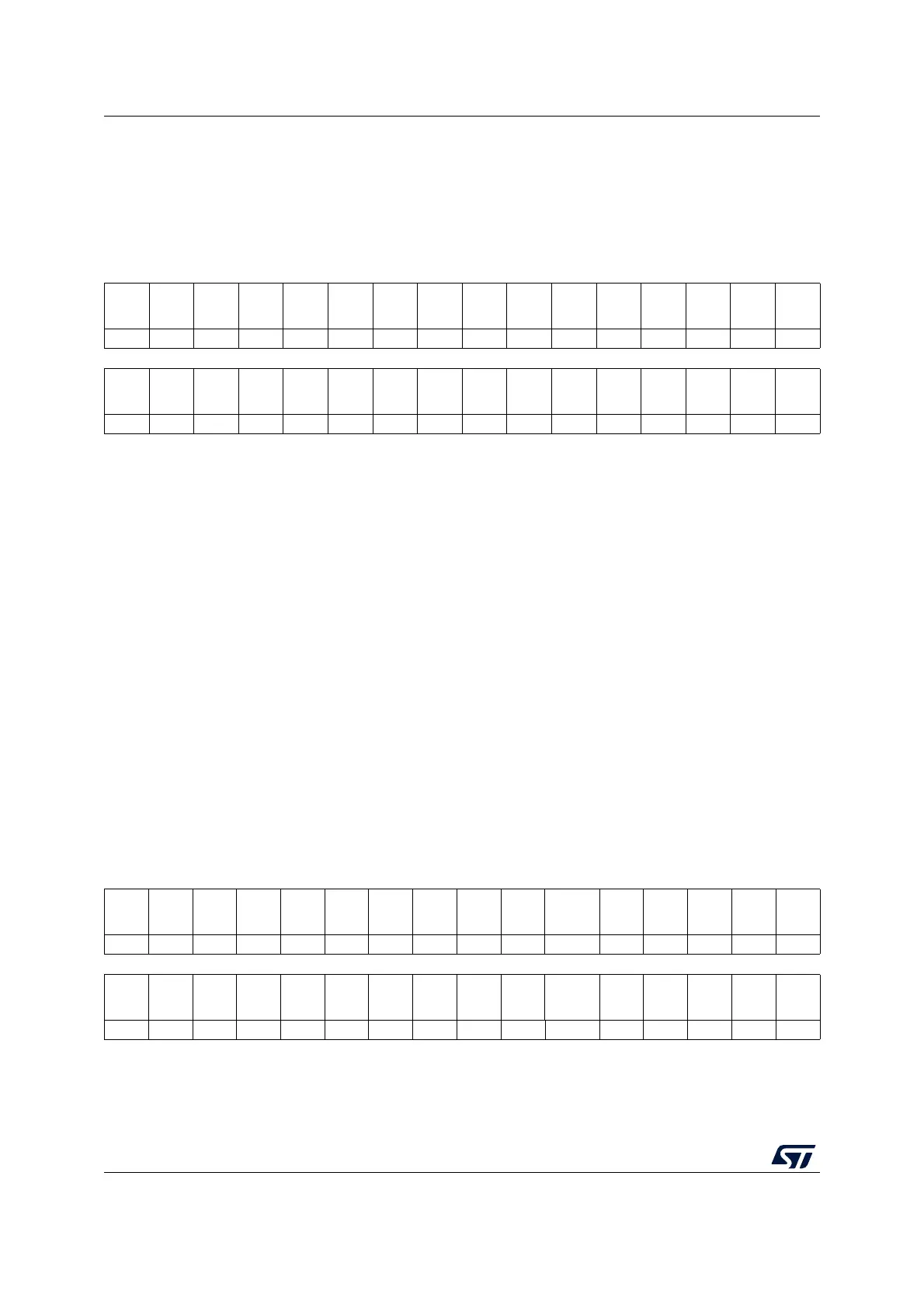

38.12.7 DBGMCU CPU1 APB2 peripheral freeze register

(DBGMCU_APB2FZR)

Address offset: 0x04C

Reset value: 0x0000 0000

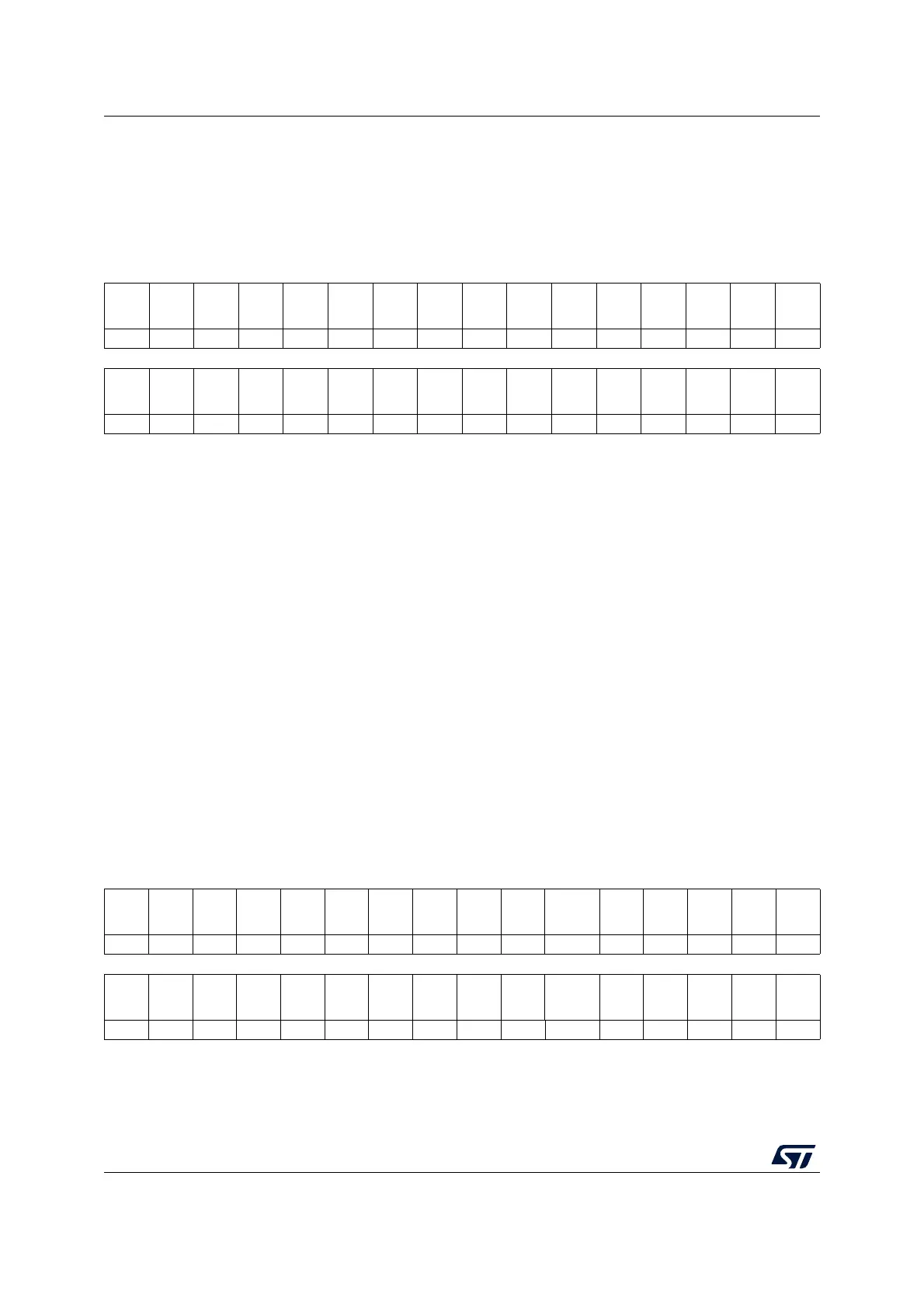

38.12.8 DBGMCU CPU2 APB2 peripheral freeze register

(DBGMCU_C2APB2FZR)

Address offset: 0x048

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

DBG_

TIM17

_STOP

DBG_

TIM16

_STOP

Res.

rw rw

1514131211109876543210

Res. Res. Res. Res.

DBG_

TIM1

_STOP

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

rw

Bits 31:19 Reserved, must be kept at reset value.

Bit 18 DBG_TIM17_STOP: TIM17 stop in CPU1 debug

0: Normal operation. TIM17 continues to operate while CPU1 is in debug mode.

1: Stop in debug. TIM17 is frozen while CPU1 is in debug mode.

Bit 17 DBG_TIM16_STOP: TIM16 stop in CPU1 debug

0: Normal operation. TIM16 continues to operate while CPU1 is in debug mode.

1: Stop in debug. TIM16 is frozen while CPU1 is in debug mode.

Bits 16:12 Reserved, must be kept at reset value.

Bit 11 DBG_TIM1_STOP: TIM1 stop in CPU1 debug

0: Normal operation. TIM1 continues to operate while CPU1 is in debug mode.

1: Stop in debug. TIM1 is frozen while CPU1 is in debug mode.

Bits 10:0 Reserved, must be kept at reset value.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

DBG_

TIM17

_STOP

DBG_

TIM16

_STOP

Res.

rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res.

DBG_

TIM1

_STOP

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

rw

Loading...

Loading...