Agilent 4155C/4156C SCPI Command Reference, Edition 1 3-15

Status Reporting Structure

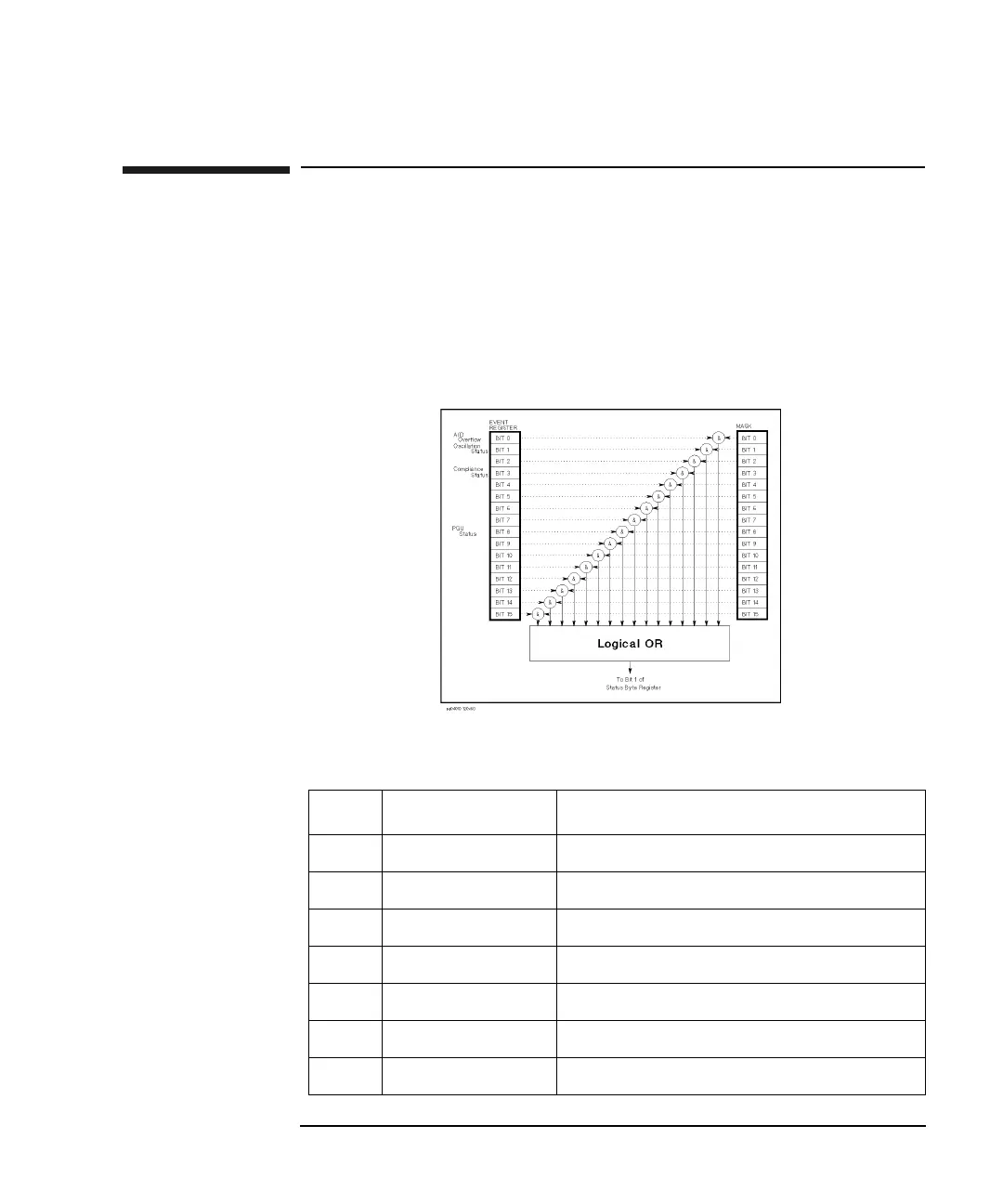

Measurement/Stress Status Register

Measurement/Stress Status Register

This register consists of EVENT and event enable (MASK) registers.

You enable the desired bits of the EVENT register by using the MASK register. 1

enables, 0 masks the corresponding bit of EVENT register. The MASK register is

set by the :STATus:MEASurement:ENABle command. See “STATus Subsystem” in

Chapter 5 for details about this command.

Figure 3-9 Measurement/Stress Status Register

This register is not a standard SCPI register.

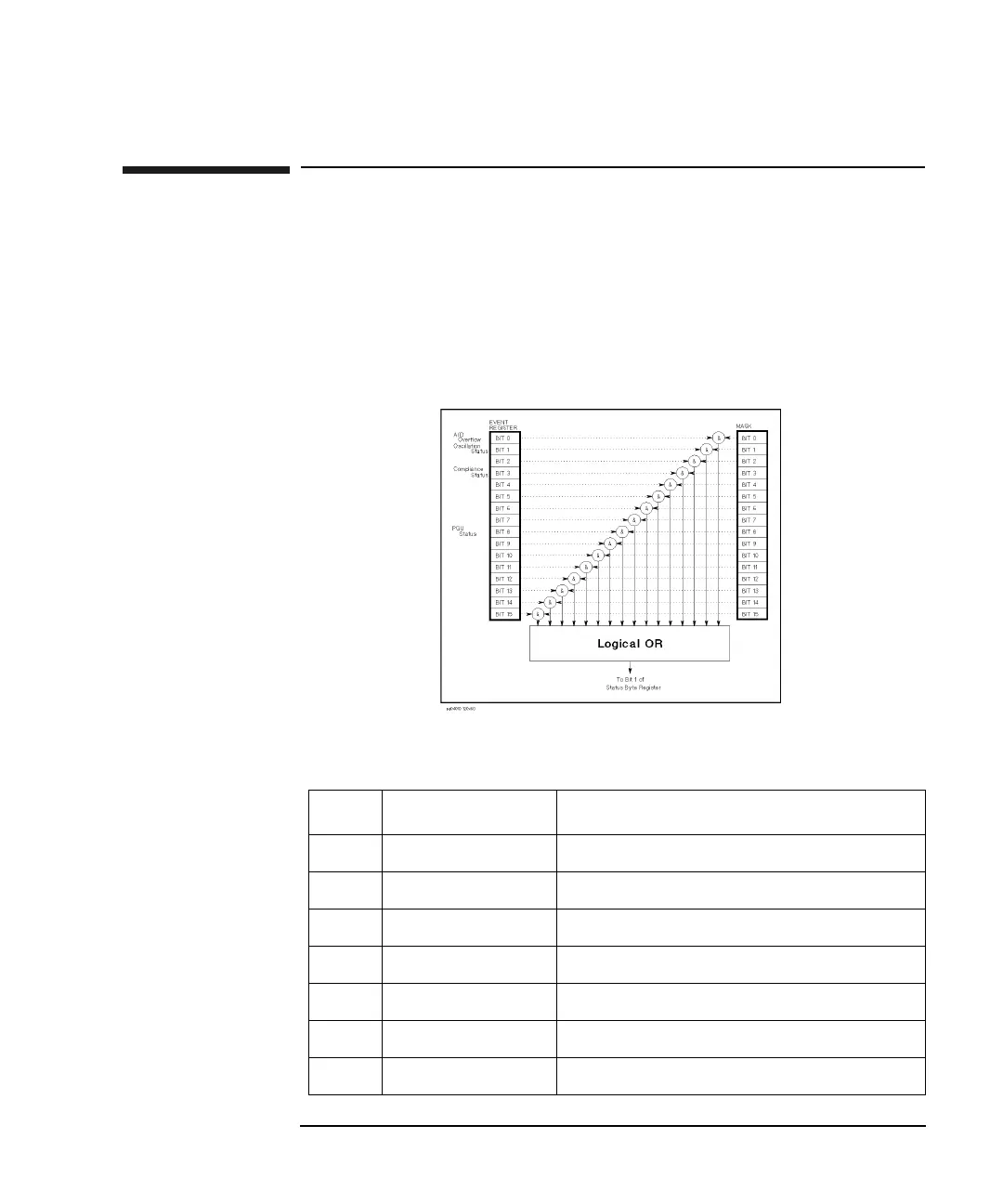

Table 3-6 Measurement/Stress Status Register

Bit Definition Explanation

0 A/D Overflow This bit is set if A/D converter overflows.

1 Oscillation Status This bit is set if SMU oscillates.

2 NOT USED This bit is always zero.

3 Compliance Status This bit is set if SMU reaches compliance.

4 to 7 NOT USED These bits are always zero.

8 PGU Status This bit is set if PGU reaches the current limit.

9 to 15 NOT USED These bits are always zero.

Loading...

Loading...