GR712RC-UM, Jun 2017, Version 2.9 121 www.cobham.com/gaisler

GR712RC

The receiver DMA works in the same way except that it checks if the FIFO is half-full and then per-

forms a burst write to the bus which is half the fifo size in length. The last burst might be shorter.

There might be 1 to 3 single byte writes when writing the beginning and end of the received packets.

16.7.1 APB slave interface

As mentioned above, the APB interface provides access to the user registers which are 32-bits in

width. The accesses to this interface are required to be aligned word accesses. The result is undefined

if this restriction is violated.

16.7.2 AHB master interface

The GRSPW contains a single master interface which is used by both the transmitter and receiver

DMA engines. The arbitration algorithm between the channels is done so that if the current owner

requests the interface again it will always acquire it. This will not lead to starvation problems since the

DMA engines always deassert their requests between accesses.

The AHB accesses are always word accesses (HSIZE = 0x010) of type incremental burst with unspec-

ified length (HBURST = 0x001) if rmap and rxunaligned are disabled. Otherwise the accesses can be

of size byte, halfword and word (HSIZE = 0x000, 0x001, 0x010). Byte and halfword accesses are

always NONSEQ.

The burst length will be half the AHB FIFO size except for the last transfer for a packet which might

be smaller. Shorter accesses are also done during descriptor reads and status writes.

The AHB master also supports non-incrementing accesses where the address will be constant for sev-

eral consecutive accesses. HTRANS will always be NONSEQ in this case while for incrementing

accesses it is set to SEQ after the first access. This feature is included to support non-incrementing

reads and writes for RMAP.

If the GRSPW does not need the bus after a burst has finished there will be one idle cycle (HTRANS

= IDLE).

BUSY transfer types are never requested and the core provides full support for ERROR, RETRY and

SPLIT responses.

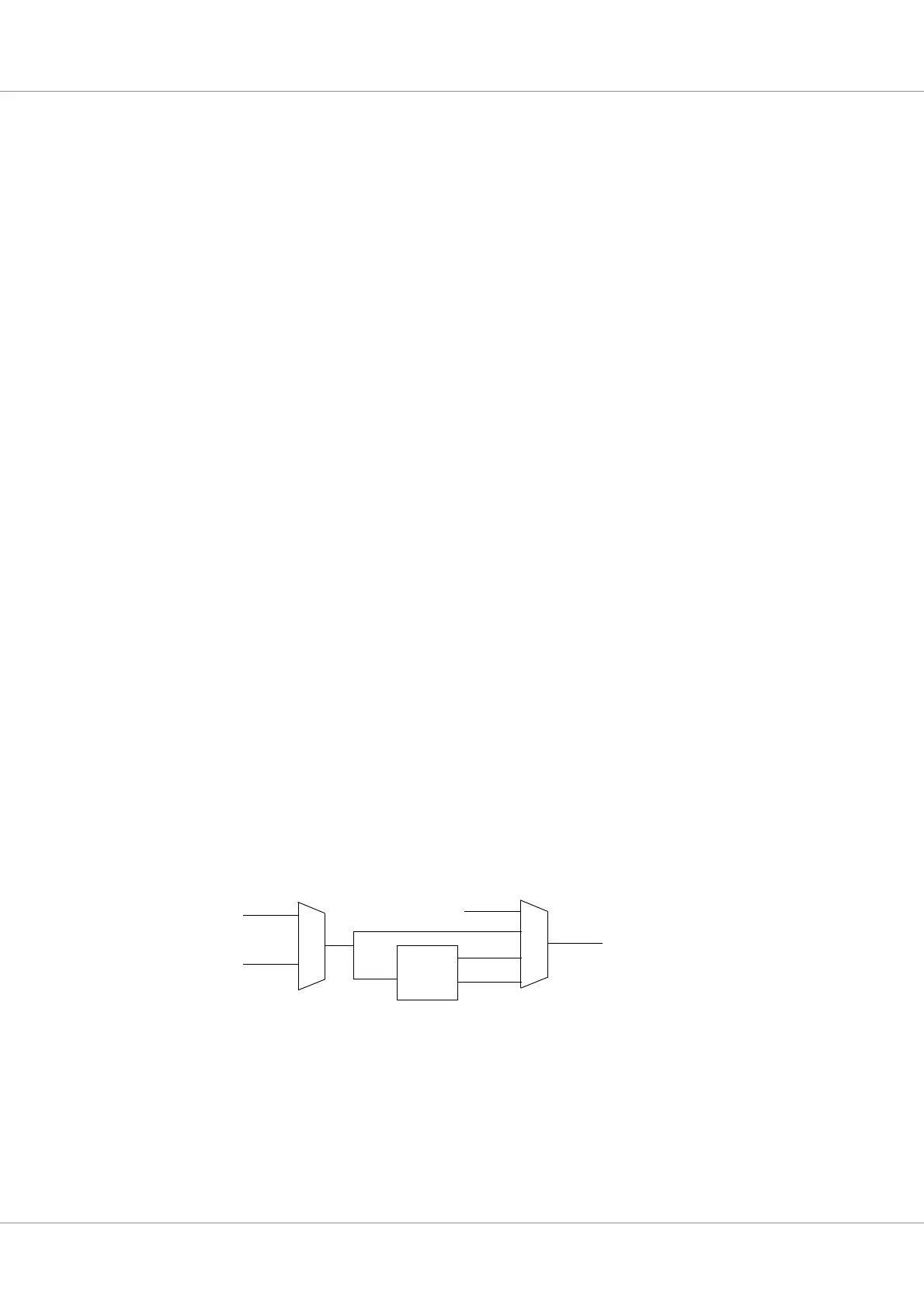

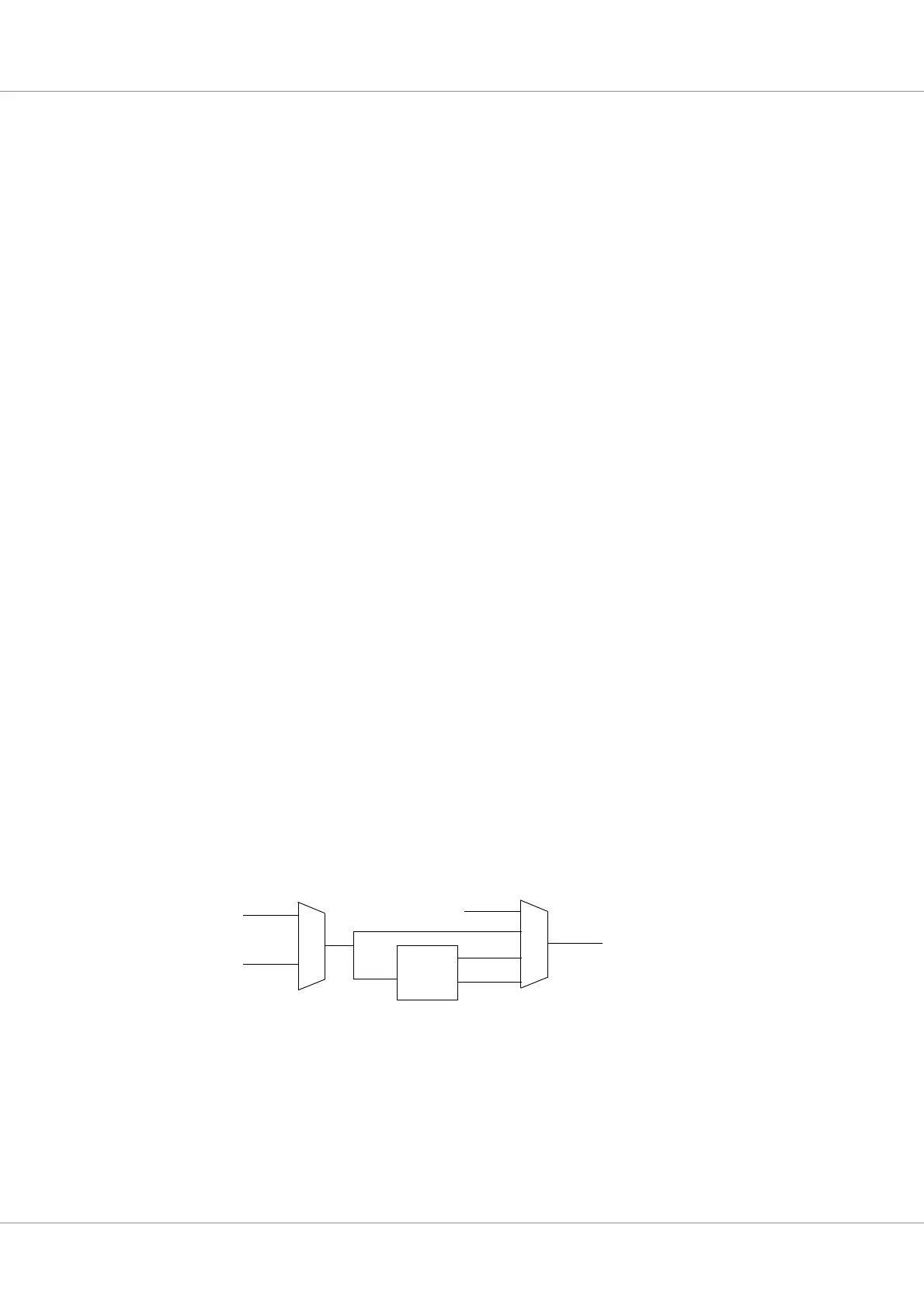

16.8 SpaceWire clock generation

The clock source for SpaceWire is selectable through a clock multiplexer, which inputs are the SPW-

CLK, and INCLK inputs. The selected clock is then used either as 1X, 2X or 4X as shown in the fig-

ure below. The system clock (CLK) is also selectable as SpaceWire transmit clock.

After reset the selected SpaceWire transmit clock is SPWCLK without any multiplication. The Space-

Wire clock multiplexers and the DLL reset are controlled through the GRGPREG register.

The SpaceWire transmit clock must be a multiple of 10 MHz in order to achieive 10 Mbps start up bit

rate. The division to 10 MHz is done internally in the GRSPW2 core. During reset the clock divider

register in GRSPW2 gets its value from 4 I/O pins that must be pulled up/down to set the divider cor-

rectly. Pins (MSB-LSB) SWMX45, 43, 40 and 37 are used for this. Thus it is possible to use a SPW-

CLK which is any multiple of 10 between 10-100 MHz (note that the required precision is 10 MHz +/

- 1 MHz).

MFDLL

2X

4X

1X

SPWCLK

INCLK

SpaceWire TX clock

CLK

Loading...

Loading...