GR712RC-UM, Jun 2017, Version 2.9 82 www.cobham.com/gaisler

GR712RC

9.6 DSU registers

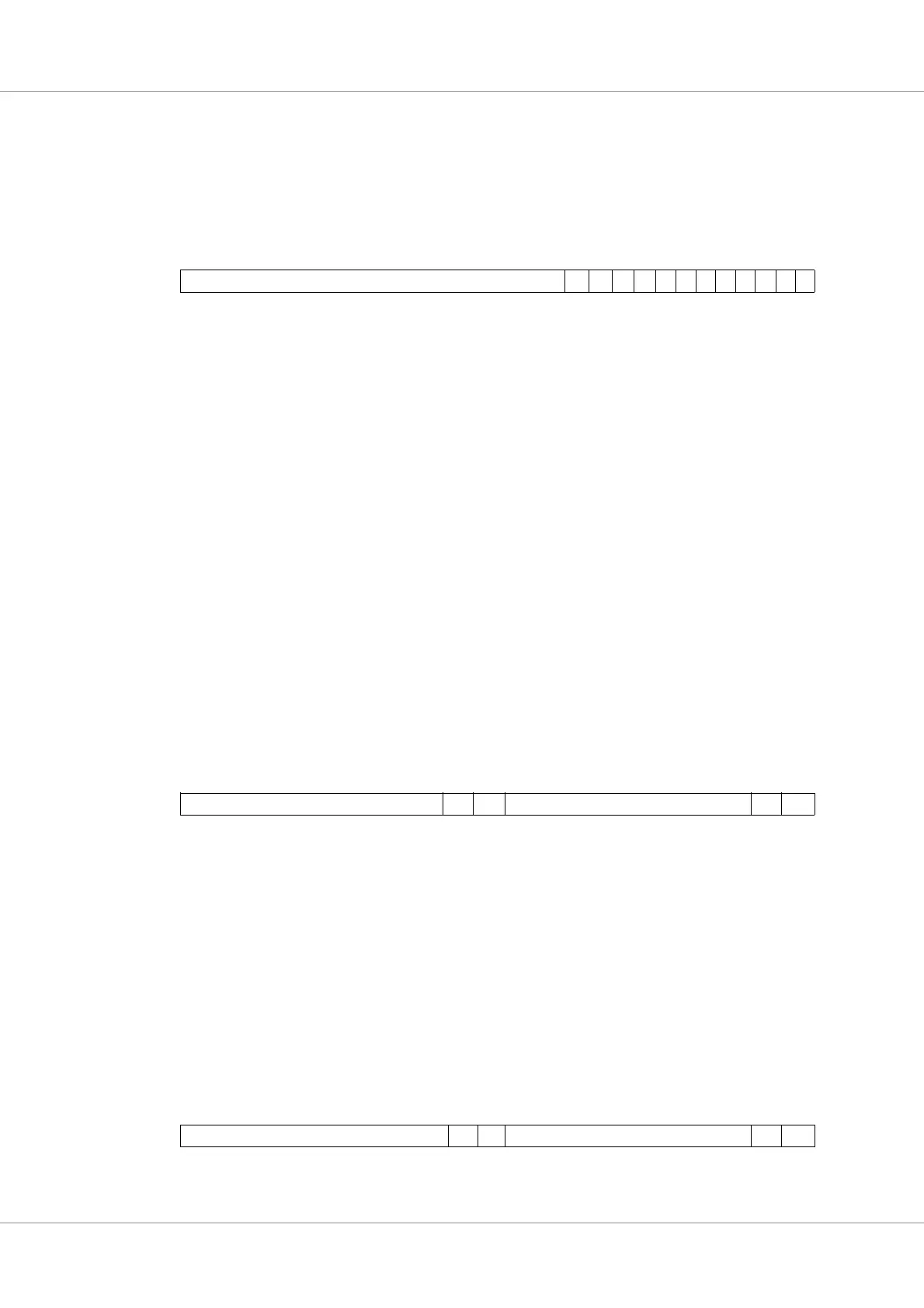

9.6.1 DSU control register

The DSU is controlled by the DSU control register:

.

[0]: Trace enable (TE). Enables instruction tracing. If set the instructions will be stored in the trace buffer. Remains set

when then processor enters debug or error mode.

[1]: Break on error (BE) - if set, will force the processor to debug mode when the processor would have entered error

condition (trap in trap).

[2]: Break on IU watchpoint (BW)- if set, debug mode will be forced on a IU watchpoint (trap 0xb).

[3]: Break on S/W breakpoint (BS) - if set, debug mode will be forced when an breakpoint instruction (ta 1) is executed.

[4]: Break on trap (BX) - if set, will force the processor into debug mode when any trap occurs.

[5]: Break on error traps (BZ) - if set, will force the processor into debug mode on all except the following traps:

priviledged_instruction, fpu_disabled, window_overflow, window_underflow, asynchronous_interrupt, ticc_trap.

[6]: Debug mode (DM). Indicates when the processor has entered debug mode (read-only).

[7]: Unused, hardcoded to 1.

[8]: Unused, hardcoded to 0.

[9]: Processor error mode (PE) - returns ‘1’ on read when processor is in error mode, else ‘0’. If written with ‘1’, it will

clear the error and halt mode.

[10]: Processor halt (HL). Returns ‘1’ on read when processor is halted. If the processor is in debug mode, setting this bit

will put the processor in halt mode.

[11]: Power down (PW). Returns ‘1’ when processor in power-down mode.

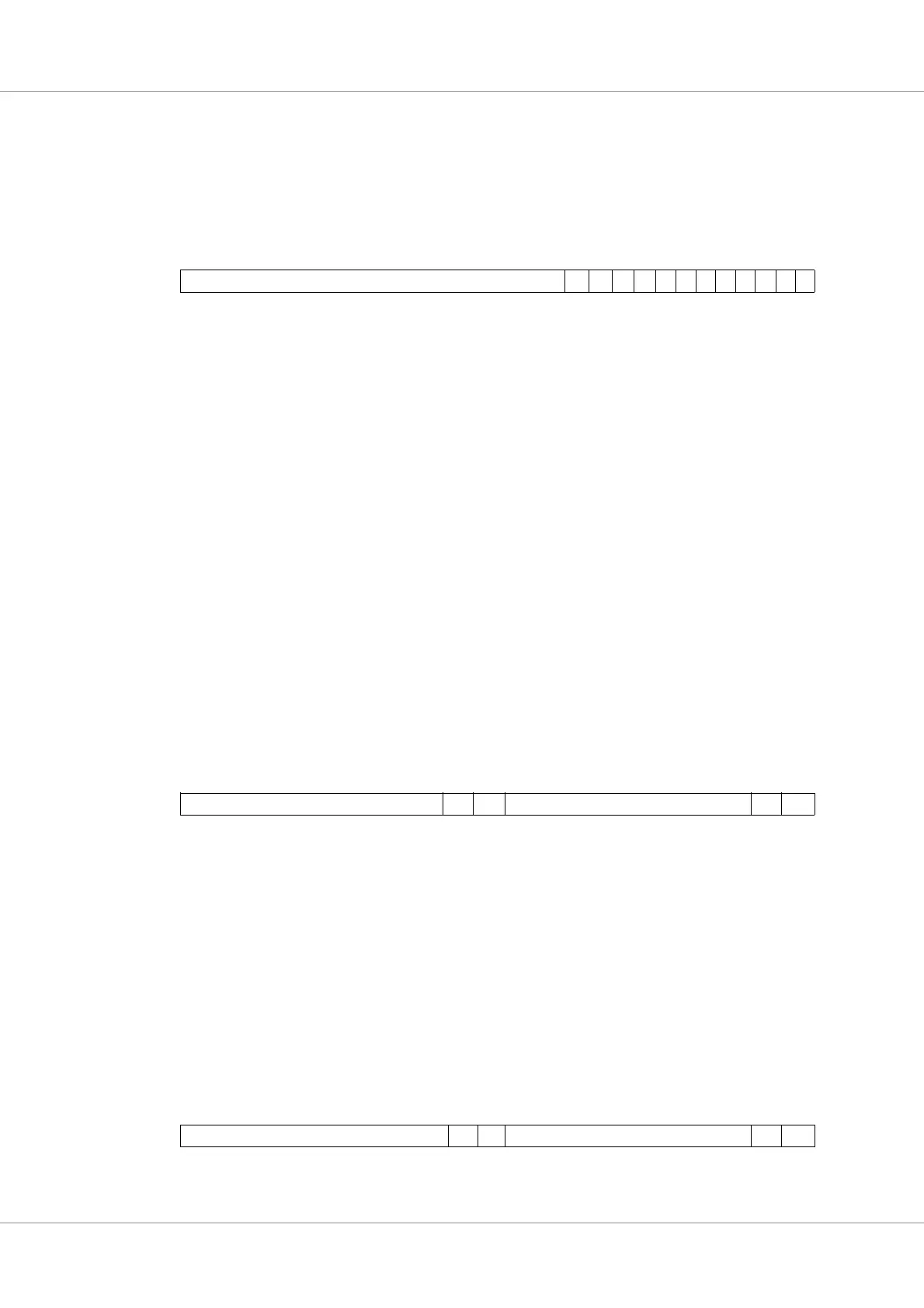

9.6.2 DSU Break and Single Step register

This register is used to break or single step the processor(s). This register controls all processors in a

multi-processor system, and is only accessible in the DSU memory map of processor 0.

[15:0]: Break now (BNx) -Force processor x into debug mode if the Break on watchpoint (BW) bit in the processors DSU

control register is set. If cleared, the processor x will resume execution.

[31:16]: Single step (SSx) - if set, the processor x will execute one instruction and return to debug mode. The bit remains set

after the processor goes into the debug mode.

9.6.3 DSU Debug Mode Mask Register

When one of the processors in a multiprocessor LEON3 system enters the debug mode the value of

the DSU Debug Mode Mask register determines if the other processors are forced in the debug mode.

This register controls all processors in a multi-processor system, and is only accessible in the DSU

memory map of processor 0.

Figure 43. DSU control register

0123457

31

TE

8910

BEBWBSBXBZ10PE

6

DM

HL

11

PW

Figure 44. DSU Break and Single Step register

0

31

BN0

1

BN1

16

SS0

17

SS1

. . .

. . .

Figure 45. DSU Debug Mode Mask register

0

31

ED0

1

ED1

215

. . .

16

17

DM1

18

DM0

. . .

Loading...

Loading...