GR712RC-UM, Jun 2017, Version 2.9 96 www.cobham.com/gaisler

GR712RC

14.3 Registers

The core is programmed through registers mapped into APB address space. GRGPIO port 1 registers

are mapped at address 0x80000900, while GRGPIO port 2 registers are at 0x80000A00.

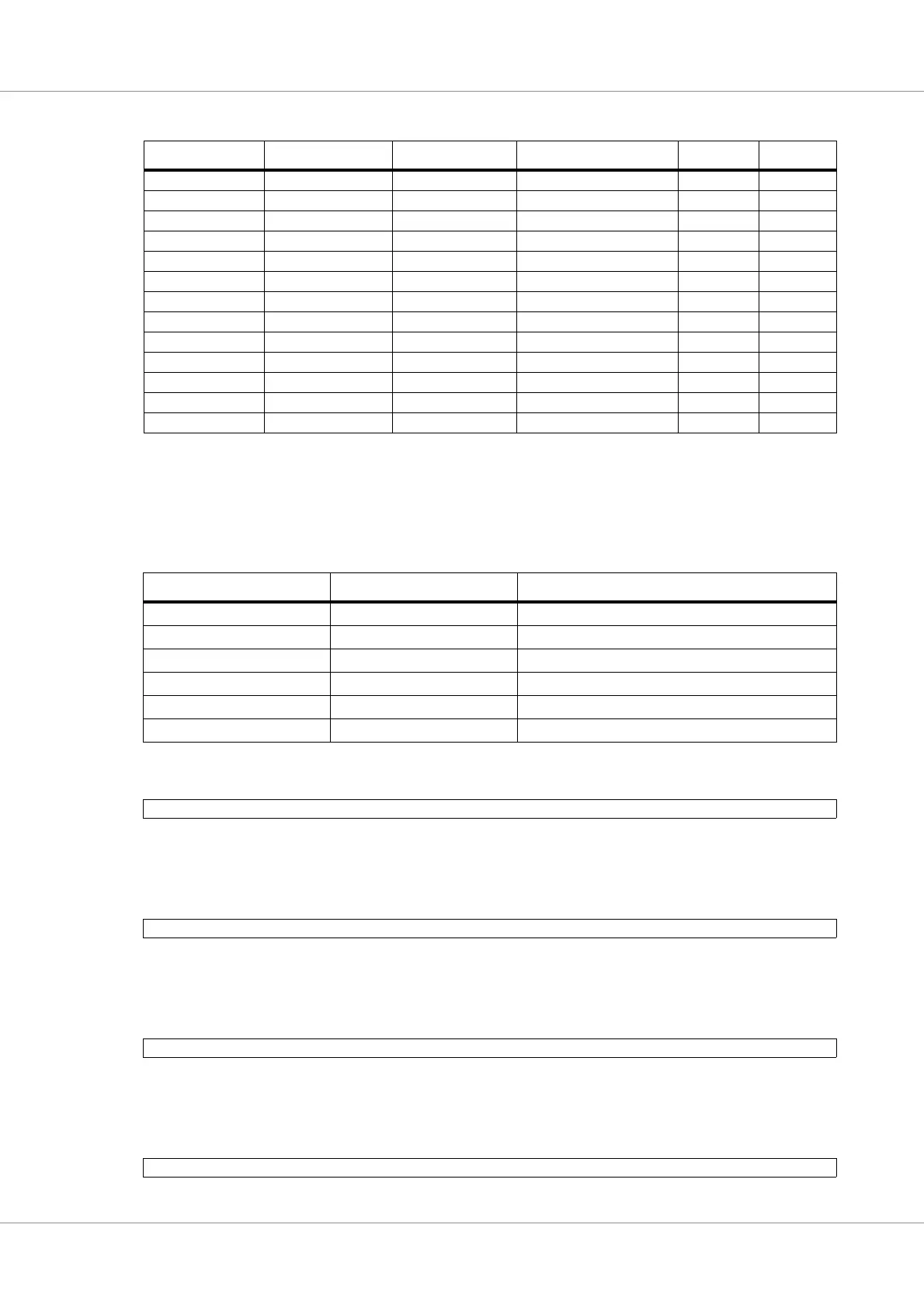

GRGPIO - 2 19 GPIO[51] SWMX[54] In/Out

GRGPIO - 2 20 GPIO[52] SWMX[55] In

GRGPIO - 2 21 GPIO[53] SWMX[56] In

GRGPIO - 2 22 GPIO[54] SWMX[57] In/Out

GRGPIO - 2 23 GPIO[55] SWMX[58] In/Out

GRGPIO - 2 24 GPIO[56] SWMX[59] In/Out

GRGPIO - 2 25 GPIO[57] SWMX[60] In/Out

GRGPIO - 2 26 GPIO[58] SWMX[61] In/Out

GRGPIO - 2 27 GPIO[59] SWMX[62] In/Out

GRGPIO - 2 28 GPIO[60] SWMX[63] In/Out

GRGPIO - 2 29 GPIO[61] SWMX[64] In/Out

GRGPIO - 2 30 GPIO[62] SWMX[65] In/Out

GRGPIO - 2 31 GPIO[63] SWMX[66] In/Out

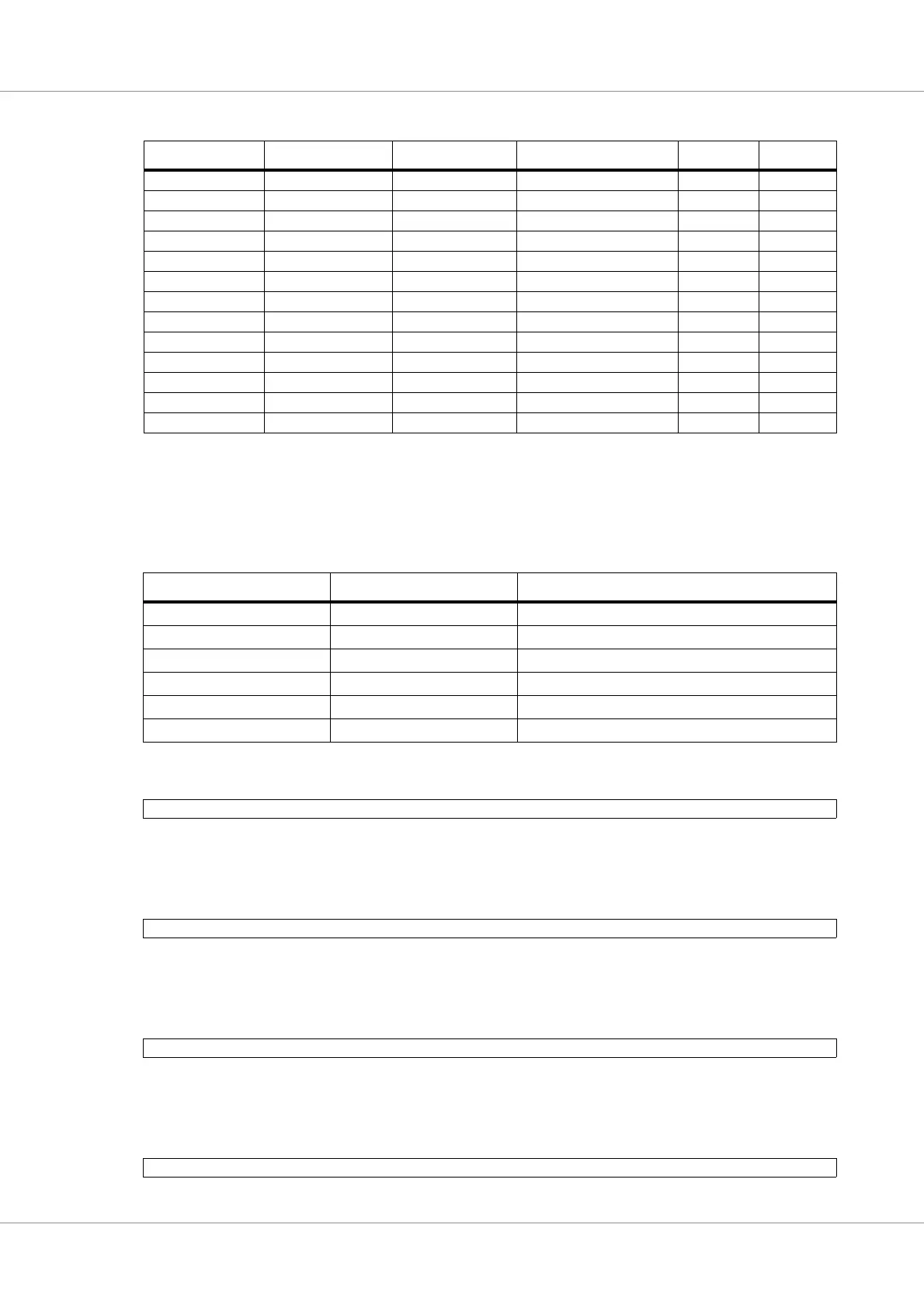

Table 68. General Purpose I/O Port registers

APB address port 1 APB address port 2 Register

0x80000900 0x80000A00 I/O port data register

0x80000904 0x80000A04 I/O port output register

0x80000908 0x80000A08 I/O port direction register

0x8000090C 0x80000A0C Interrupt mask register

0x80000910 0x80000A10 Interrupt polarity register

0x80000914 0x80000A14 Interrupt edge register

Table 69. I/O port data register

31 0

I/O port input value

31: 0 I/O port input value. Bits that are configured as outputs will always read zero from this register.

Table 70. I/O port output register

31 0

I/O port output value

31: 0 I/O port output value

Table 71. I/O port direction register

31 0

I/O port direction value

31: 0 I/O port direction value (0=output disabled, 1=output enabled). Input-only bits are don’t care.

Table 72. Interrupt mask register

31 0

Interrupt mask

TABLE 67. GPIO ports and signals

GPIO port Register bit no. Pin function External pin name InterruptDirection

Loading...

Loading...