GR712RC-UM, Jun 2017, Version 2.9 18 www.cobham.com/gaisler

GR712RC

1.8 Document revision history

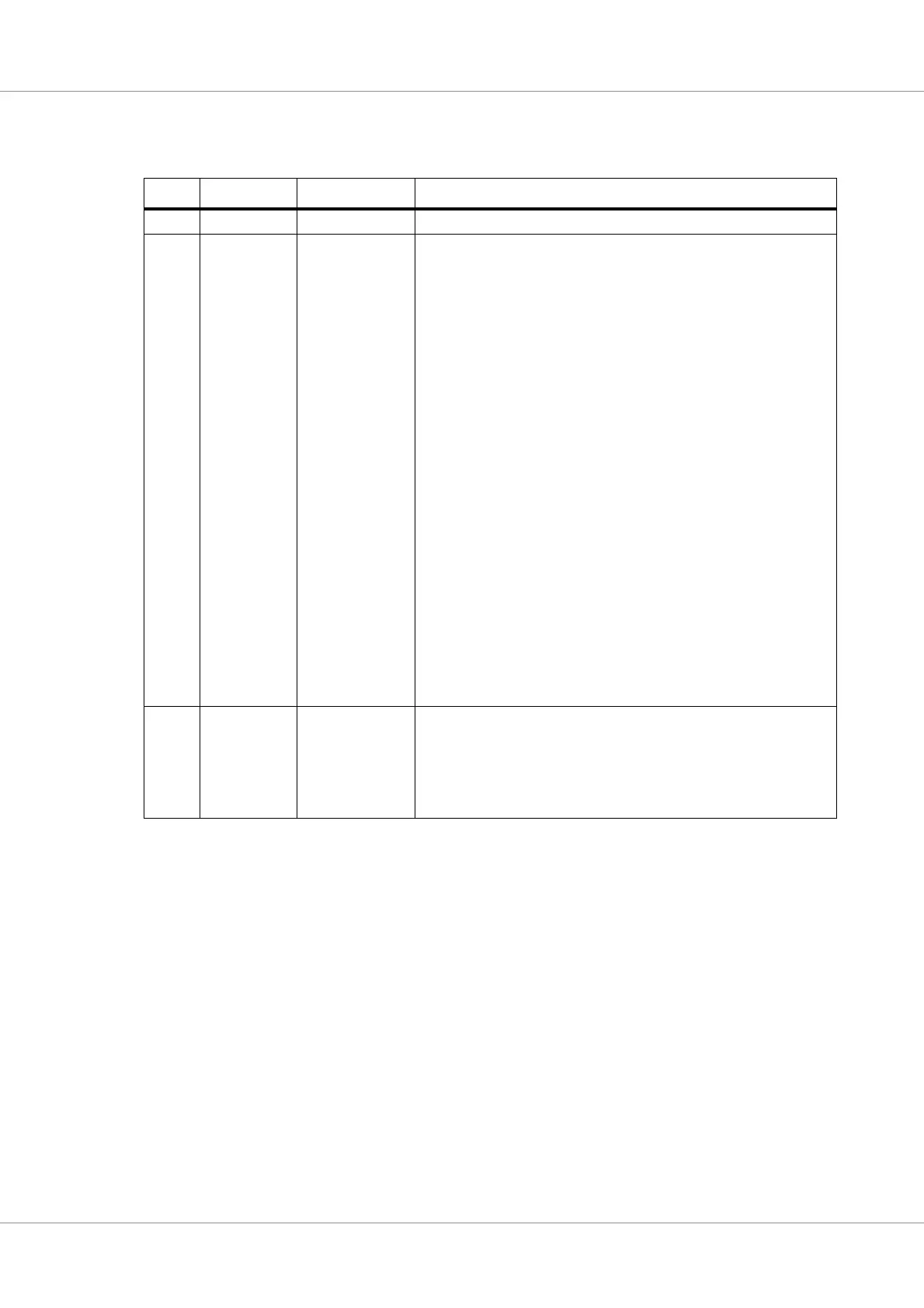

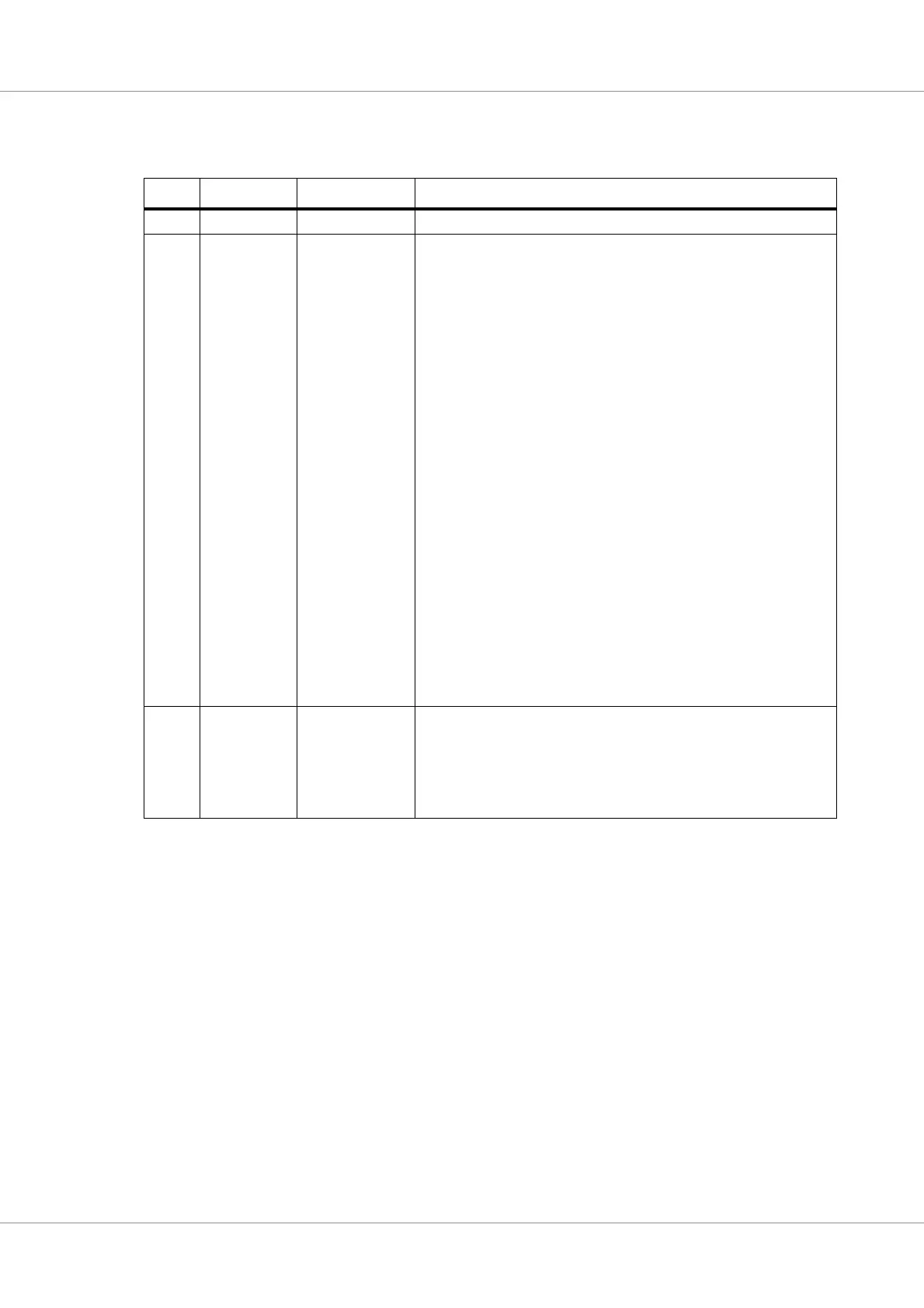

TABLE 4. Revision history

Issue Date Sections Description

2.9 2017-06-22 1.7.14 Added errata about TLB disable when MMU is enabled

2.8 2017-02-28 1.7.3

1.7.13

4.2.6

4.2.9

4.2.12, 4.5.1,

4.6.1

4.2.15

4.5.2, 4.5.5,

4.5.6

4.5.4

5.14.2

15.6

16.1

16.8

16.9

18.1

23.3

Updated error handling for GRSPW2

Added errata for back-to-back storage

Added description of CASA instruction

FPU option value corrected

ASI clarification for ASI 0x10, 0x11 and 0x13.

Updated multiprocessor wording

Clarified cache access descriptions

FD bit interpretation corrected in Cache Control Register

TRP bit description corrected in Memory configuration register 2

Clarified APBUART receive interrupts

Further clarified number of DMA channels per GRSPW2

Clarified relationship between SPW receive data rate and trans-

mit clock

Clarified reset value of AS bit in GRSPW control register

Added reference to CAN multiplexer to clarify the need to acti-

vate OC-CAN

LSD bit description corrected in SPI controller Command regis-

ter

2.7 2016-01-26 7.2

15.2.2

AHBSTAT: Remove incorrect note about AMBA ERROR over-

riding correctable errors.

APBUART documentation mentioned receive ready instead of

data ready field.

Update footer

Loading...

Loading...