GR712RC-UM, Jun 2017, Version 2.9 137 www.cobham.com/gaisler

GR712RC

18.4 BasicCAN mode

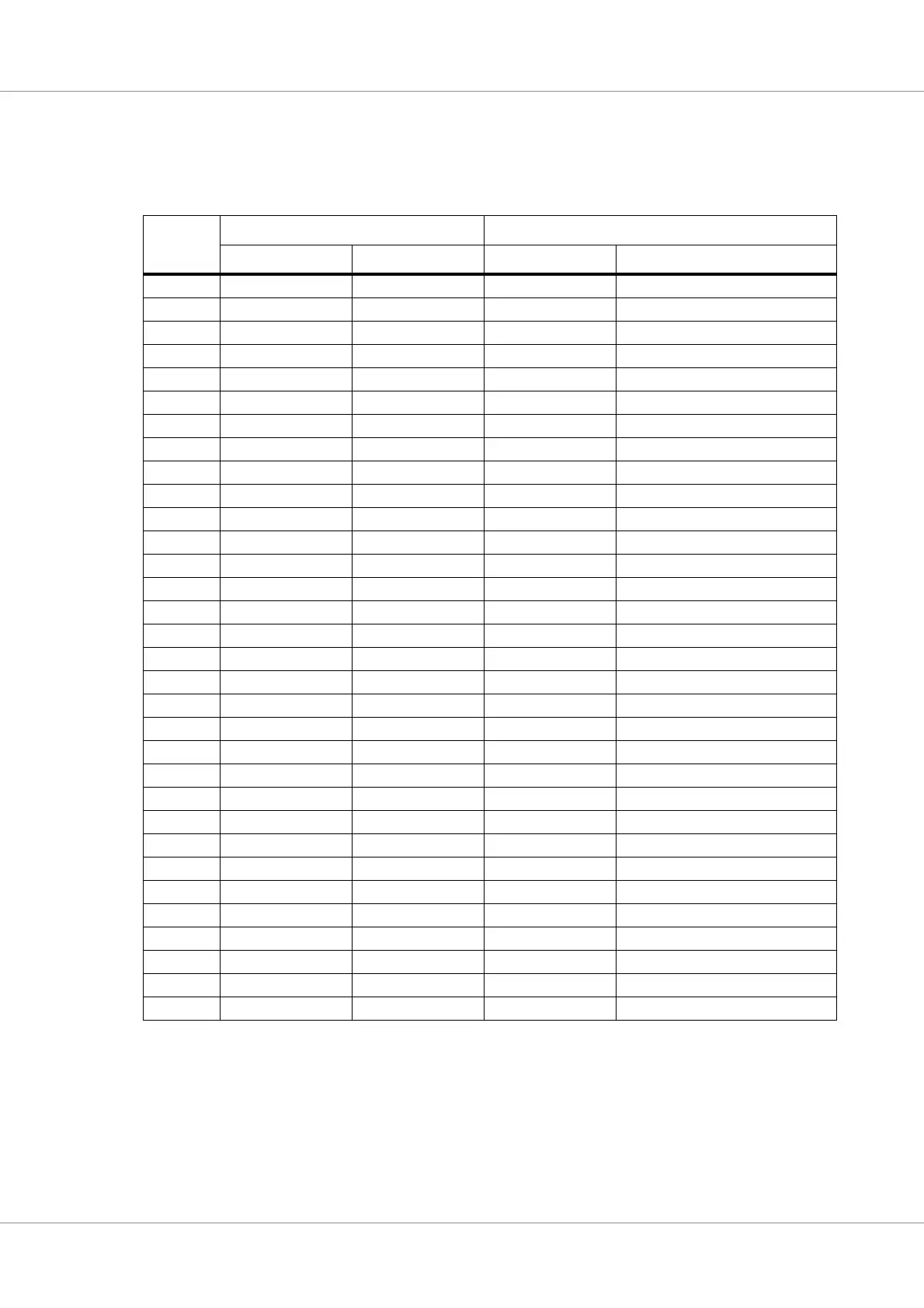

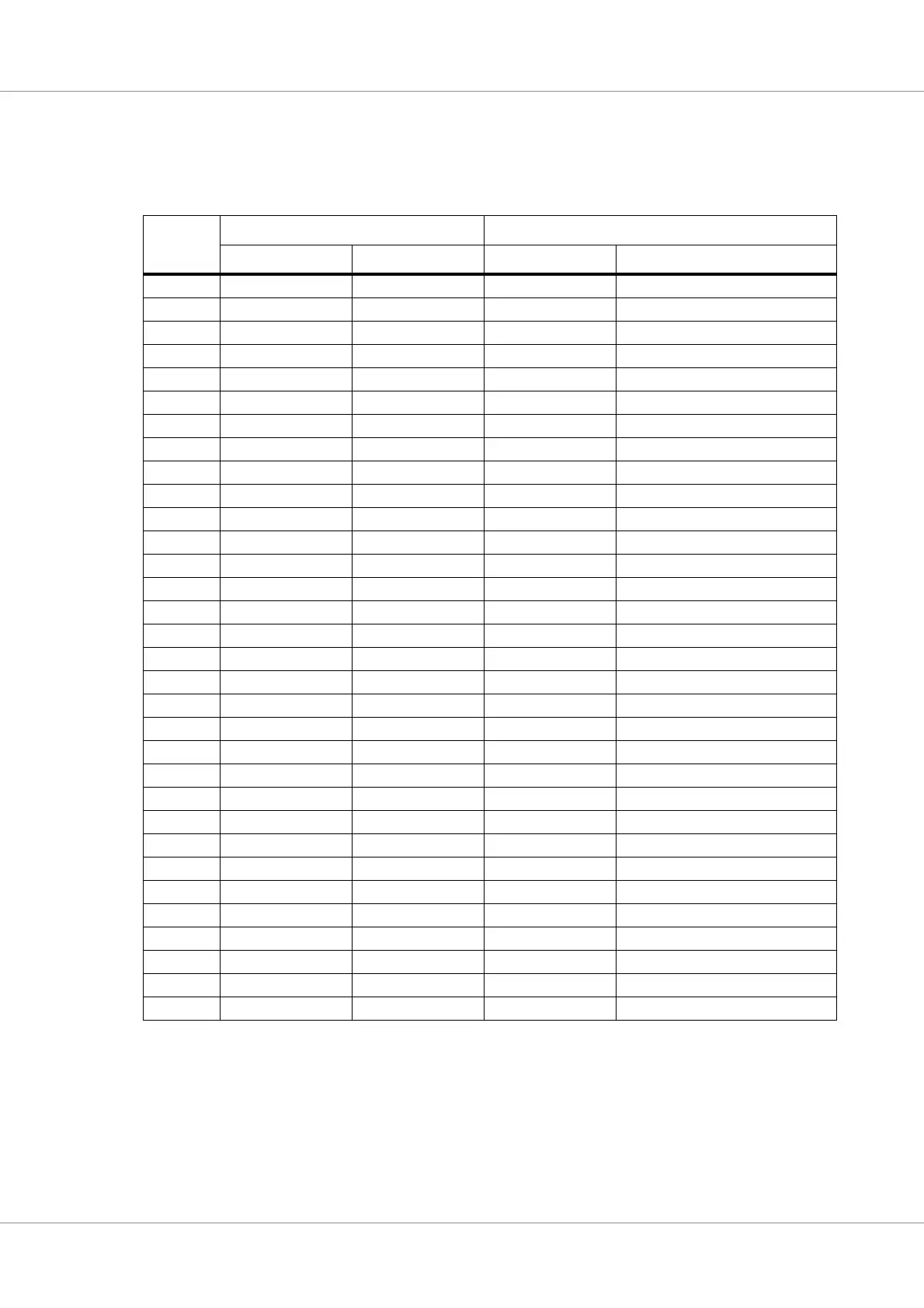

18.4.1 BasicCAN register map

Table 121.BasicCAN address allocation

Address Operating mode Reset mode

Read Write Read Write

0 Control Control Control Control

1 (0xFF) Command (0xFF) Command

2 Status - Status -

3 Interrupt - Interrupt -

4 (0xFF) - Acceptance code Acceptance code

5 (0xFF) - Acceptance mask Acceptance mask

6 (0xFF) - Bus timing 0 Bus timing 0

7 (0xFF) - Bus timing 1 Bus timing 1

8 (0x00) - (0x00) -

9 (0x00) - (0x00) -

10 TX id1 TX id1 (0xFF) -

11 TX id2, rtr, dlc TX id2, rtr, dlc (0xFF) -

12 TX data byte 1 TX data byte 1 (0xFF) -

13 TX data byte 2 TX data byte 2 (0xFF) -

14 TX data byte 3 TX data byte 3 (0xFF) -

15 TX data byte 4 TX data byte 4 (0xFF) -

16 TX data byte 5 TX data byte 5 (0xFF) -

17 TX data byte 6 TX data byte 6 (0xFF) -

18 TX data byte 7 TX data byte 7 (0xFF) -

19 TX data byte 8 TX data byte 8 (0xFF) -

20 RX id1 - RX id1 -

21 RX id2, rtr, dlc - RX id2, rtr, dlc -

22 RX data byte 1 - RX data byte 1 -

23 RX data byte 2 - RX data byte 2 -

24 RX data byte 3 - RX data byte 3 -

25 RX data byte 4 - RX data byte 4 -

26 RX data byte 5 - RX data byte 5 -

27 RX data byte 6 - RX data byte 6 -

28 RX data byte 7 - RX data byte 7 -

29 RX data byte 8 - RX data byte 8 -

30 (0x00) - (0x00) -

31 Clock divider Clock divider Clock divider Clock divider

Loading...

Loading...