GR712RC-UM, Jun 2017, Version 2.9 71 www.cobham.com/gaisler

GR712RC

6.3 Registers

The on-chip RAM is configured through a configuration register mapped at address 0x80100000:

Table 35. FTAHBRAM registers

APB Address offset Register

0x80100000 Configuration Register

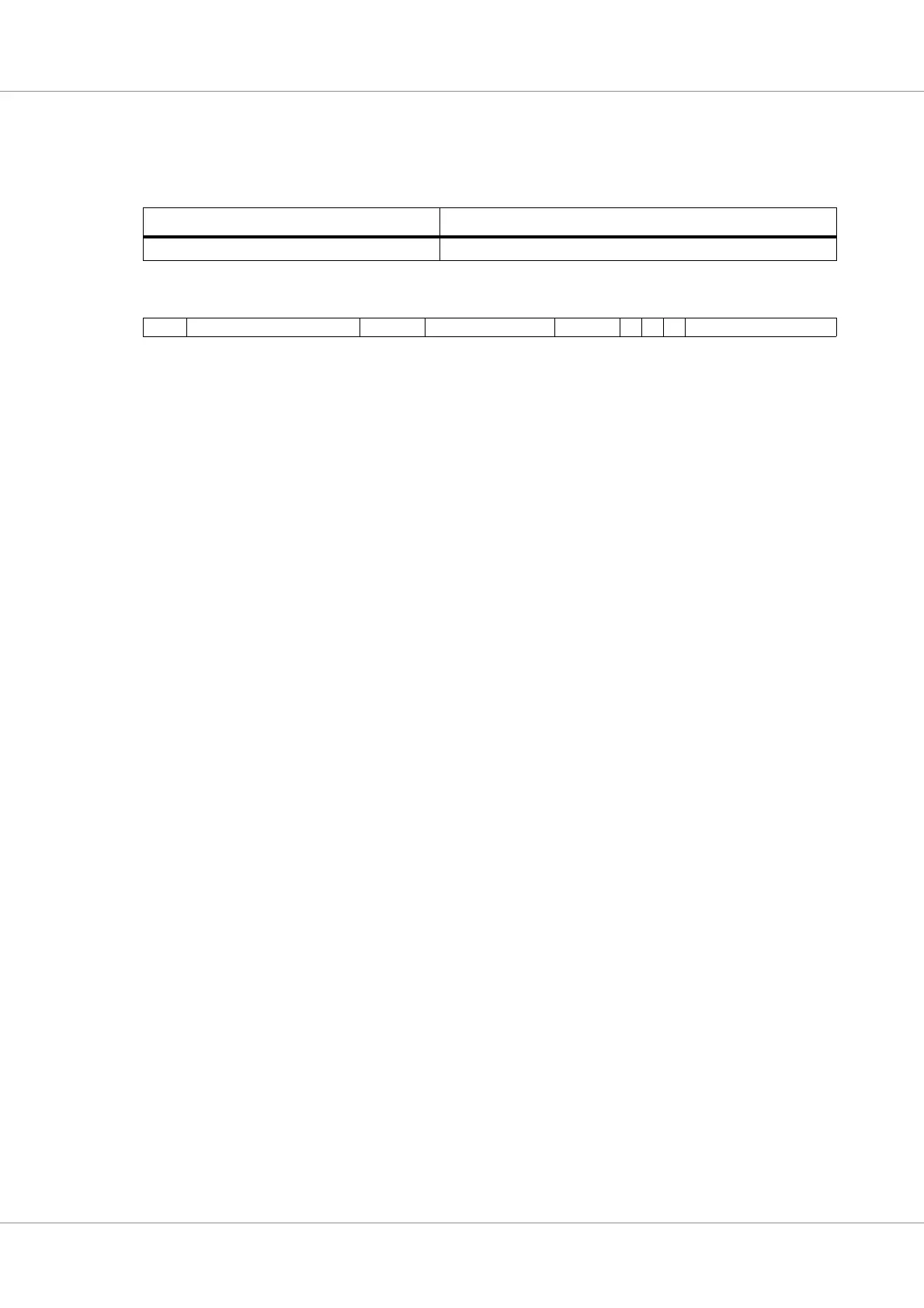

Table 36. Configuration Register

31 30 29 24 23 21 20 13 12 10 9 8 7 6 0

DIAG MEMSIZE SEC MEMSIZE WB RB EN TCB

31: 30 RAM timing adjust. Must be written with “00”.

23 21 3 MSB bits of log2 of the memory size (read-only). Hardcoded to “001”.

20: 13 Single error counter (SEC): Incremented each time a single error is corrected (includes errors on

checkbits). Each bit can be set to zero by writing a one to it.

12: 10 3 LSB bits of log2 of the memory size (read-only). Hardcoded to “000”.

9 Write Bypass (WB): When set, the TCB field is stored as check bits when a write is performed to the

memory.

8 Read Bypass (RB): When set during a read or subword write, the check bits loaded from memory are

stored in the TCB field.

7 EDAC Enable (EN): When set, the EDAC is used otherwise it is bypassed during read and write

operations.

6: 0 Test Check Bits (TCB): Used as checkbits when the WB bit is set during writes and loaded with the

check bits during a read operation when the RB bit is set.

Any unused most significant bits are reserved. Always read as ‘000...0’.

All fields except TCB are initialized to 0 at reset.

Loading...

Loading...