GR712RC-UM, Jun 2017, Version 2.9 70 www.cobham.com/gaisler

GR712RC

6 On-chip Memory with EDAC Protection

6.1 Overview

The GR712RC is provided with 192 KiB on-chip RAM, based on the FTAHBRAM core from

GRLIB. The RAM is protected with an error detection and correction unit (EDAC), capable of cor-

recting one error per word, and detecting two errors per word. The on-chip memory is not cacheable.

6.2 Operation

The 192 KiB of on-chip memory is accessed through the AHB bus at address 0xA0000000 -

0xA0030000. The configuration register is accessible via the APB bus at address 0x80100000.

The on-chip RAM implements a general-purpose storage and can be accessed by any AHB master.

The on-chip RAM can be protected against soft errors by enabling the EDAC protection in the config-

uration register. When enabled, the EDAC will transparently correct any single-bit error, and return an

AHB error response in case of an uncorrectable multi-bit error.

If EDAC is enabled by setting the EN bit in configuration register. When enabled for the first time

after reset, the full RAM contents should be written with a pre-defined value to initialize the EDAC

checkbits using word (32-bit) writes.

Reads are performed with 3 AHB waitstates while (32-bit) writes are fully buffered and do not gener-

ate any waitstates. Sub-word writes require 4 waitstates.

Note: the FTAHBRAM is not cached in the L1 caches of the LEON3FT processor(s). It is therefore

better suited to be used for data buffers than containing program instructions. If the processors exe-

cutes out of the FTAHBRAM, the performance is typically 0.25 MIPS/MHz.

6.2.1 EDAC checkbits diagnostic access

The EDAC checkbits can be accessed for diagnostic purposes using read and write bypass mode. In

read bypass mode, the checkbits are stored in the TCB field of the configuration register after each

read to the RAM. In write bypass mode, the checkbits in the RAM array are written with the value of

the TCB field instead of the automatically calculated checkbits. The bypass modes can be enabled by

setting the RB and/or WB bits in the configuration register.

6.2.2 Error reporting

An 8-bit single error counter (SEC) field is available in the configuration register. It is incremented

each time a single data bit error is encountered (reads or subword writes), saturation at 255. The

counter can be reset by writing the value 255 to it. A single-error will also be reported in the AHB sta-

tus register, see section 7 for details.

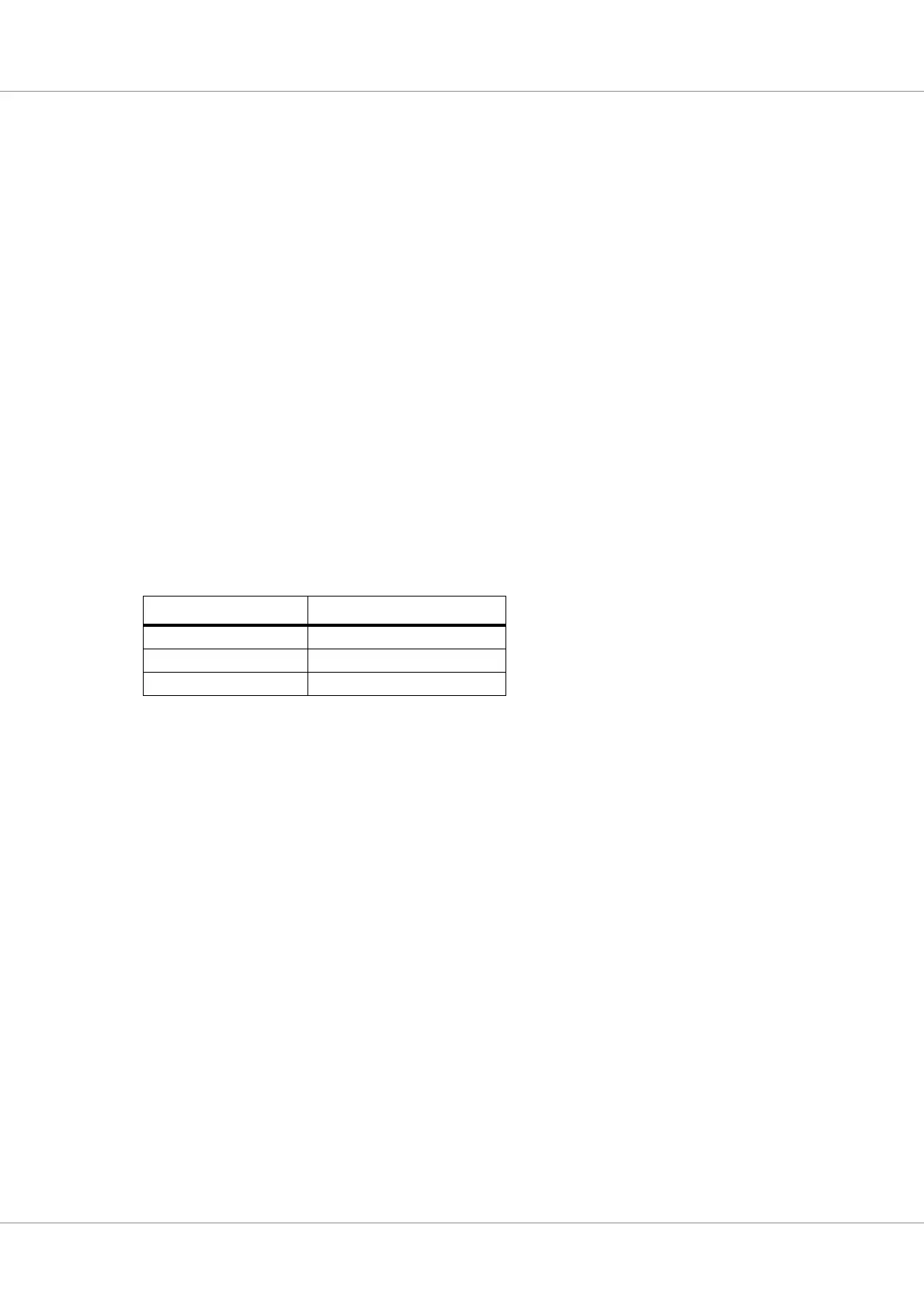

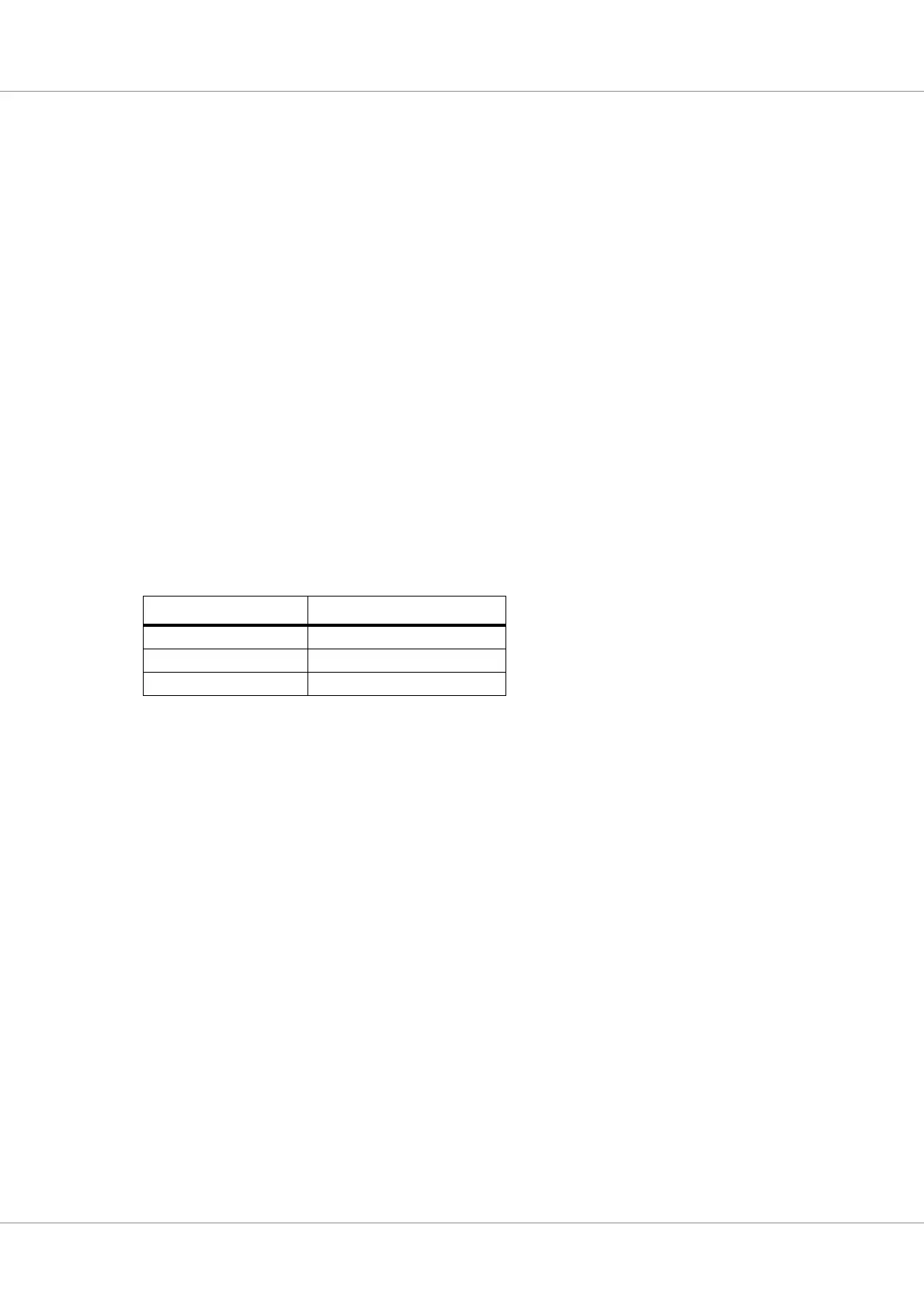

Table 34. Summary of the number of waitstates for the different operations for the memory.

Operation Waitstates

Read 3

Word write 0

Subword write 4

Loading...

Loading...