GR712RC-UM, Jun 2017, Version 2.9 64 www.cobham.com/gaisler

GR712RC

c

0,10

= DATA[23:20]

c

1,10

= DATA[19:16]

c

0,11

= DATA[15:12]

c

1,11

= DATA[11:8]

c

0,12

= DATA[7:4]

c

1,12

= DATA[3:0]

c

0,13

= CB[15:12]

c

1,13

= CB[11:8]

c

0,14

= CB[7:4]

c

1,14

= CB[3:0]

5.10.3 EDAC Error reporting

An un-correctable EDAC error will results in an AHB error response. The initiating AHB master will

be notified of the error and take corresponding action. If the master was the LEON3FT processor, an

instruction or data error trap will be taken (see LEON3 section). The AHB error response will also be

registered in the AHB status register (see section 7). Correctable EDAC errors are amended on the fly

so that correct data is provided on the AHB bus, but data in memory is left unchanged. The presence

of a correctable error is howewer registered in the AHB Status register by raising the NE and CE flags

(see section 7). This information can be used for providing a scrubbing mechanism and/or error statis-

tics in software.

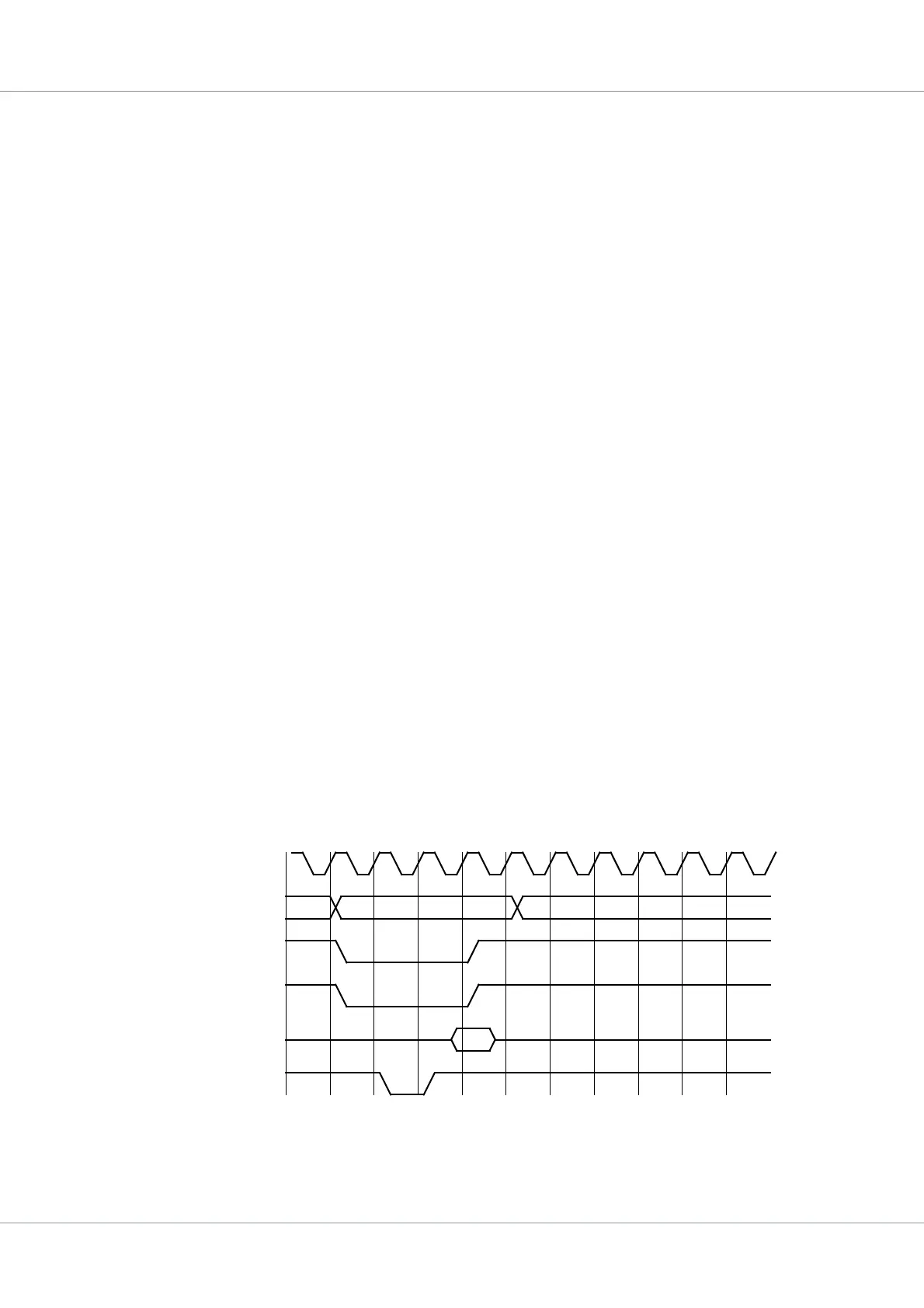

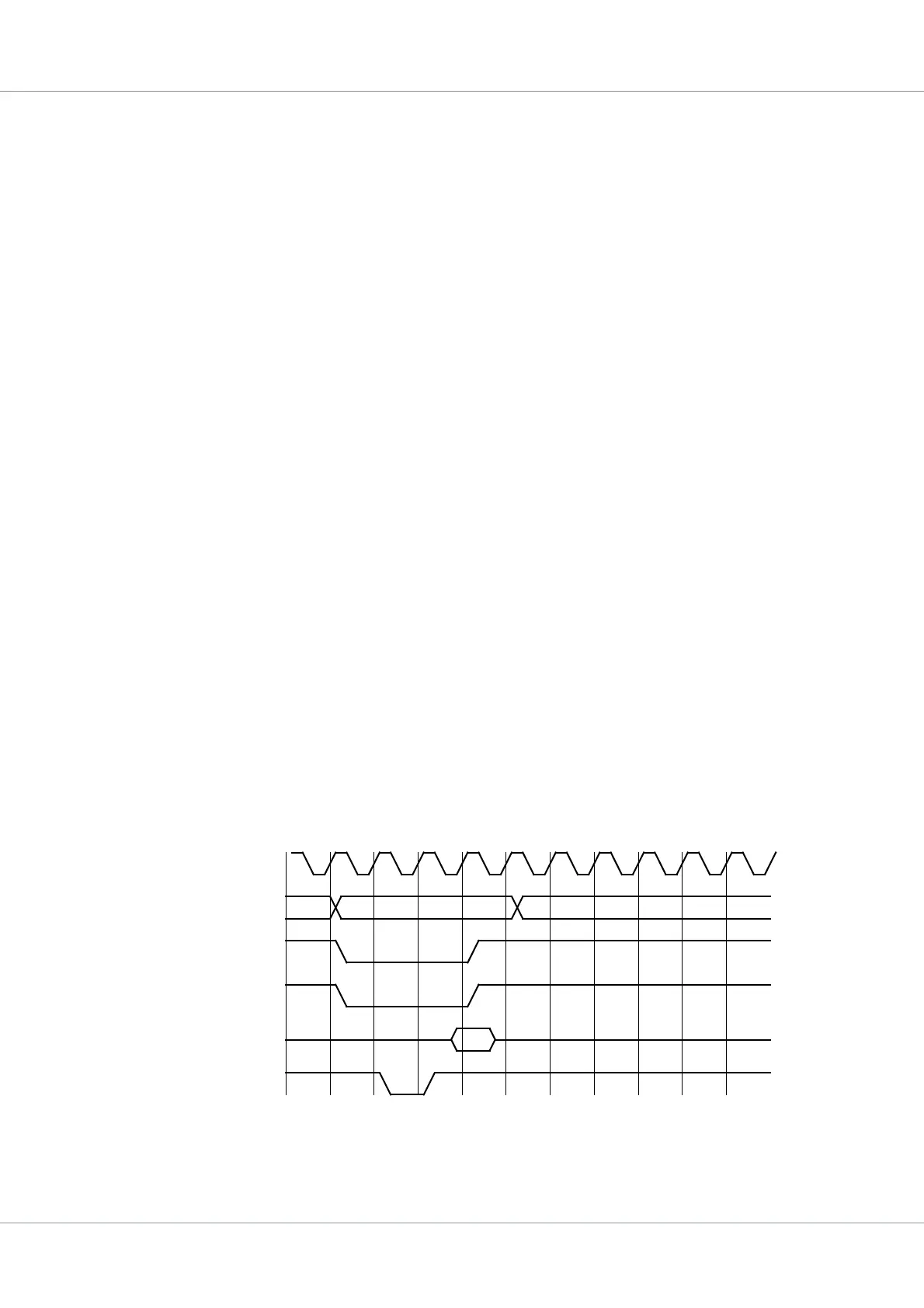

5.11 Bus Ready signalling

The BRDYN signal can be used to stretch accesses to the PROM and I/O area. The accesses will

always have at least the pre-programmed number of waitstates as defined in memory configuration

registers 1, but will be further stretched until BRDYN is asserted. BRDYN should be asserted in the

cycle preceding the last one. If bit 29 in MCFG1 is set, BRDYN can be asserted asynchronously with

the system clock. In this case, the read data must be kept stable until the de-assertion of OEN and

BRDYN must be asserted for at least 1.5 clock cycle. The use of BRDYN can be enabled separately

for the PROM and I/O areas. It is recommended that BRDYN is asserted until the corresponding chip

select signal is de-asserted, to ensure that the access has been properly completed and avoiding the

system to stall.

Figure 28 shows the use of BRDYN with asynchronous sampling. BRDYN is kept asserted for more

than 1.5 clock-cycle. Two synchronization registers are used so it will take at least one additional

Figure 27. READ cycle with one extra data2 cycle added with BRDYN (synchronous sampling). Lead-out cycle is only

applicable for I/O accesses.

data1 data2

address

romsn/iosn

data

oen

data2 lead-out

sdclk

D1

A1

brdyn

Loading...

Loading...