GR712RC-UM, Jun 2017, Version 2.9 122 www.cobham.com/gaisler

GR712RC

The SpaceWire transmitter uses SDR output registers meaning that the bitrate will be equal to the

transmit clock. The SpaceWire input signals are sampled synchronously with DDR registers using the

transmit clock. This allows the GR712RC to receive SpaceWire data at a bitrate equal to the transmit

clock.

16.9 Registers

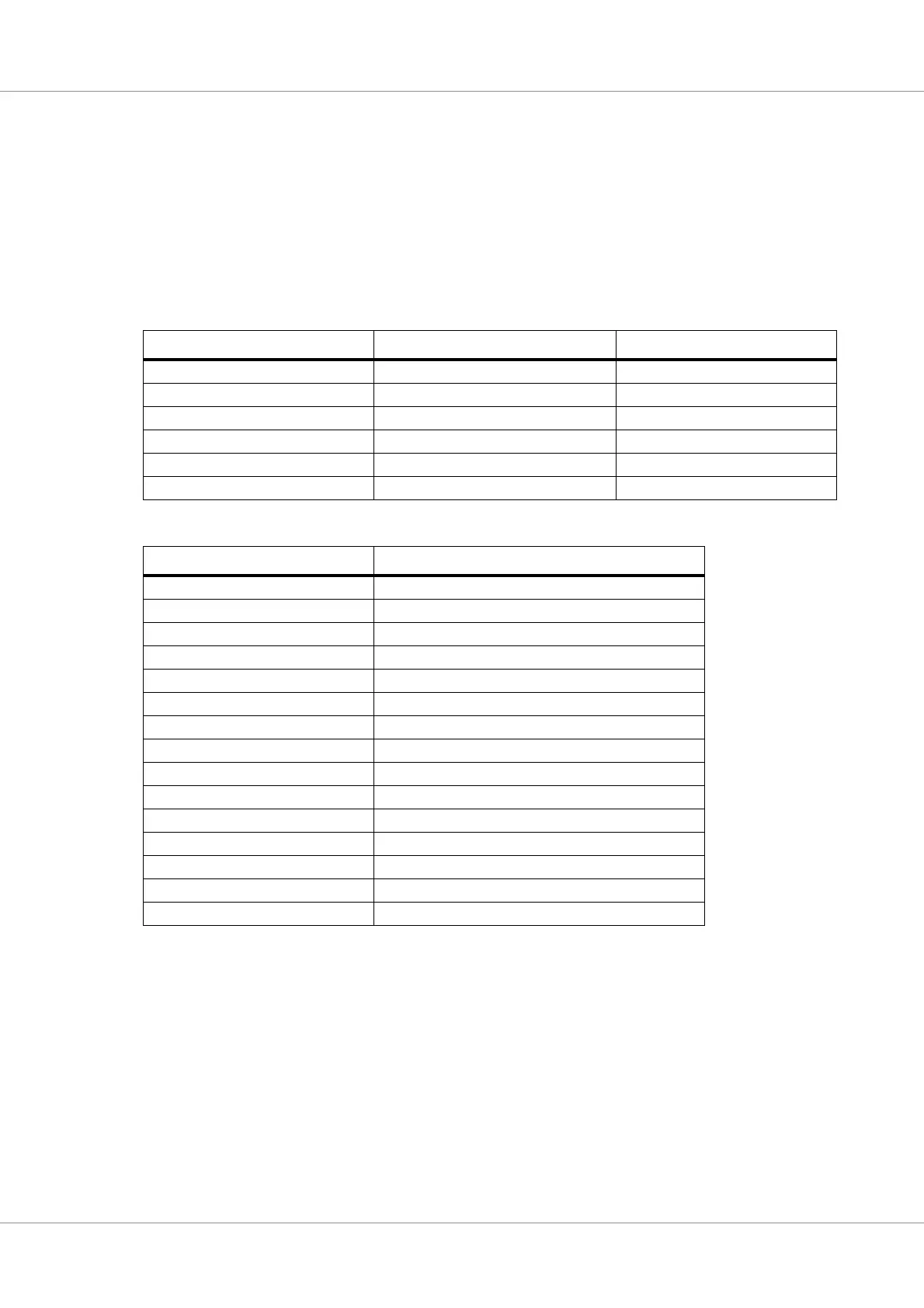

The core is programmed through registers mapped into APB address space.The table below shows the

base address and interrupt number for each GRSWP core.

Table 92. GRSPW core base addresses and interrupts

APB base address GRSWP core Interrupt

0x80100800 GRSPW2 - 0 22

0x80100900 GRSPW2 - 1 23

0x80100A00 GRSPW2 - 2 24

0x80100B00 GRSPW2 - 3 25

0x80100C00 GRSPW2 - 4 26

0x80100D00 GRSPW2 - 5 27

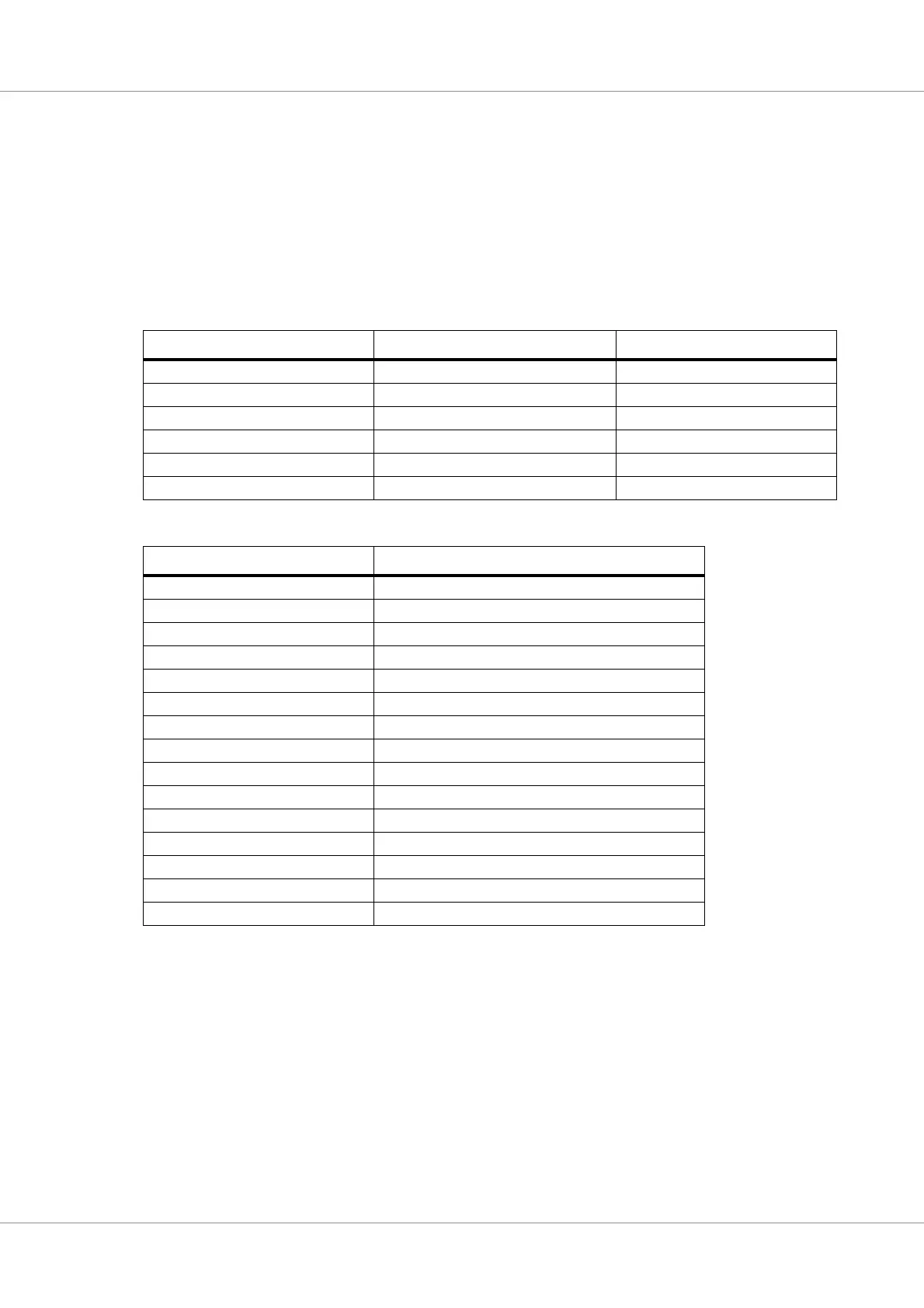

Table 93. GRSPW registers

APB address offset Register

0x0 Control

0x4 Status/Interrupt-source

0x8 Node address

0xC Clock divisor

0x10 Destination key

0x14 Time

0x20 DMA channel 1 control/status

0x24 DMA channel 1 rx maximum length

0x28 DMA channel 1 transmit descriptor table address.

0x2C DMA channel 1 receive descriptor table address.

0x30 DMA channel 1 address register

0x34 Unused

0x38 Unused

0x3C Unused

0x40 - 0x9C Unused

Loading...

Loading...