GR712RC-UM, Jun 2017, Version 2.9 78 www.cobham.com/gaisler

GR712RC

9 Hardware Debug Support Unit

9.1 Overview

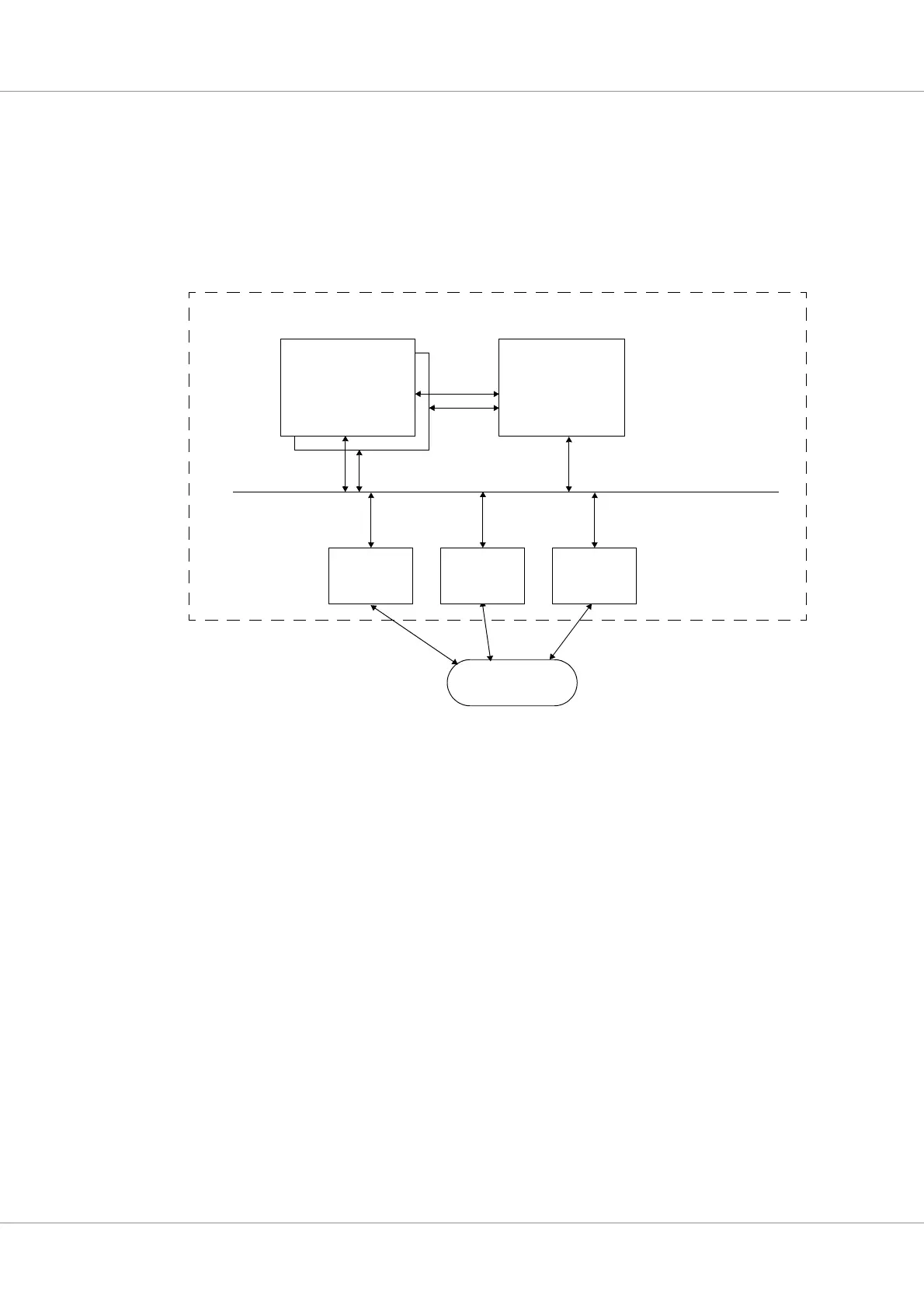

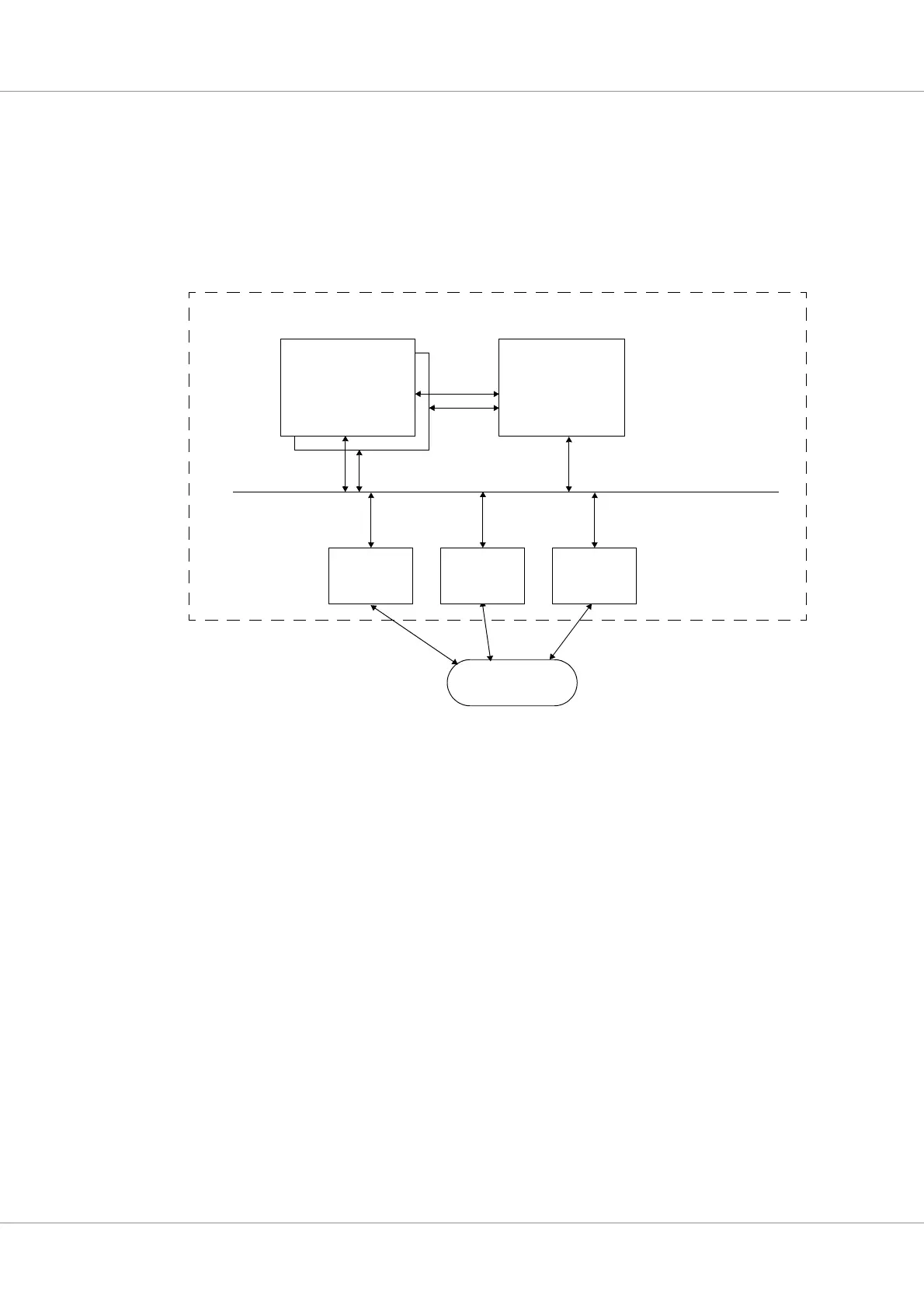

To simplify debugging on target hardware, the LEON3 processor implements a debug mode during

which the pipeline is idle and the processor is controlled through a Debug Support Unit (DSU). The

DSU acts as an AHB slave and can be accessed by any AHB master. In the GR712RC, an external

debug host can access the DSU through JTAG or SpaceWire links 0 and 1 (using RMAP).

9.2 Operation

Through the DSU AHB slave interface, the debug link AHB master can access the processor registers

and the contents of the instruction trace buffer. The DSU control registers can be accessed at any time,

while the processor registers, caches and trace buffer can only be accessed when the processor has

entered debug mode. In debug mode, the processor pipeline is held and the processor state can be

accessed by the DSU. Entering the debug mode can occur on the following events:

• executing a breakpoint instruction (ta 1)

• integer unit hardware breakpoint/watchpoint hit (trap 0xb)

• setting the break-now (BN) bits in the DSU break and single step register

• a trap that would cause the processor to enter error mode

• occurrence of any, or a selection of traps as defined in the DSU control register

• after a single-step operation

• one of the processors in a multiprocessor system has entered the debug mode

• DSU AHB breakpoint hit

When the debug mode is entered, the following actions are taken:

• PC and nPC are saved in temporary registers (accessible by the debug unit)

• the timer unit is (optionally) stopped to freeze the LEON timers and watchdog

Processor(s)

LEON3

Processor(s)

LEON3

Unit

AMBA AHB BUS

Debug Support

AHB Slave I/F

Debug I/F

AHB Master I/F

Figure 42. LEON3/DSU Connection

SpaceWire 1

DEBUG HOST

JTAGSpaceWire 0

with GRMON

Loading...

Loading...