GR712RC-UM, Jun 2017, Version 2.9 163 www.cobham.com/gaisler

GR712RC

The final sequence illustrates how to write one byte to an I

2

C-slave which requires addressing. First

the slave is addressed and the memory location on the slave is transmitted. After the slave has

acknowledged the memory location the data to be written is transmitted without a generating a new

START condition:

1. Left-shift the I

2

C-device address one position and write the result to the transmit register. The

least significant bit of the transmit register (R/W) is set to ‘0’.

2. Generate START condition and send contents of transmit register by setting the STA and WR

bits in the command register.

3. Wait for interrupt or for TIP bit in the status register to go low.

4. Read RxACK bit in status register. If RxACK is low the slave has acknowledged the transfer,

proceed to step 5. If RxACK is set the device did not acknowledge the transfer, go to step 1.

5. Write the memory location to be written from the slave to the transmit register.

6. Set the WR bit in the command register.

7. Wait for interrupt, or for TIP bit in the status register to go low.

8. Read RxACK bit in the status register. RxACK should be low.

9. Write the data byte to the transmit register.

10. Set WR and STO in the command register to send the data byte and then generate a STOP

condition.

11. Wait for interrupt, or for TIP bit in the status register to go low.

12. Check RxACK bit in the status register. If the write succeeded the slave should acknowledge

the data byte transfer.

The example sequences presented here can be generally applied to I

2

C-slaves. However, some

devices may deviate from the protocol above, please consult the documentation of the I

2

C-slave in

question. Note that a software driver should also monitor the arbitration lost (AL) bit in the status reg-

ister.

22.3 Registers

The core is programmed through registers mapped into APB address space.

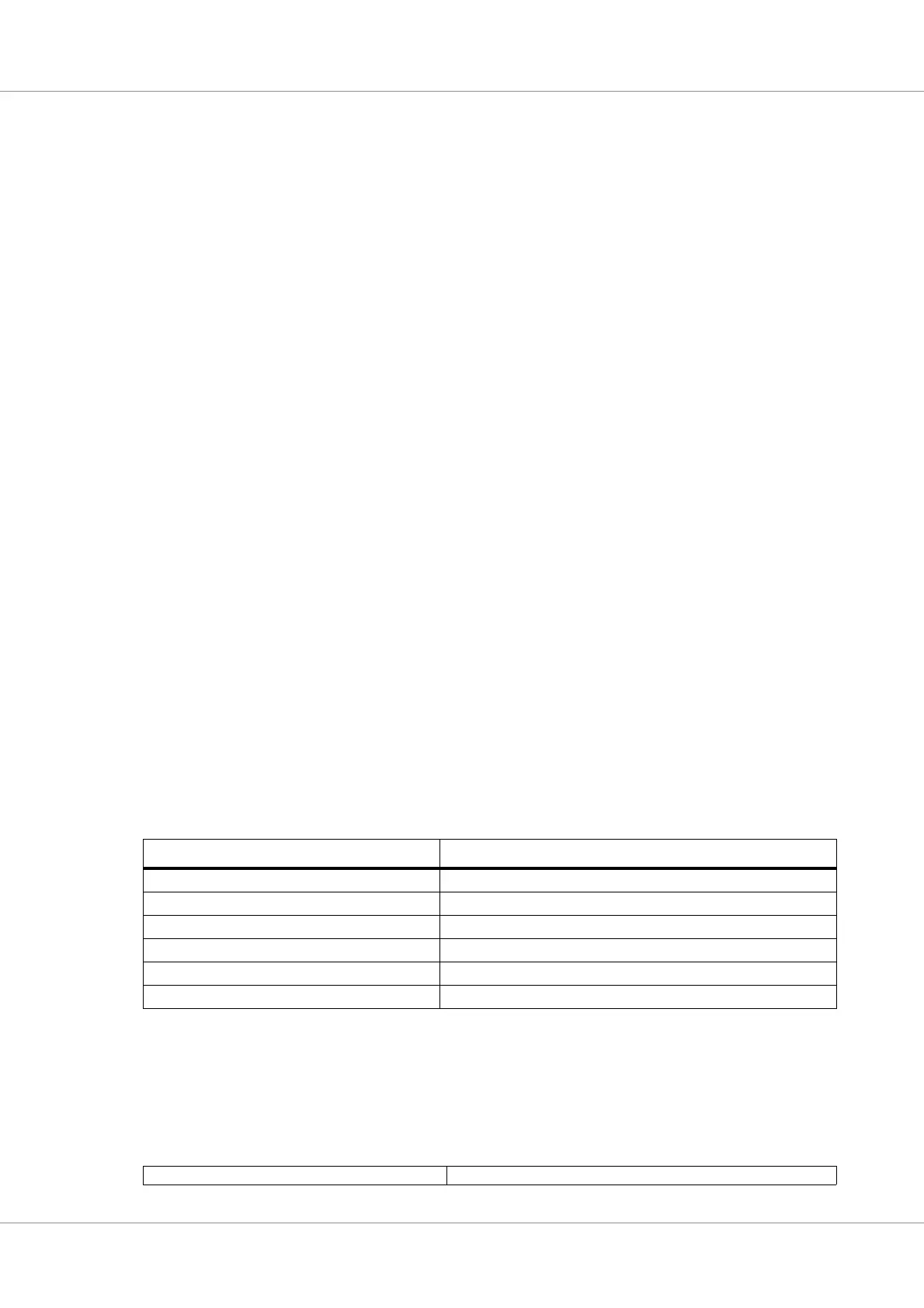

Table 164.I

2

C-master registers

APB address Register

0x80000C00 Clock prescale register

0x80000C04 Control register

0x80000C08 Transmit register*

0x80000C08 Receive register**

0x80000C0C Command register*

0x80000C0C Status register**

* Write only

** Read only

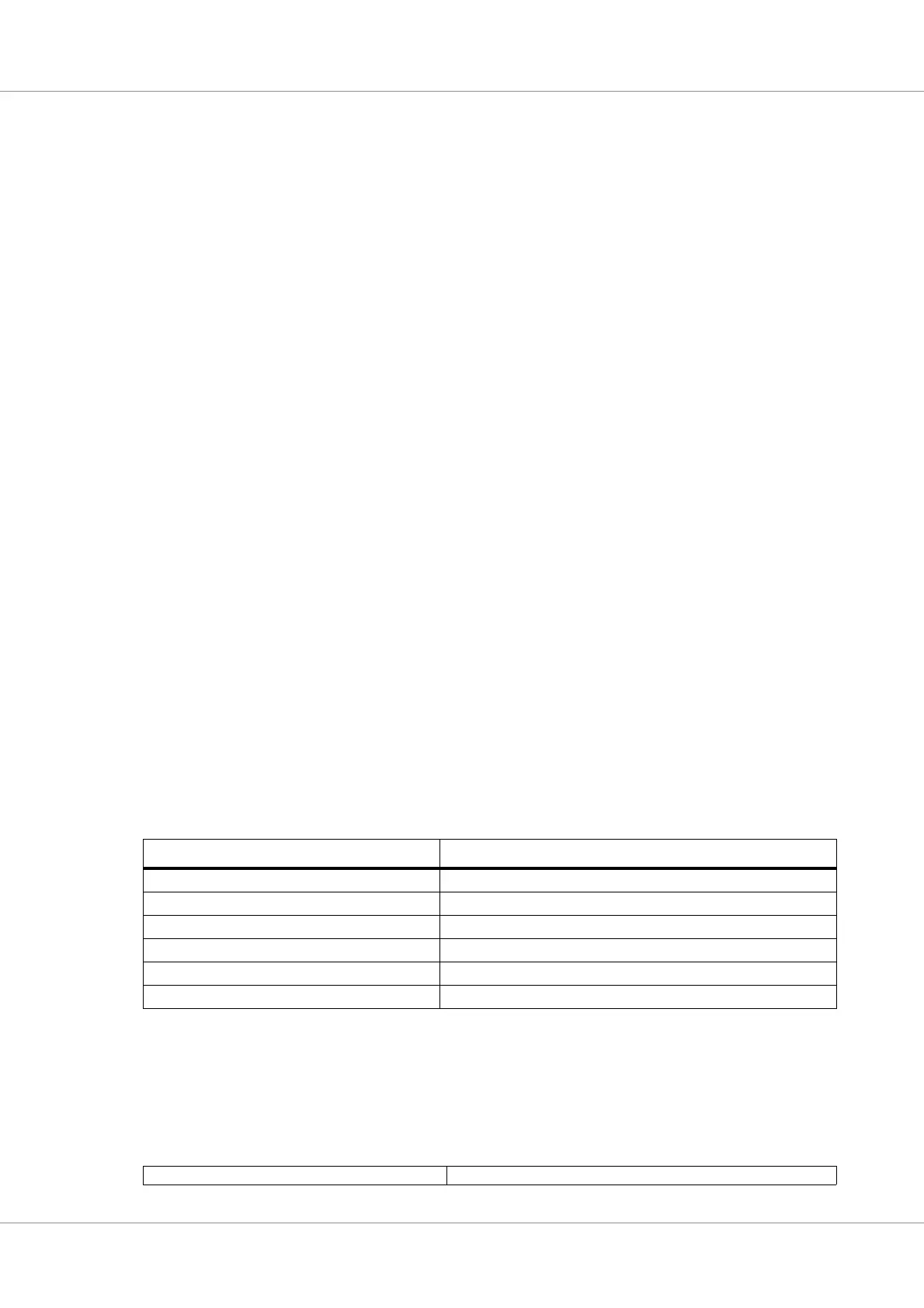

Table 165. I

2

C-master Clock prescale register

31 161576543210

RESERVED Clock prescale

Loading...

Loading...