GR712RC-UM, Jun 2017, Version 2.9 175 www.cobham.com/gaisler

GR712RC

Error Enable (PERRE) bit in the Mask register is set this event will cause an interrupt. The incoming

word may have been a response to an ongoing SEQUENCE operation or to a MASTER-WORD-

SEND READ transfer. Software should abort any ongoing SEQUENCE operation and possibly stop

waiting for the response to a READ operation when the core reports a parity error.

24.2.6 Clock and SYNC generation

To avoid multiple clock domains in the design the core generates the SCLK clock by dividing the sys-

tem clock. The clock divisor is selected by the fields CLKSCALEH and CLKSCALEL in the Clock

Scaler register. The SCLK frequency is calculated with the formula:

The CLKSCALEH determines the number of system clock cycles, plus one, that the SCLK clock is

kept HIGH and the CLKSCALEL value determines how many clock cycles, plus one, that the SCLK

clock is kept low. This scaling constrains the system clock frequency. To generate a 6 MHz, SCLK the

system clock frequency must be a multiple of 6 MHz. To attain a 6 MHz SCLK with 50/50 duty cycle,

the multiple must be dividable by two. The lowest possible system frequency that can be used to gen-

erate a 6 MHz clock is 12 MHz, with both scaler register fields set to zero:

The next frequency that will generate a SCLK clock with a 6 MHz period is a system clock of 18

MHz. This system frequency does not allow a SCLK clock with a 50/50 duty cycle.

24.3 Registers

The core is programmed through registers at address. 0x80000800

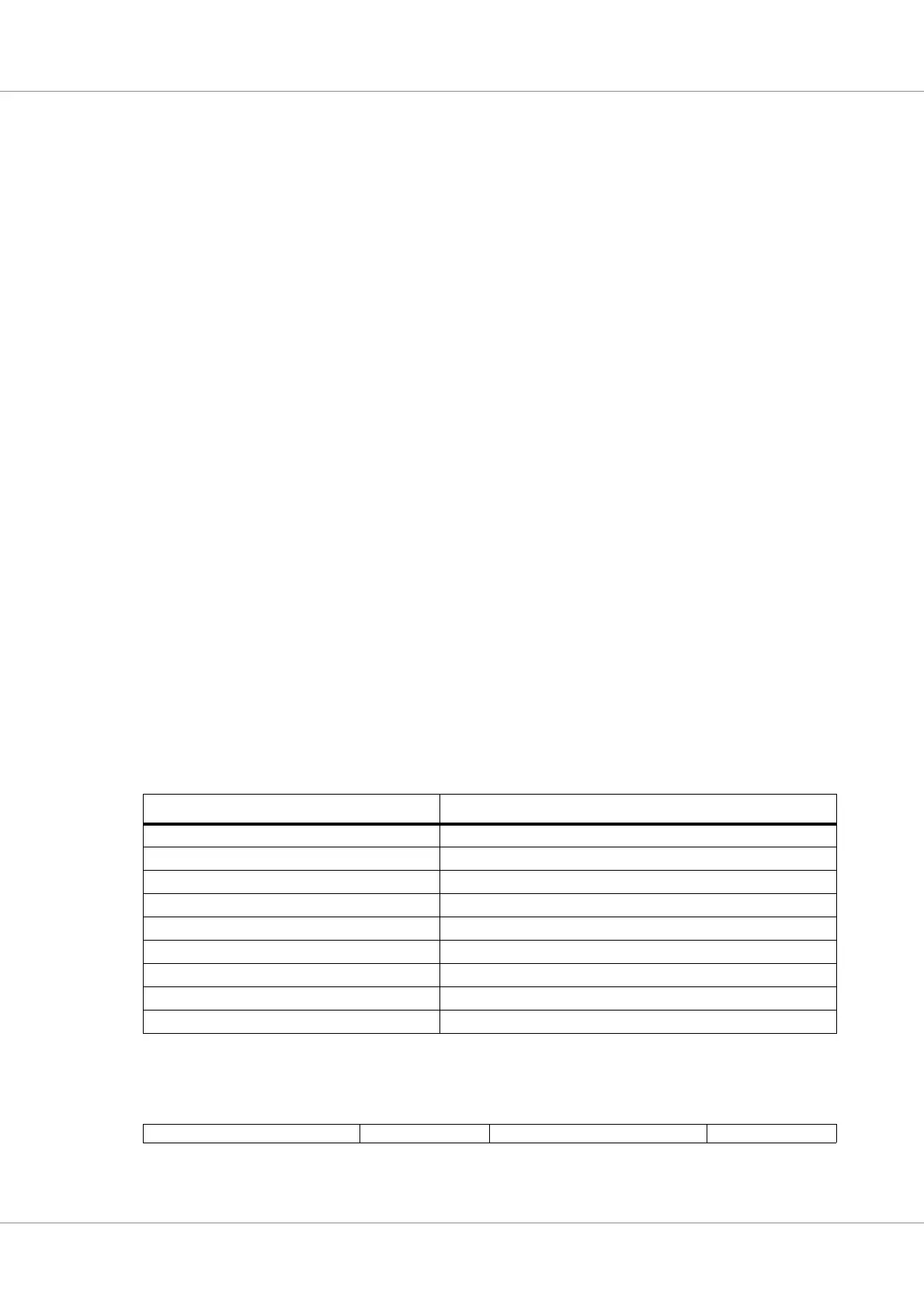

Table 185.GRSLINK registers

APB address offset Register

0x08000080 Clock Scaler register

0x80000804 Control register

0x80000808 NULL word register

0x8000080C Status register

0x80000810 IRQ mask register

0x80000814 Array A base address register

0x80000818 Array B base address register

0x8000081C Transmit register

0x80000820 Receive register

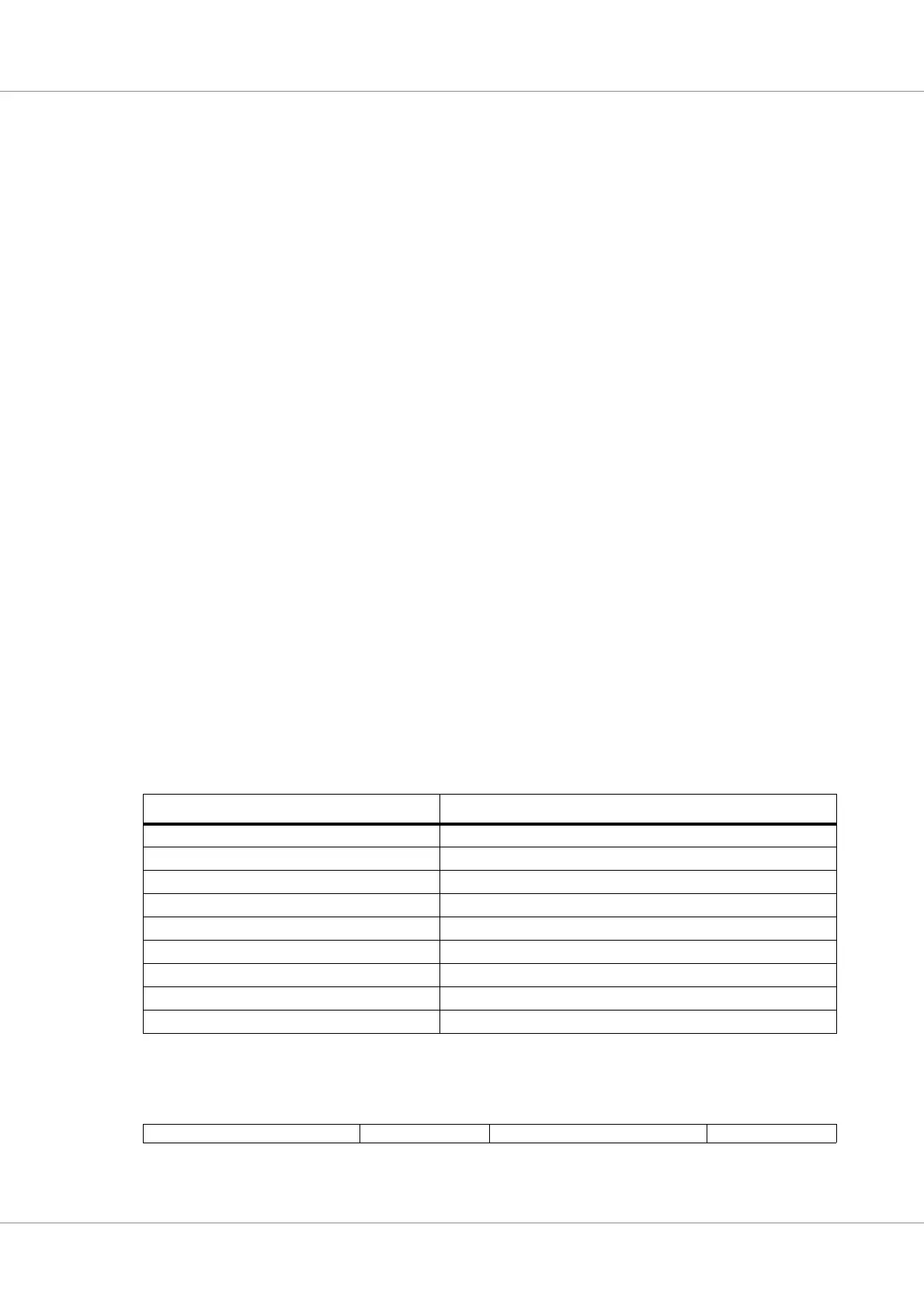

Table 186. GRSLINK Clock Scaler register

31 21 20 16 15 5 4 0

RESERVED CLKSCALEH RESERVED CLKSCALEL

31:21 RESERVED

SCLK

SystemClockFrequency

CLKSCALEH 1+CLKSCALEL 1++

---------------------------------------------------------------------------------------------------------------

=

SCLK

SystemClockFrequency

CLKSCALEH 1+CLKSCALEL 1++

---------------------------------------------------------------------------------------------------------------

12MHz

01+01++

---------------------------------------------

12MHz

2

------------------

6MHz====

Loading...

Loading...