GR712RC-UM, Jun 2017, Version 2.9 132 www.cobham.com/gaisler

GR712RC

The address word of the descriptor is never touched by the GRETH.

17.4.4 Reception with AHB errors

If an AHB error occurs during a descriptor read or data store, the Receiver AHB Error (RA) bit in the

status register will be set and the receiver is disabled. The current reception is aborted. The receiver

can be enabled again by setting the Receive Enable bit in the control register.

17.5 MDIO Interface

The MDIO interface provides access to PHY configuration and status registers through a two-wire

interface which is included in the RMII interface. The GRETH provided full support for the MDIO

interface.

The MDIO interface can be used to access from 1 to 32 PHY containing 1 to 32 16-bit registers. A

read transfer i set up by writing the PHY and register addresses to the MDIO Control register and set-

ting the read bit. This caused the Busy bit to be set and the operation is finished when the Busy bit is

cleared. If the operation was successful the Linkfail bit is zero and the data field contains the read

data. An unsuccessful operation is indicated by the Linkfail bit being set. The data field is undefined

in this case.

A write operation is started by writing the 16-bit data, PHY address and register address to the MDIO

Control register and setting the write bit. The operation is finished when the busy bit is cleared and it

was successful if the Linkfail bit is zero.

17.6 Reduced Media Independent Interfaces (RMII)

The GRETH is configured to use the Reduced Media Independent Interface (RMII) for interfacing the

external PHY. It uses 7 signals which are a subset of the MII signals. The table below shows the sig-

nals and their function.

17.7 Registers

The core is programmed through registers mapped into APB address space.

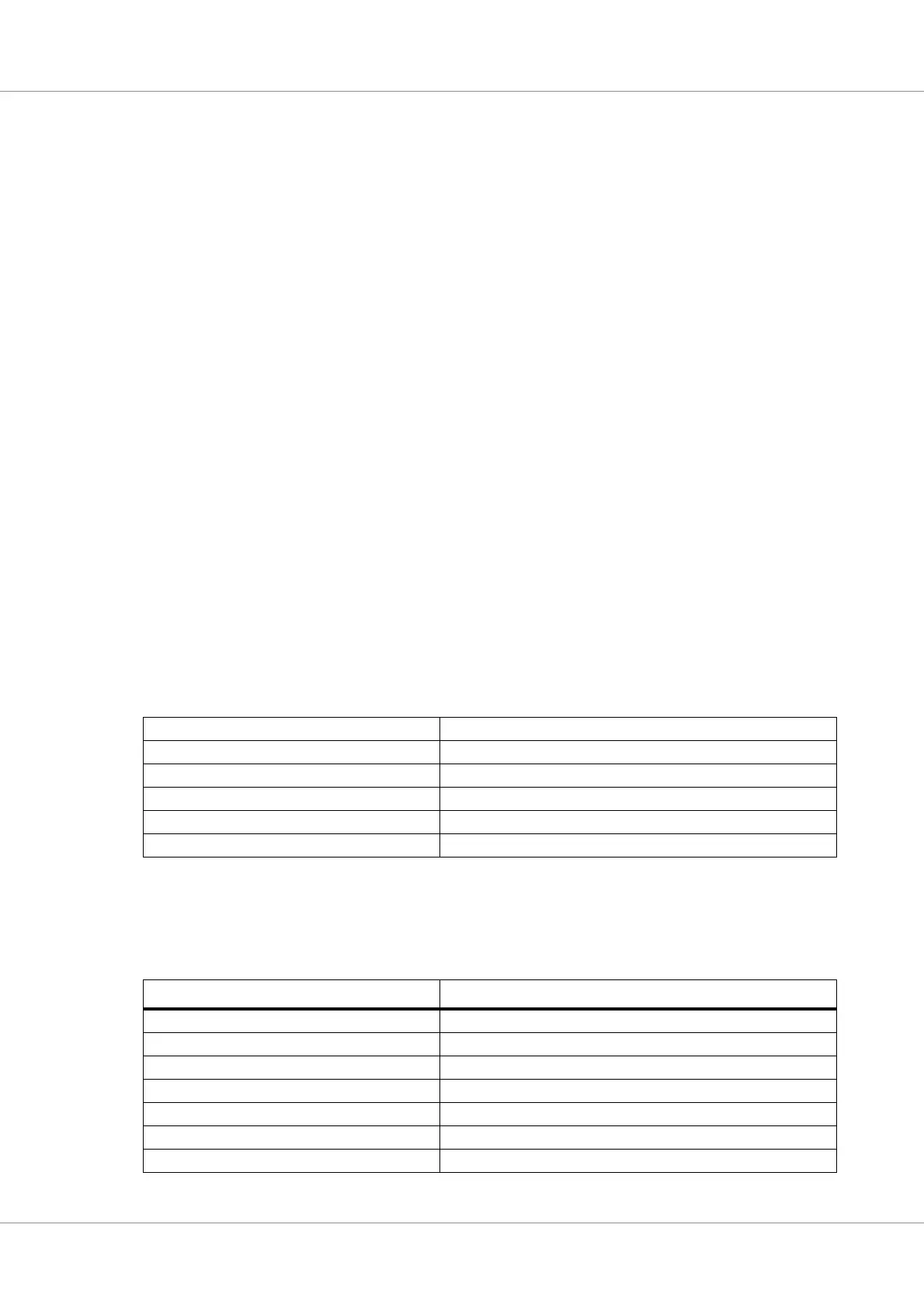

Table 110.RMII signals

Signal Function

RMTXD[1:0] Transmit data

RMTXEN

Transmit enable

RMCRSDV

Carrier sense and data valid

RMRXD[1:0] Receiver data

RMRFCLK

Reference clock (50 MHz)

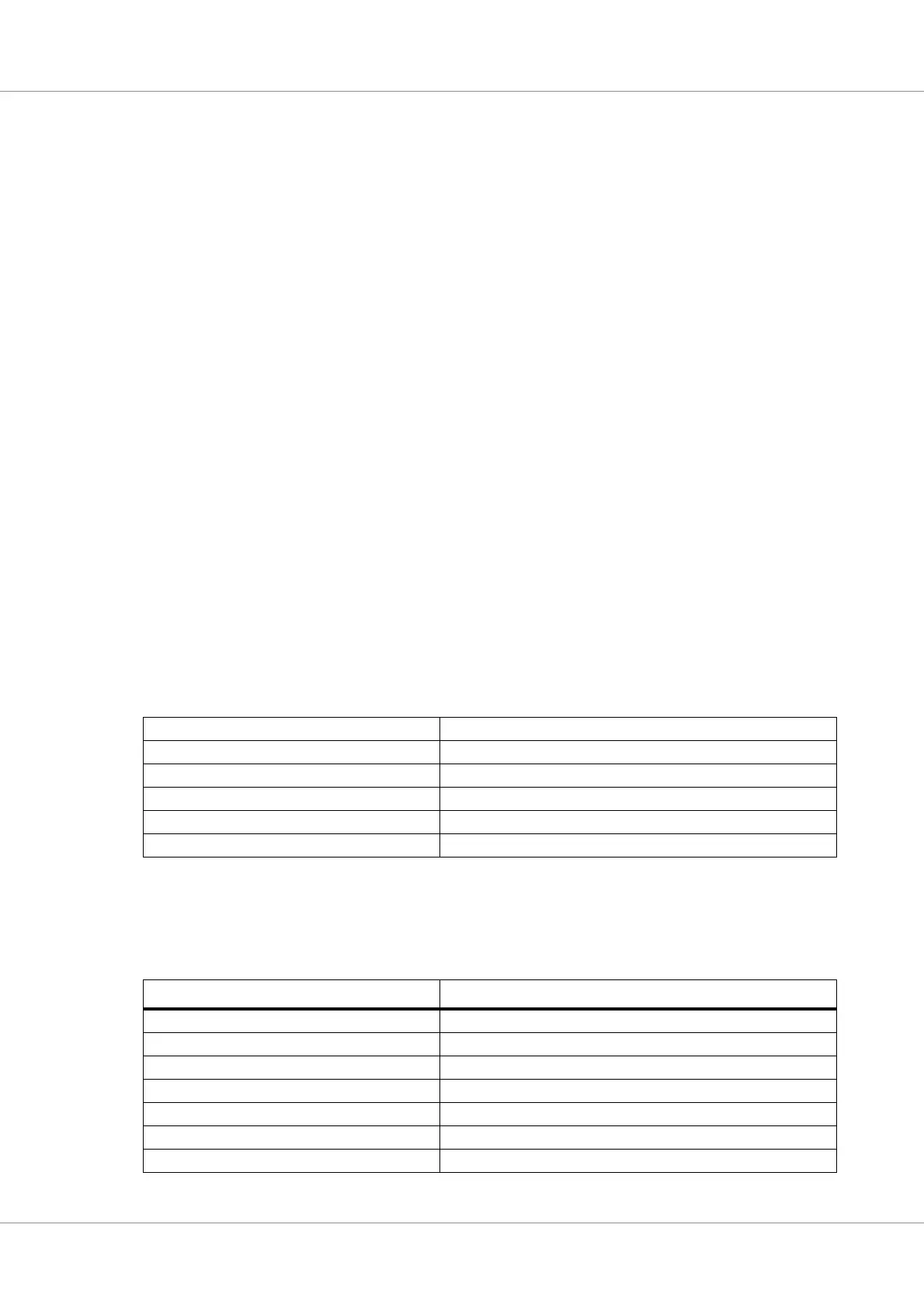

Table 111.GRETH registers

APB address Register

0x80000E00 Control register

0x80000E04 Status/Interrupt-source register

0x80000E08 MAC Address MSB

0x80000E0C MAC Address LSB

0x80000E10 MDIO Control/Status

0x80000E14 Transmit descriptor pointer

0x80000E18 Receiver descriptor pointer

Loading...

Loading...