GR712RC-UM, Jun 2017, Version 2.9 7 www.cobham.com/gaisler

GR712RC

1 Introduction

1.1 Scope

This document is a user’s manual for the radiation-hard GR712RC Dual-Core LEON3FT SPARC V8

processor. GR712RC is based on LEON3FT and IP cores from the GRLIB IP library, implemented

with the Ramon RadSafe

TM

180 nm cell library on Tower Semiconductors 180nm CMOS process.

1.2 GR712RC Architecture

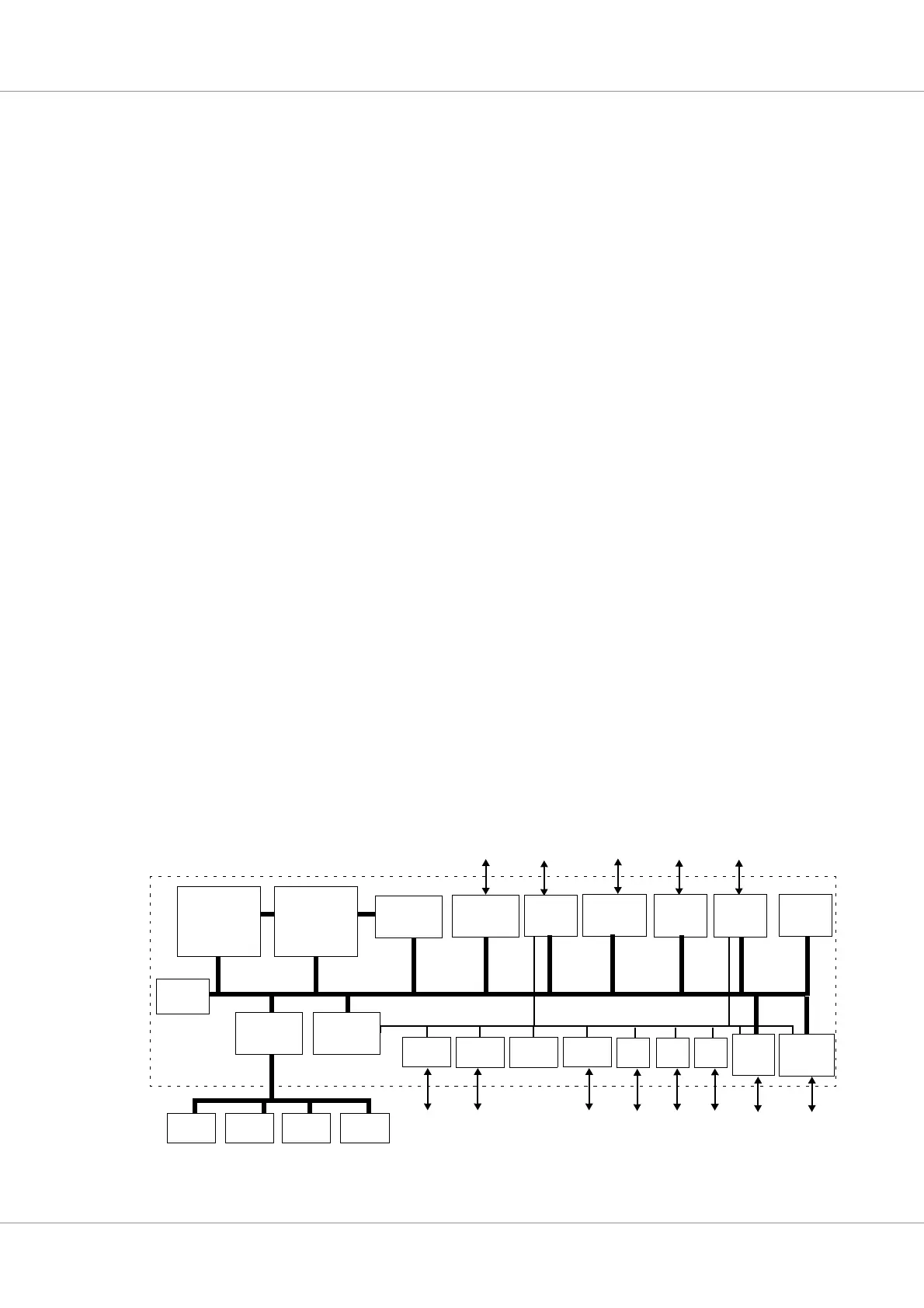

The GR712RC has the following on-chip features:

• 2 x LEON3FT processor cores with 32KiB cache and 32-entry TLB SRMMU

• 2 x Double-precision high-performance floating-point units (GRFPU V2)

• Debug Support Unit (DSU) with 256-line instruction and AMBA AHB trace buffers

• PROM/SRAM/SDRAM memory controller with BCH and Reed-Solomon error-correction

• up to 32 MiB PROM over two 16 MiB banks

• up to 32 MiB SRAM over two 16 MiB banks

• up to 1 GiB SDRAM over two 512 MiB banks

• 192 KiB on-chip RAM with BCH error-correction (uncacheable)

• 6 x SpaceWire links (two with RMAP support, one DMA channel per link, one port per link)

•6 x UARTs

• 6 x General Purpose Timers (2 with time latch capability)

• Multi-processor Interrupt Controller with support for 31 interrupts

• 2 x 32 bits General Purpose I/O

• JTAG debug link

• 10/100 Ethernet MAC with RMII interface

• MIL-STD-1553B BC/RT/BM controller

• 2 x CAN 2.0 controller

• High-speed CCSDS Telecommand decoder and Telemetry encoder

• SPI master controller

• I2C master controller

• SLINK and ASCS16 controllers

• Clock gating unit

• I/O switch matrix

AMBA AHB

Timers IrqCtrl

AMBA APB

SRAM

8/32-bits memory bus

Debug

Support Unit

SDRAMI/O

Memory

Controller

AHB/APB

Bridge

I/O port

6xUART

GPIO

SpaceWire

RS232

1553

1553

WDOGN

AHB

JTAG

Debug Link

6xSpW

JTAG

PROM

Ethernet

MAC

ETH PHY

CAN

2xCAN

TMTC

TM &

TC

BC/RT/BM

SLINK

SLINK

SPI

SPI

I2C

I2C

ASCS

ASCS16

LEON3FT

GR712RC Block diagram

LEON3FT

Control

RAM

192K

Loading...

Loading...