GR712RC-UM, Jun 2017, Version 2.9 56 www.cobham.com/gaisler

GR712RC

5.3 Memory mapped IO

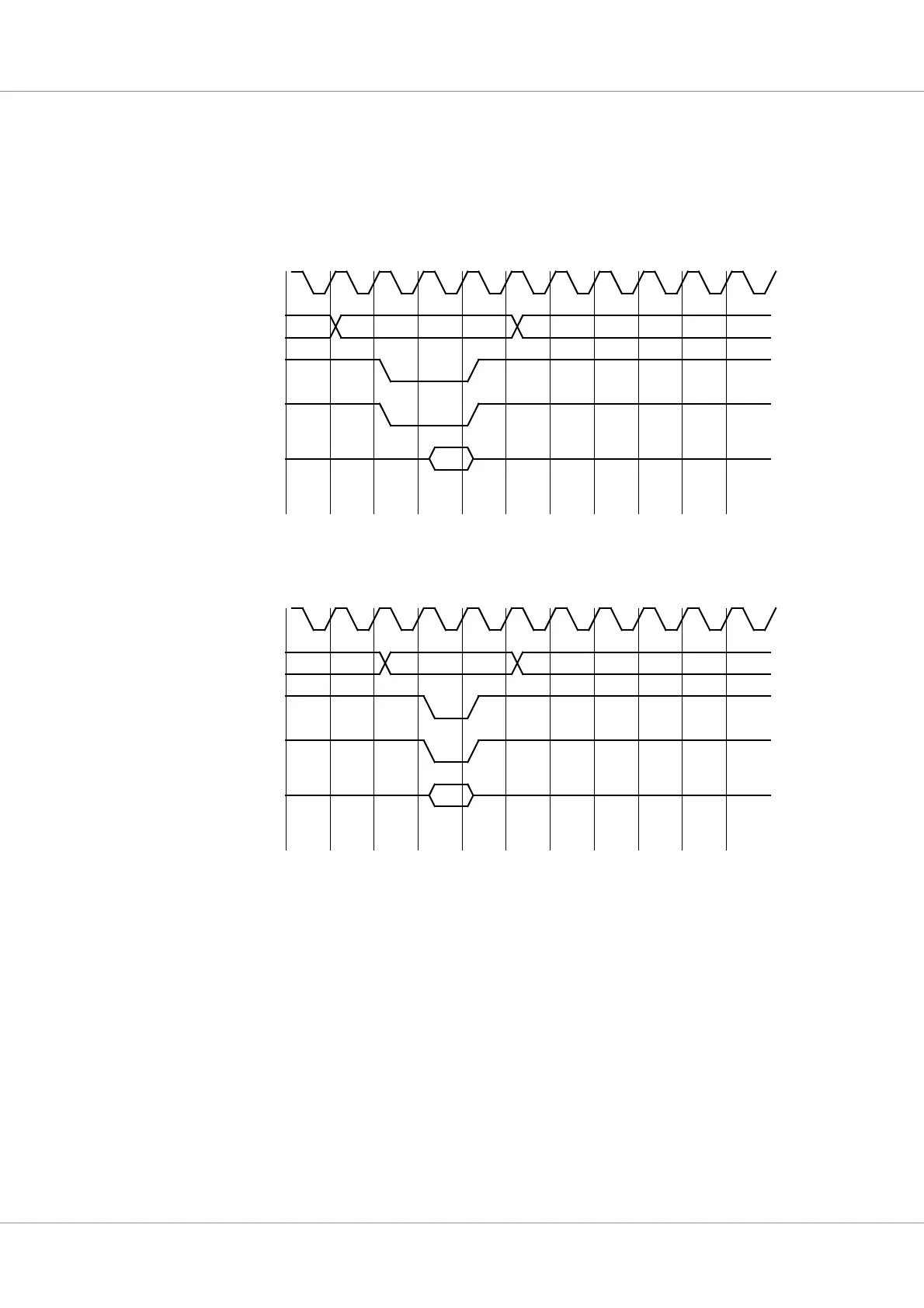

Accesses to IO have similar timing as PROM accesses. The IO select (IOSN) and output enable

(OEN) signals are delayed one clock to provide stable address before IOSN is asserted. All accesses

are performed as non-consecutive accesses as shown in figure 21. The data2 phase is extended when

waitstates are added.

Figure 21. I/O read cycle (0-waitstates)

data1

address

iosn

data

oen

lead-out

sdclk

A1

D1

lead-in data2

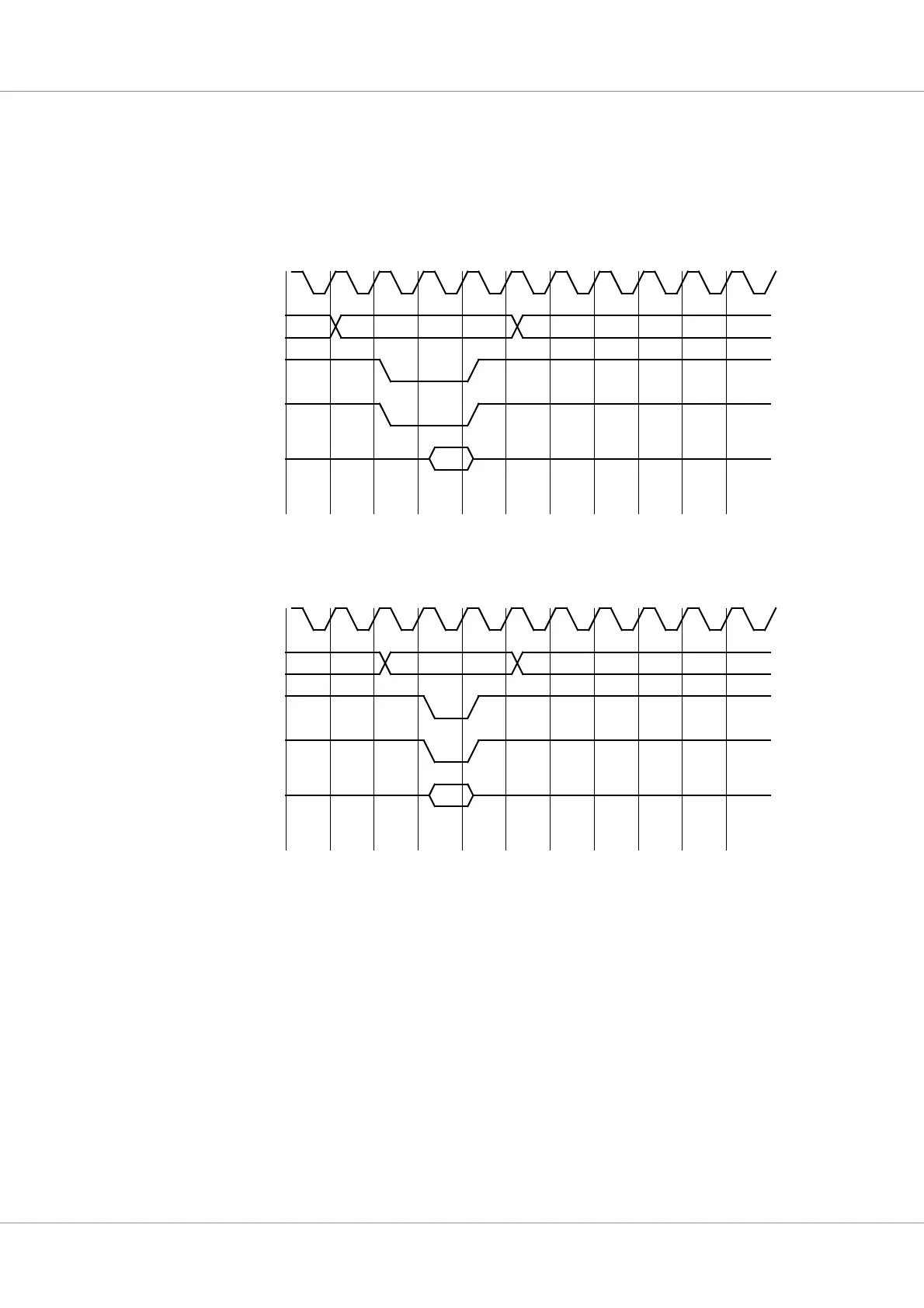

Figure 22. I/O write cycle (0-waitstates)

address

iosn

data

writen

lead-out

sdclk

A1

D1

lead-in

data

Loading...

Loading...