GR712RC-UM, Jun 2017, Version 2.9 75 www.cobham.com/gaisler

GR712RC

8.3 Registers

The core is controlled through registers mapped into APB address space. The number of implemented

registers depend on number of processor in the multiprocessor system.

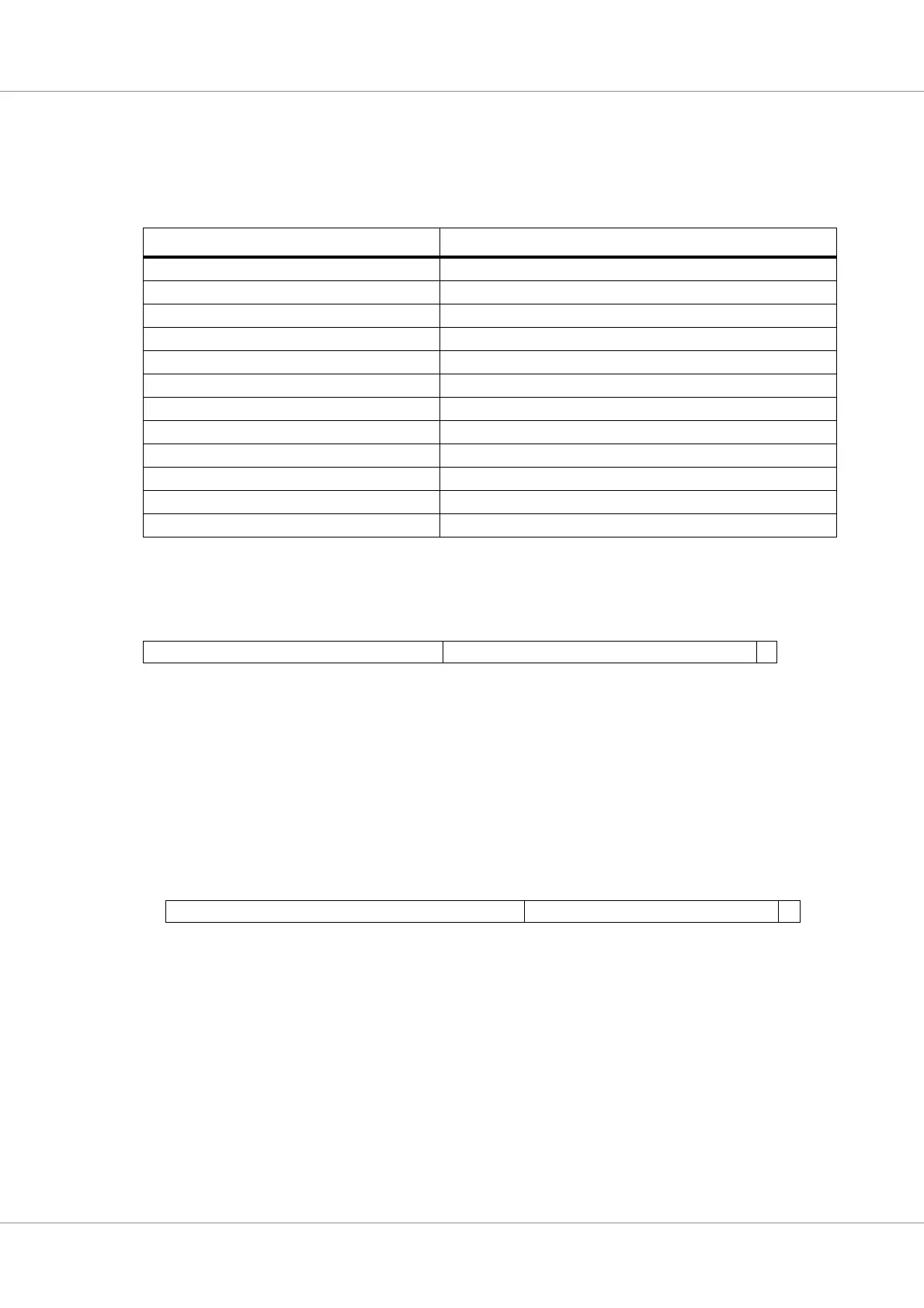

8.3.1 Interrupt level register

Figure 33. Interrupt level register

31

16

17

IL[15:1]

“000..0”

0

0

1

[31:16] Reserved.

[15:1] Interrupt Level n (IL[n]): Interrupt level for interrupt n.

[0] Reserved.

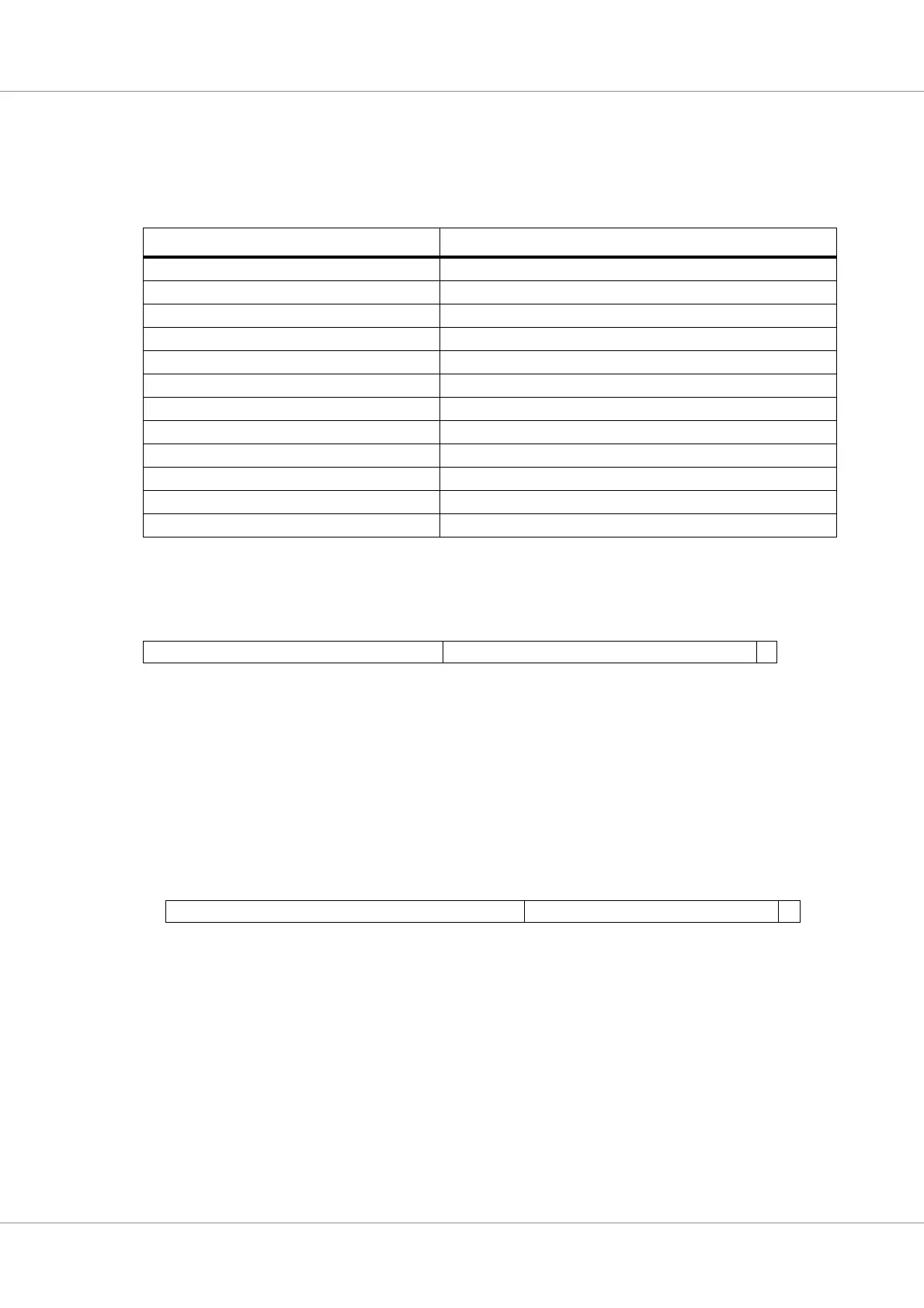

8.3.2 Interrupt pending register

Figure 34. Interrupt pending register

031

EIP[31:16]

0

15

IP[15:1]

16

1

[31:17] Extended Interrupt Pending n (EIP[n]).

[15:1] Interrupt Pending n (IP[n]): Interrupt pending for interrupt n.

[0] Reserved

Table 41. Interrupt Controller registers

APB address offset Register

0x80000200 Interrupt level register

0x80000204 Interrupt pending register

0x80000208 Interrupt force register, processor 0

0x8000020C Interrupt clear register

0x80000210 Multiprocessor status register

0x80000214 Broadcast register

0x80000240 Processor 0 interrupt mask register

0x80000244 Processor 1 interrupt mask register

0x80000280 Processor 0 interrupt force register

0x80000284 Processor 1 interrupt force register

0x800002C0 Processor 0 extended interrupt identification register

0x800002C4 Processor 1 extended interrupt identification register

Loading...

Loading...