GR712RC-UM, Jun 2017, Version 2.9 74 www.cobham.com/gaisler

GR712RC

cessor acknowledgement will clear the force bit rather than the pending bit. After reset, the interrupt

mask register is set to all zeros while the remaining control registers are undefined. Note that interrupt

15 cannot be maskable by the LEON3 processor and should be used with care - most operating sys-

tems do not safely handle this interrupt.

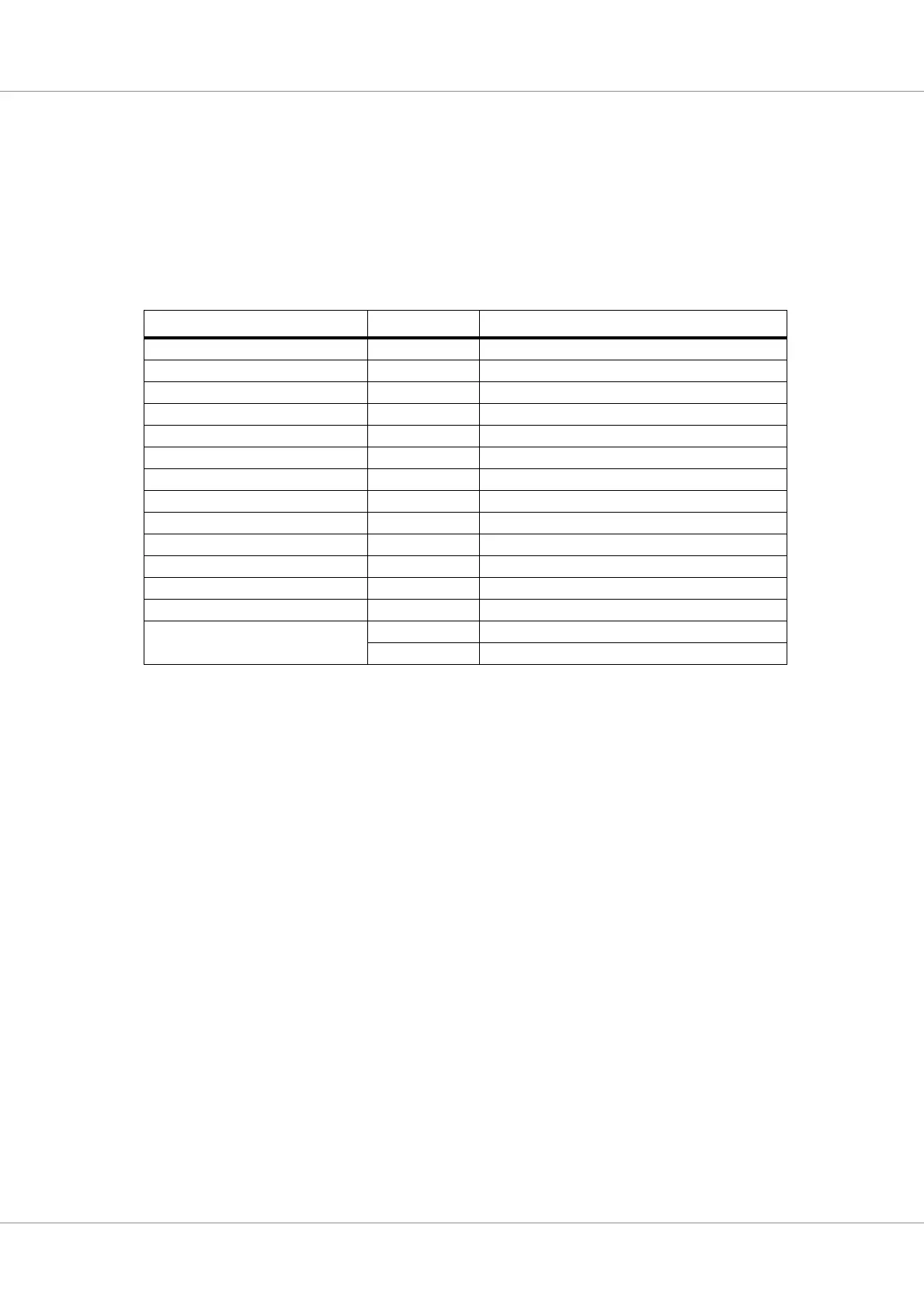

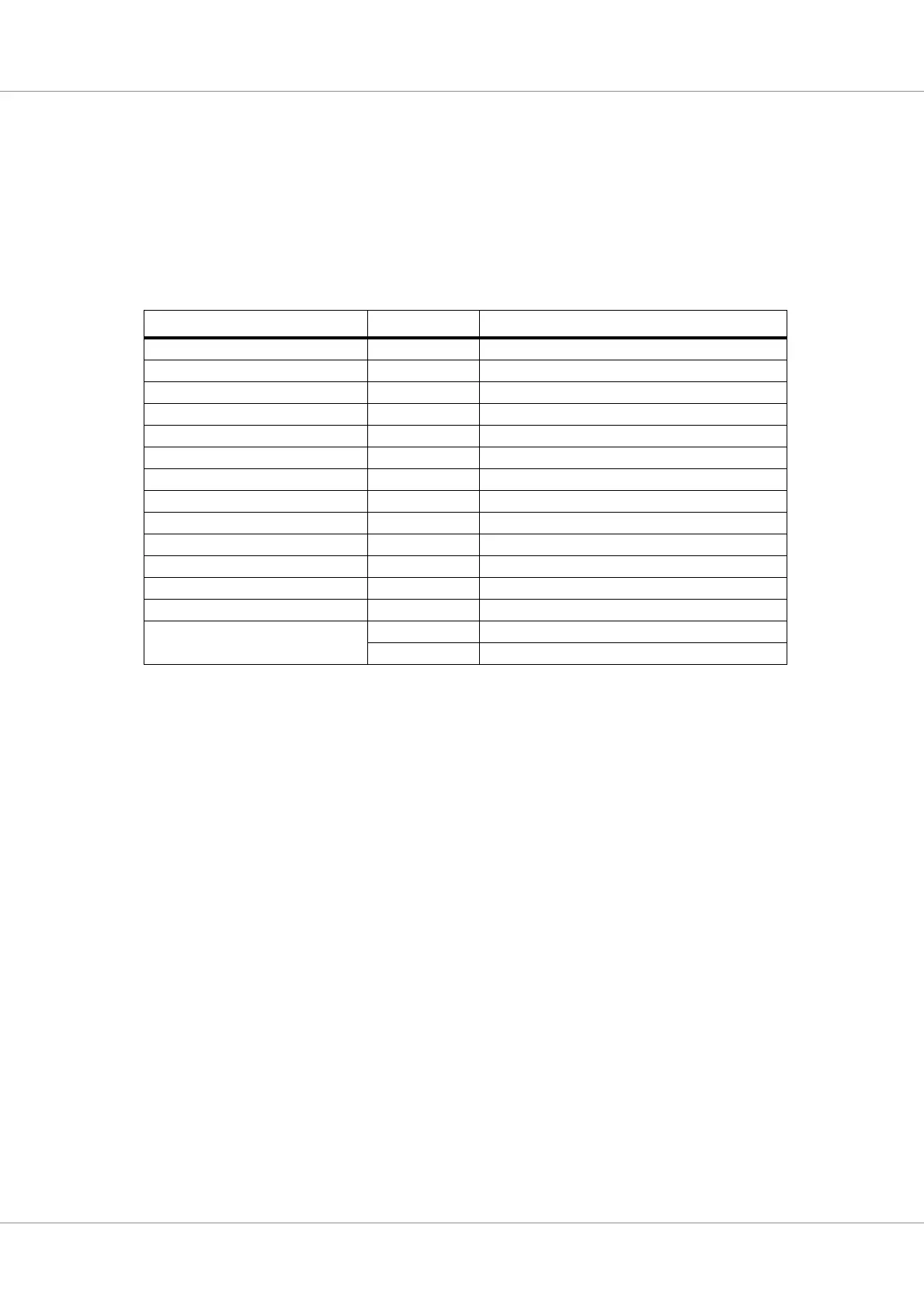

8.2.3 Interrupt assignment

The following table specifies the interrupt assignment for the GR712RC:

8.2.4 Processor status monitoring

The processor status can be monitored through the Multiprocessor Status Register. The STATUS field

in this register indicates if a processor is halted (‘1’) or running (‘0’). A halted processor can be reset

and restarted by writing a ‘1’ to its status field. After reset, all processors except processor 0 are

halted. When the system is properly initialized, processor 0 can start the remaining processors by

writing to their STATUS bits.

8.2.5 Interrupt broadcasting

An incoming interrupt that has its bit set in the Broadcast Register is propagated to the force register

of all processors rather than only to the Pending Register. This can be used to implement a timer that

fires to all processors with that same interrupt.

TABLE 40. Interrupt assignment

Core Interrupt # Function

AHBSTAT 1 AHB bus error

APBUART - 0 2 UART0 RX/TX interrupt

GRGPIO1-2 1-15 External I/O interrupt (3 & 4 are GPIO only)

CANOC 5-6 OCCAN interrupt (core 1 - 2)

GRTIMER 7 GRTIMER timer underflow interrupt

GPTIMER 8-11 GPTIMER timer underflow interrupts

IRQMP 12 IRQMP Extended interrupt

SPICTRL, SLINK 13 SPI and SLINK interrupt

B1553BRM, GRETH, GRTC 14 1553, Ethernet, and Telecommand interrupt

ASCS 16 ASCS interrupt

APBUART - 1 to 5 17-21 UART1-5 RX/TX interrupt

GRSPW2 - 0 to 5 22-27 SpaceWire 0-5 RX/TX data interrupt

I2CMST 28 I2C master interrupt

GRTM 29 Telemetry encoder interrupt

30 Telemetry encoder time strobe interrupt

Loading...

Loading...