GR712RC-UM, Jun 2017, Version 2.9 181 www.cobham.com/gaisler

GR712RC

25.3 Registers

The core is programmed through registers at address 0x80000700.

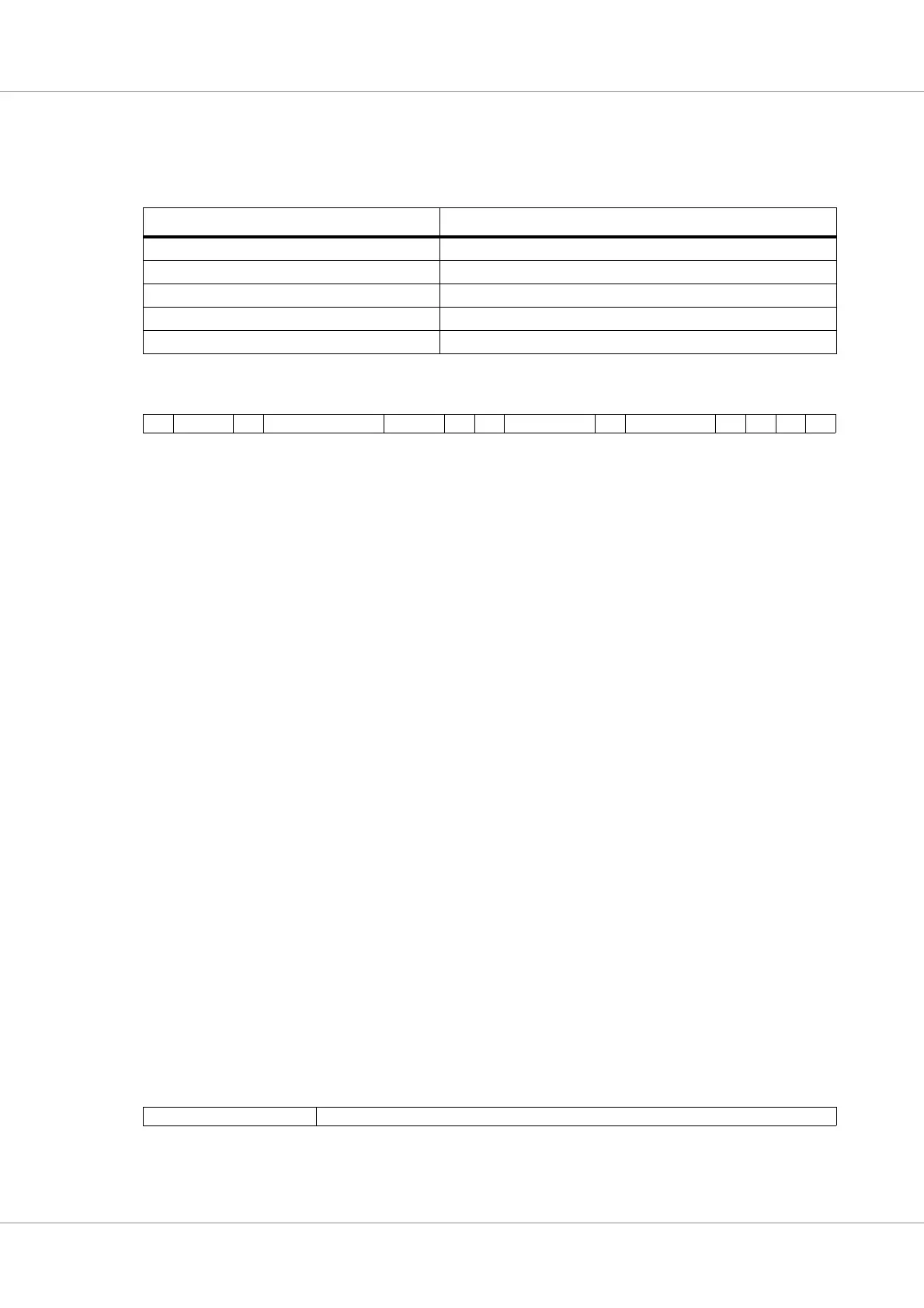

Table 196.GRASCS registers

APB address offset Register

0x80000700 Command and control register

0x80000704 ETR scale register

0x80000708 Status and capability register

0x8000070C TC data and control register

0x80000710 TM data register

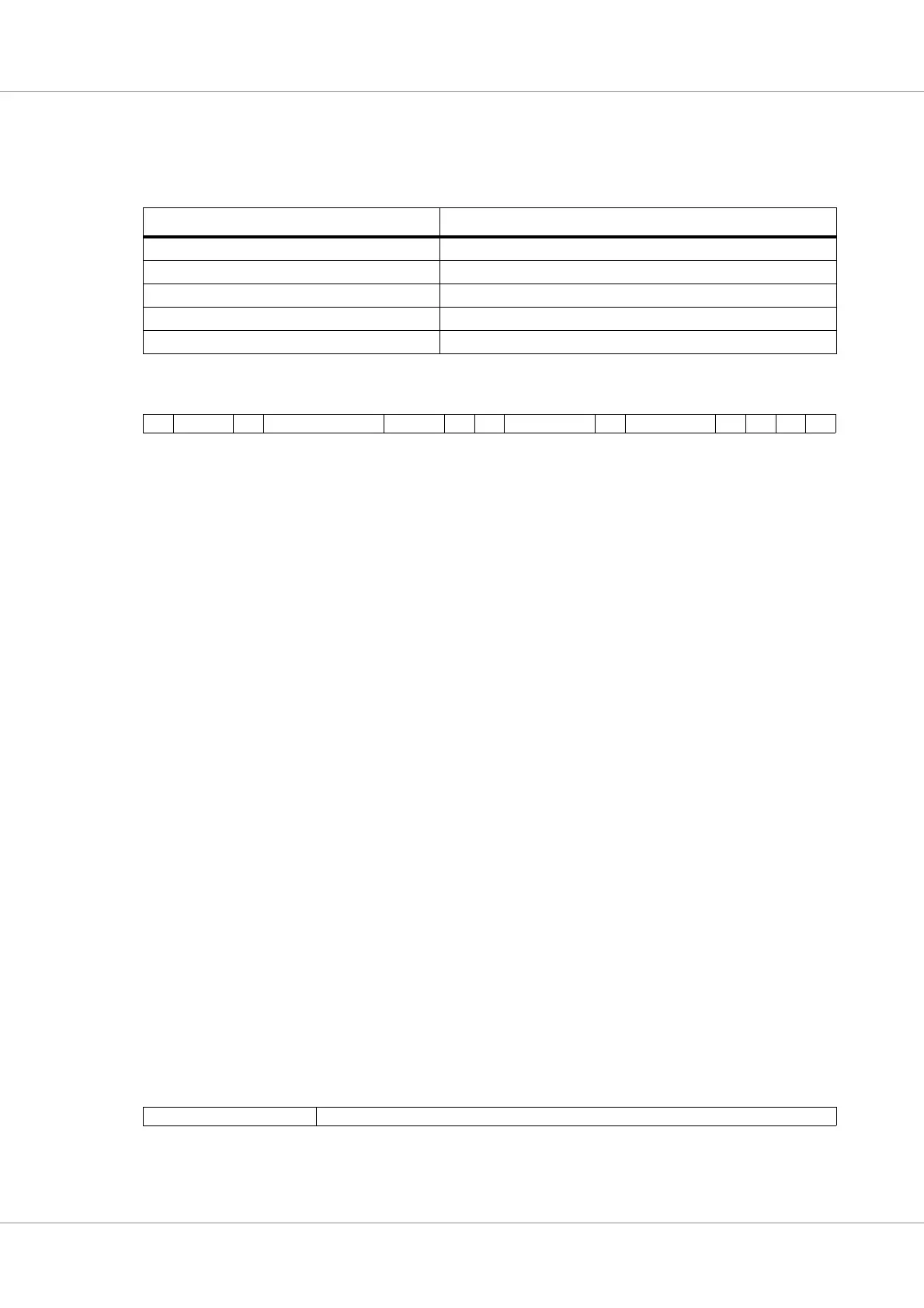

Table 197. Command and control register

31 25 24 23 16 15 14 13 12 11 8 7 6 4 3 2 1 0

OEN R us1c us1 R tmd tcd slave_sel R etr_ctrl stm estst stst res

31 Output enable. Reset value 0. (Read/Write)

30:25 Reserved, always zero

24 This bit can’t be written and it always reads zero. But if the us1 field should be updated then this bit needs

to be set to a ‘1’ in the same write cycle.

23:16 Number of system clock cycles in a micro second. In order to preserve correct timing of transactions the

core prevents these bits from being written if the run bit in the status register is set to ‘1’. (Read/Write)

15:14 Reserved, always zero

13 Interrupt control mask bit for TMs. When set to ‘1’ an interrupt is generated when a TM is done, when set

to ‘0’ no interrupt is generated. (Read/Write)

12 Interrupt control mask bit for TCs. When set to ‘1’ an interrupt is generated when a TC is done, when set to

‘0’ no interrupt is generated. (Read/Write)

11:8 Slave select bits. Decides which slave input the core listens to when performing a TM. In order to prevent

faulty data to be stored in the TM register the core prevents these bits from being written if the tma bit in the

status register is ‘1’. Only the number of bits required to represent the number of slaves are used, the rest

are always zero. (Read/Write)

7 Reserved, always zero

6:4 ETR source control. Decides which source that should be used for the ETR synchronization pulse. A value

of 0 means that an internal counter is used while a value of 1 - 6 means that external time marker 1 - 6 will

be used. In order to prevent an invalid ETR period or pulse the core prevents these bits from being written

when the erun bit in the status register is ‘1’. (Read/Write)

3 Send TM bit. When this bit is set to ‘1’ the core will perform a TM the next chance it gets and at the same

time clear this bit. (Read/Write)

2 Synchronization interface start/stop. This bit is set/cleared immediately but the actual start/stop of the inter-

face might be delayed. The real status of the synchronization interface is reported in the status register.

(Read/Write)

1 Serial interface start/stop. This bit is set/cleared immediately but the actual start/stop of the interface might

be delayed. The real status of the serial interface is reported in the status register. (Read/Write)

0 Reset. Writing a ‘1’ to this bit is equivalent with a hardware reset with the following exceptions: In order to

be sure that the core never generates a invalid ETR pulse or transactions with too short delays in between

them, the ETR scale register and internal timers are not reset, and the etr_running bit in the status register

might not be cleared immediately. This bit is cleared by the core the cycle after is set. (Read/Write)

Table 198. ETR scale register

31 28 27 0

R

31:28 Reserved, always zero

27:0 This field should be set to the number of system clock cycles in one ETR period. (Read/Write)

Loading...

Loading...