GR712RC-UM, Jun 2017, Version 2.9 182 www.cobham.com/gaisler

GR712RC

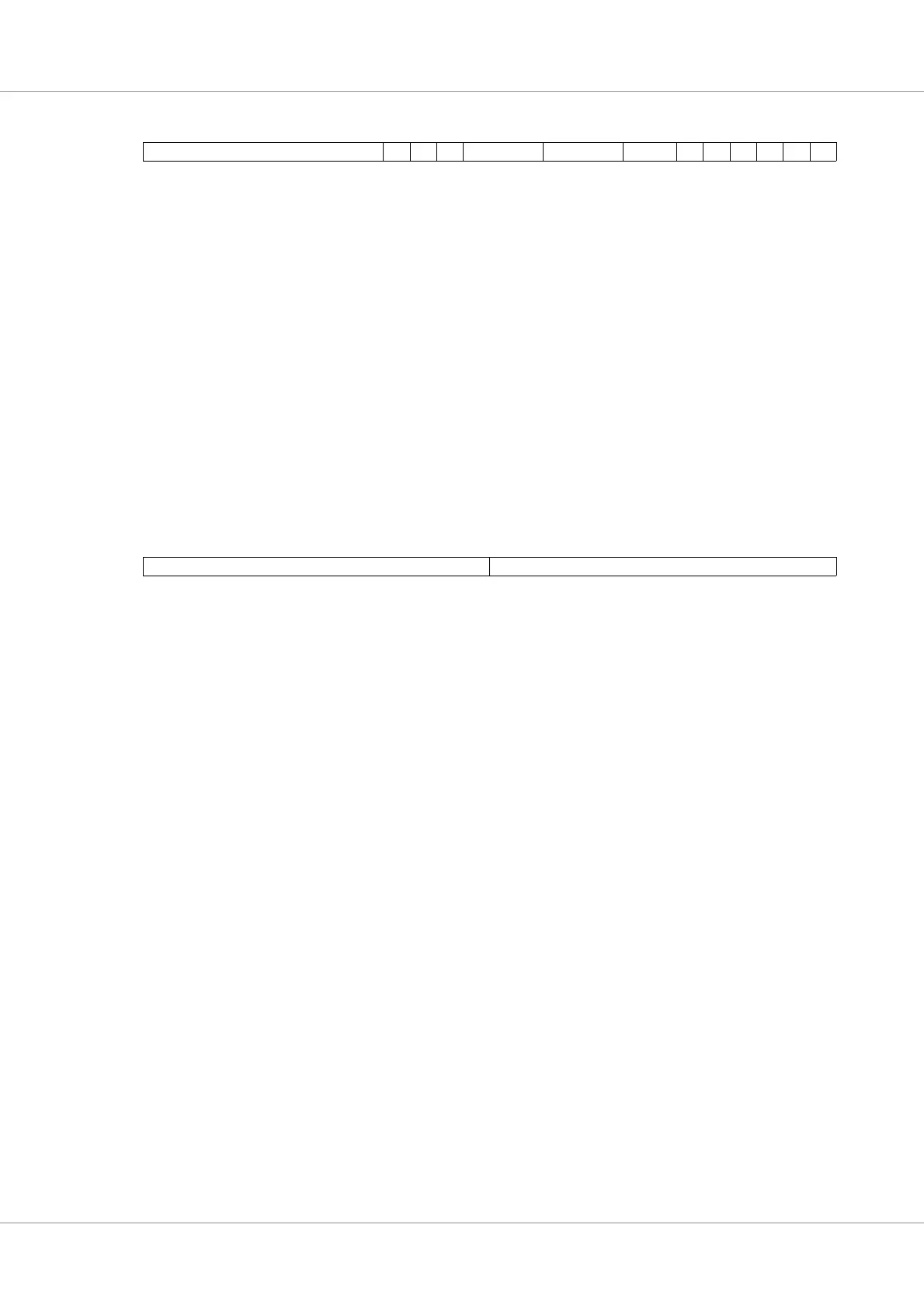

Table 199. Status and capability register

31 2019181716 1312 876543210

R tmc usc sdc nslaves dbits R tmd tcd tma tca erun run

31:20 Reserved, always zero.

19 Capability bit ‘1’: five external time markers enabled (Read only)

18 Capability bit ‘0’: using internal us counter (Read only)

17 Capability bit ‘1’: separate input signals (Read only)

16:13 Capability bits “01”: number of slaves minus one, 2 slaves. (Read only)

12:8 Capability bits “1111”: number of bits in data word minus one, 16 bits. (Read only)

7:6 Reserved, always zero.

5 TM done bit. Core sets this bit to ‘1’ when a TM is done. Software can clear this bit by writing ‘1’ to it.

(Read/Write clear)

4 TC done bit. Core sets this bit to ‘1’ when a TC is done. Software can clear this bit by writing ‘1’ to it. (Read/

Write clear)

3 TM active. Set to ‘1’ if a TM is in progress. (Read only)

2 TC active. Set to ‘1’ if a TC is in progress. (Read only)

1 ETR running bit. This bit is set to ‘1’when the synchronization interface is running. (Read only)

0 Serial running bit. This bit is set to ‘1’ when the serial interface is running. (Read only)

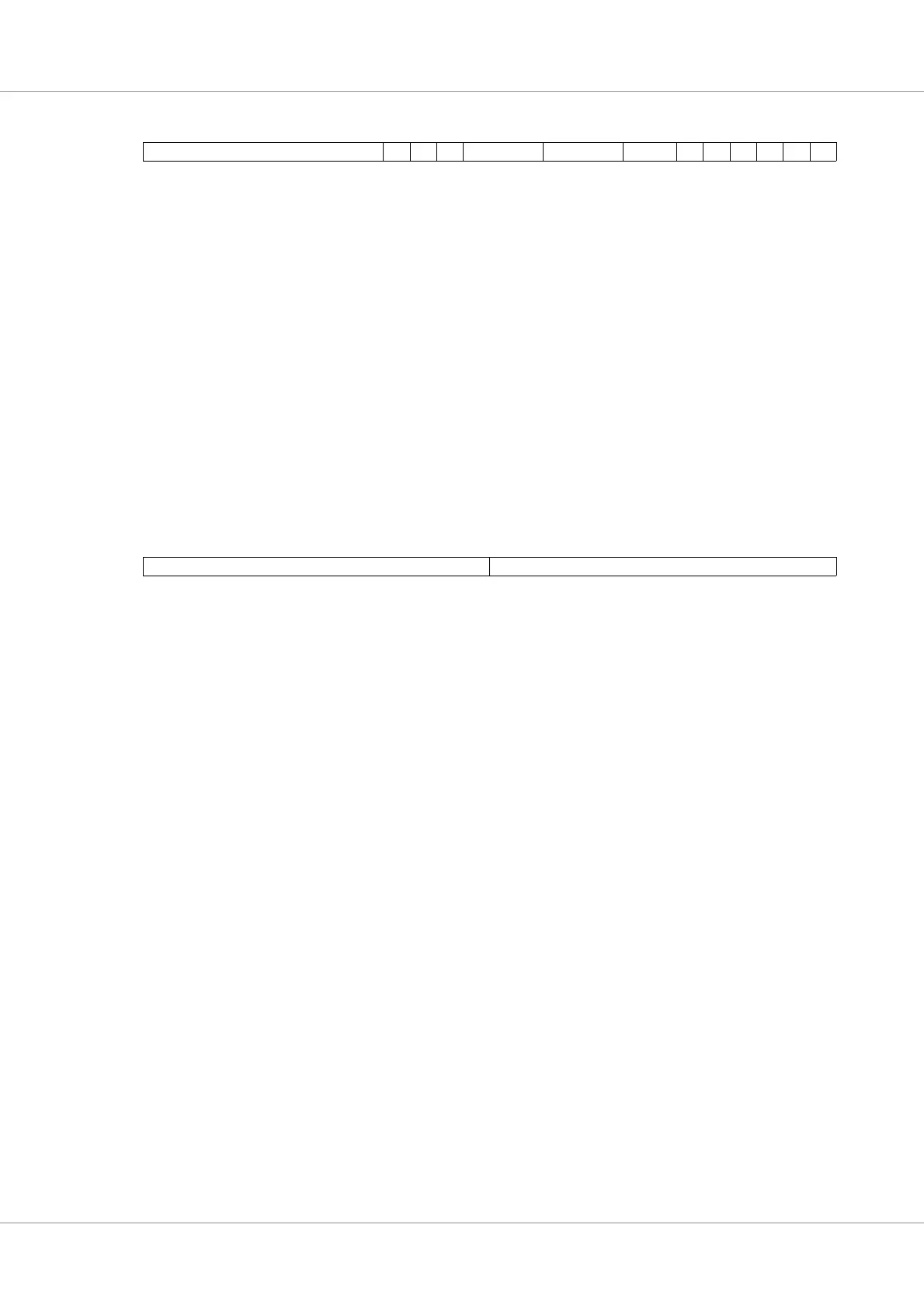

Table 200. TC data and control register

31 16 15 0

Rtcd

31:16 Reserved, always zero.

15: 0 TC data. When these bits are written the core will perform a TC at the next chance it gets and send

the data written. In order to not send wrong TC data the core prevents these bits from being written if

the tca bit in the status register is set to ‘1’. (Read/Write)

Loading...

Loading...