GR712RC-UM, Jun 2017, Version 2.9 69 www.cobham.com/gaisler

GR712RC

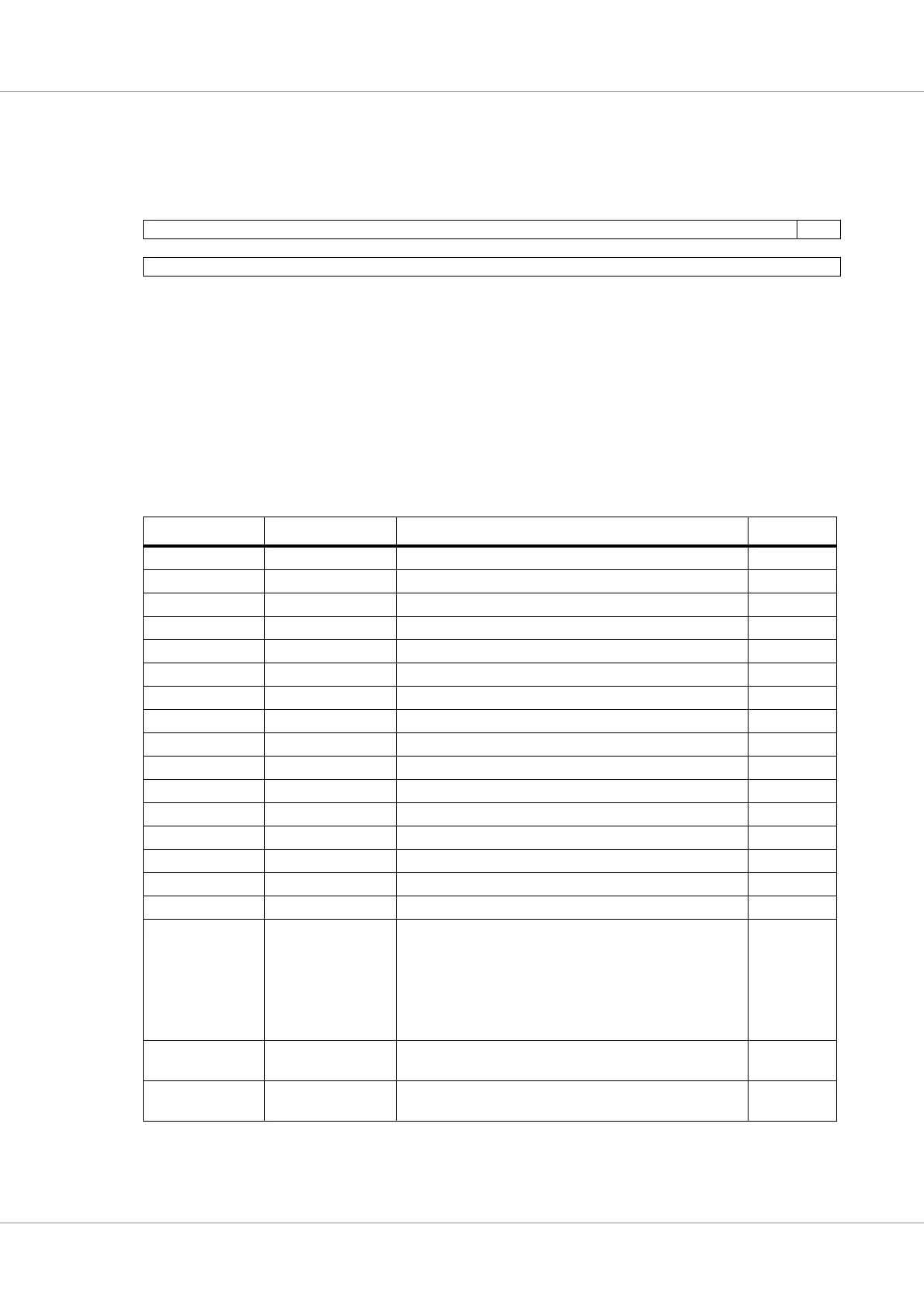

5.14.4 Memory configuration register 4 (MCFG4)

MCFG4 provides means to insert Reed-Solomon EDAC errors into memory for diagnostic purposes.

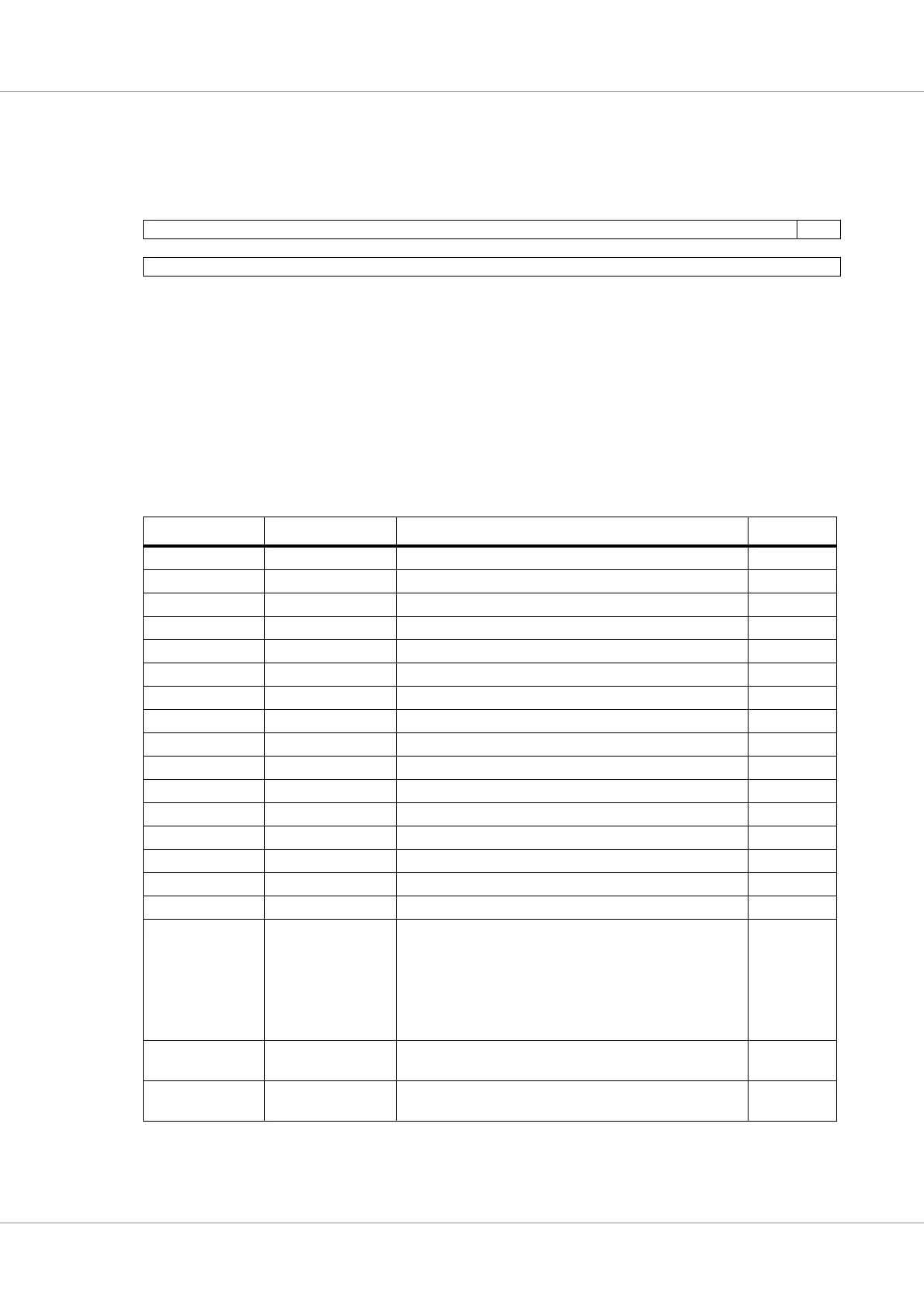

5.15 Signal definitions

The signals are described in table 33.

Table 32. Memory configuration register 4

31 16

RESERVED WB

15 0

TCB[15:0]

31: 17 RESERVED

16 EDAC diagnostic write bypass (WB) - Enables EDAC write bypass. Identical to WB in MCFG3.

15: 0 Test checkbits (TCB) - This field replaces the normal checkbits during write cycles when WB is set.

It is also loaded with the memory checkbits during read cycles when RB is set. Note that TCB[7:0]

are identical to TCB[7:0] in MCFG3

Table 33. Signal definitions

Signal name Type Function Active

ADDRESS[23:0] Output Memory address High

DATA[31:0] Input/Output Memory data High

CB[15:0] Input/Output Check bits High

RAMSN[1:0] Output SRAM chip select Low

RAMOEN Output SRAM output enable Low

RAMWEN Output SRAM write enable Low

OEN Output Output enable Low

WRITEN Output Write strobe Low

READ Output Read strobe High

IOSN Output I/O area chip select Low

ROMSN[1:0] Output PROM chip select Low

BRDYN Input Bus ready. Extends accesses to the PROM and IO areas. Low

BEXCN Input Bus exception. Low

SDWEN Output SDRAM write enable Low

SDRASN Output SDRAM row address strobe Low

SDCASN Output SDRAM column address strobe Low

SDDQM[3:0] Output SDRAM data mask:

SDDQM[3] corresponds to DATA[31:24],

SDDQM[2] corresponds to DATA[23:16],

SDDQM[1] corresponds to DATA[15:8],

SDDQM[0] corresponds to DATA[7:0].

Any SDDQM[ ] signal can be used for CB[ ].

High

GPIO[3] /

SWMX[6]

Input Configuring PROM data width at reset. 8-bit data width

when “0”, and 32-bit when “1”.

-

GPIO[1] /

SWMX[4]

Input Enabling EDAC usage for PROM at reset when “1”. -

Loading...

Loading...