GR712RC-UM, Jun 2017, Version 2.9 44 www.cobham.com/gaisler

GR712RC

4.2.14 Processor reset operation

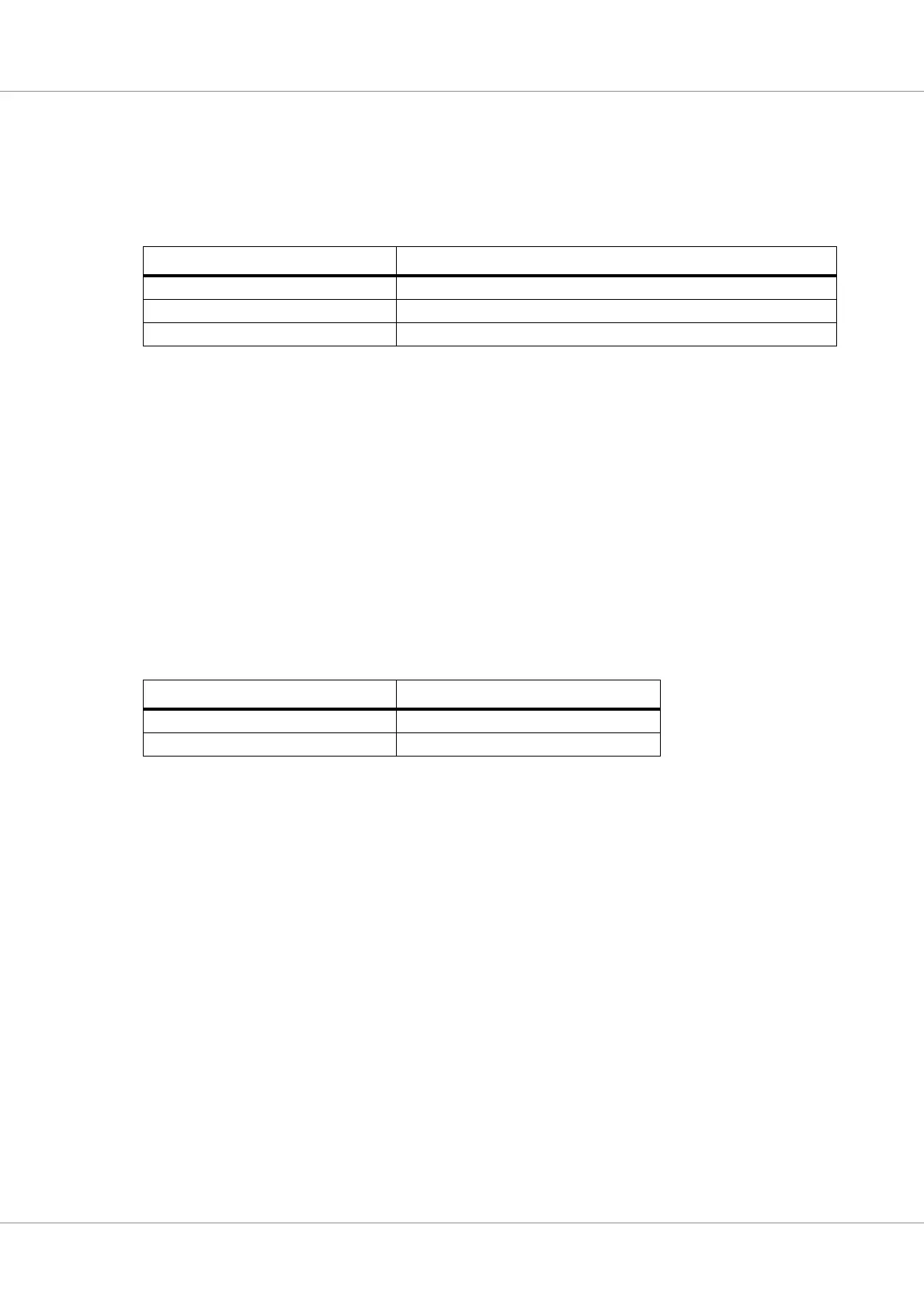

The processor is reset by asserting the RESET input for at least 4 clock cycles. The following table

indicates the reset values of the registers which are affected by the reset. All other registers maintain

their value (or are undefined). Since PC is set to 0, execution start at address 0 in the PROM area.

4.2.15 Multi-processor support

The GR712RC contains two LEON3 processor support symmetric multiprocessing (SMP) configura-

tion. After reset, only the first processor will start while the second processor will remain halted in

power-down mode. After the system has been initialized, the second processor can be started by writ-

ing to the ‘MP status register’, located in the multi-processor interrupt controller. The halted proces-

sors will start executing from address 0. Cache snooping should always be enabled in SMP systems to

maintain data cache coherency between the processors.

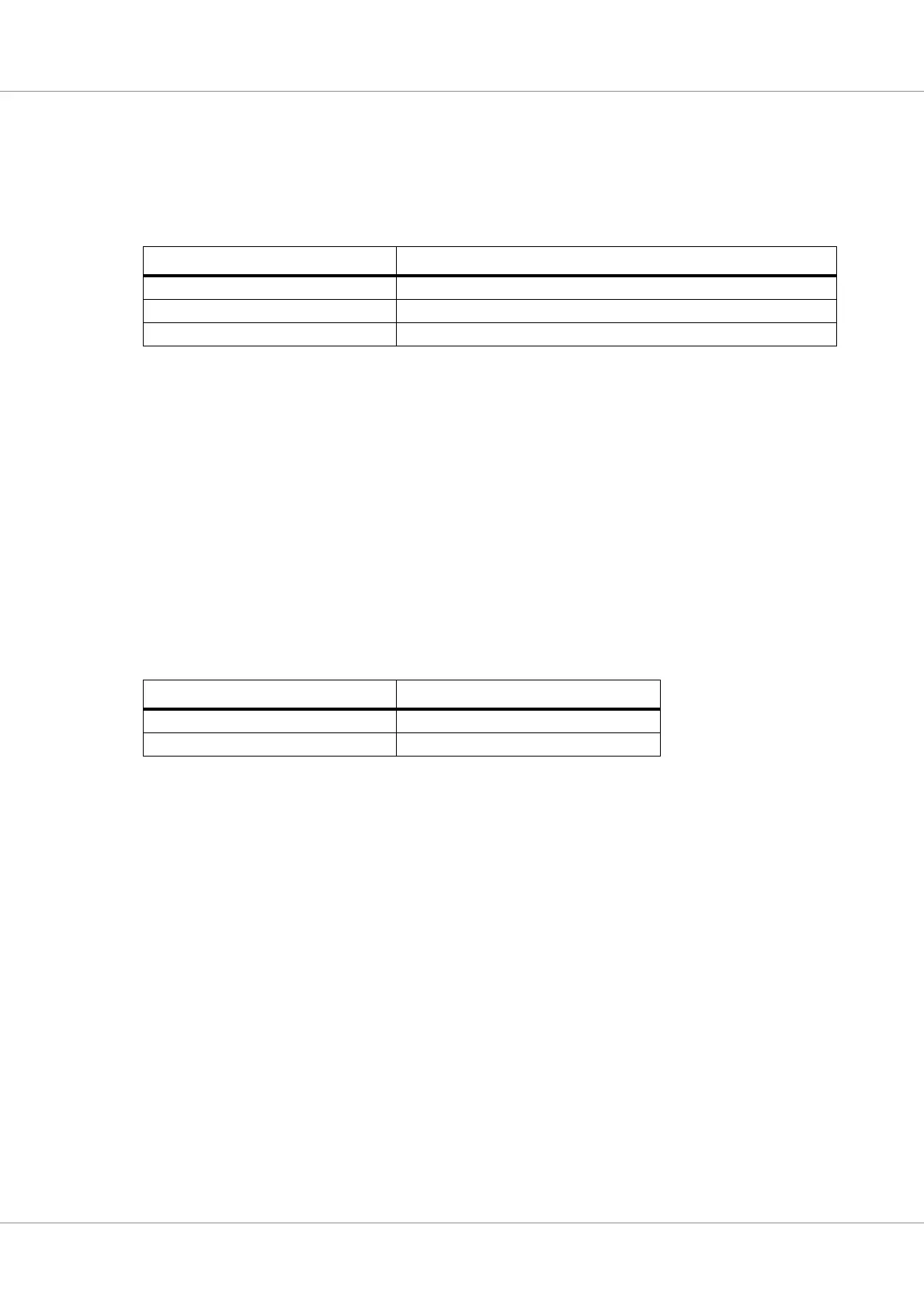

4.2.16 Cache sub-system

The LEON3 processor implements a Harvard architecture with separate instruction and data buses,

connected to two independent cache controllers. The cacheable memory areas are shown in the table

below.

4.3 Instruction cache

4.3.1 Operation

The instruction cache is as a 4x4 KiB multi-way cache with 32 byte/line, using true LRU replacement

policy. Each line has a cache tag associated with it consisting of a tag field and a valid field with one

valid bit for each 4-byte sub-block. On an instruction cache miss to a cachable location, the instruc-

tion is fetched and the corresponding tag and data line updated.

If instruction burst fetch is enabled in the cache control register (CCR), the cache line is filled starting

at the missed address and until the end of the line. At the same time, the instructions are forwarded to

the IU (streaming). If the IU cannot accept the streamed instructions due to internal dependencies or

multi-cycle instruction, the IU is halted until the line fill is completed. If the IU executes a control

transfer instruction (branch/CALL/JMPL/RETT/TRAP) during the line fill, the line fill will be termi-

nated on the next fetch. If instruction burst fetch is enabled, instruction streaming is enabled even

when the cache is disabled. In this case, the fetched instructions are only forwarded to the IU and the

cache is not updated. During cache line refill, incremental burst are generated on the AHB bus.

If a memory access error occurs during a line fill with the IU halted, the corresponding valid bit in the

cache tag will not be set. If the IU later fetches an instruction from the failed address, a cache miss

will occur, triggering a new access to the failed address. If the error remains, an instruction access

error trap (tt=0x1) will be generated.

Table 17. Processor reset values

Register Reset value

PC (program counter) 0x0

nPC (next program counter) 0x4

PSR (processor status register) ET=0, S=1

Table 18. Cacheable areas

Address range Usage

0x00000000 - 0x20000000

External PROM

0x40000000 - 0x80000000

External SRAM/SDRAM

Loading...

Loading...