GR712RC-UM, Jun 2017, Version 2.9 43 www.cobham.com/gaisler

GR712RC

4.2.12 Address space identifiers (ASI)

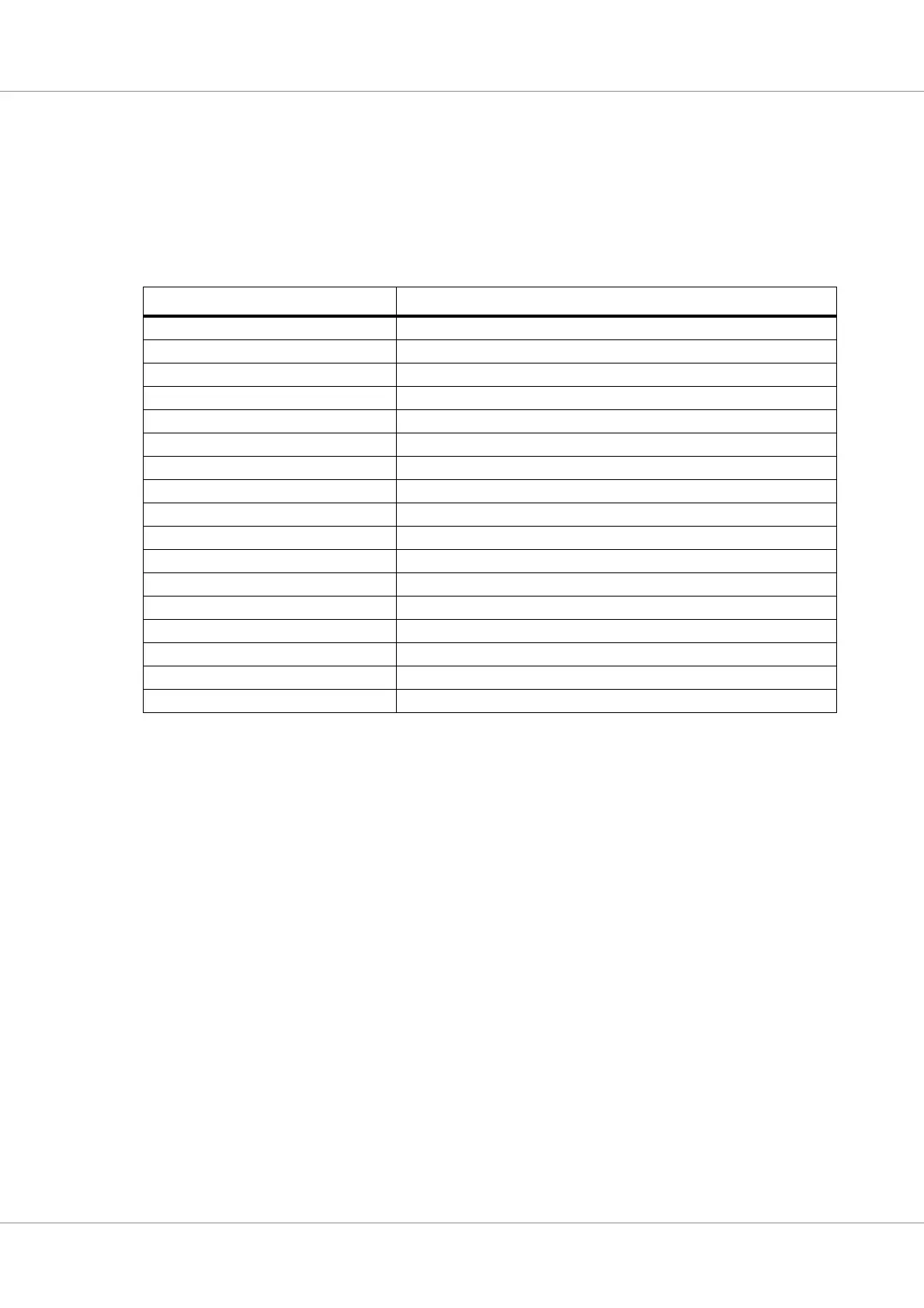

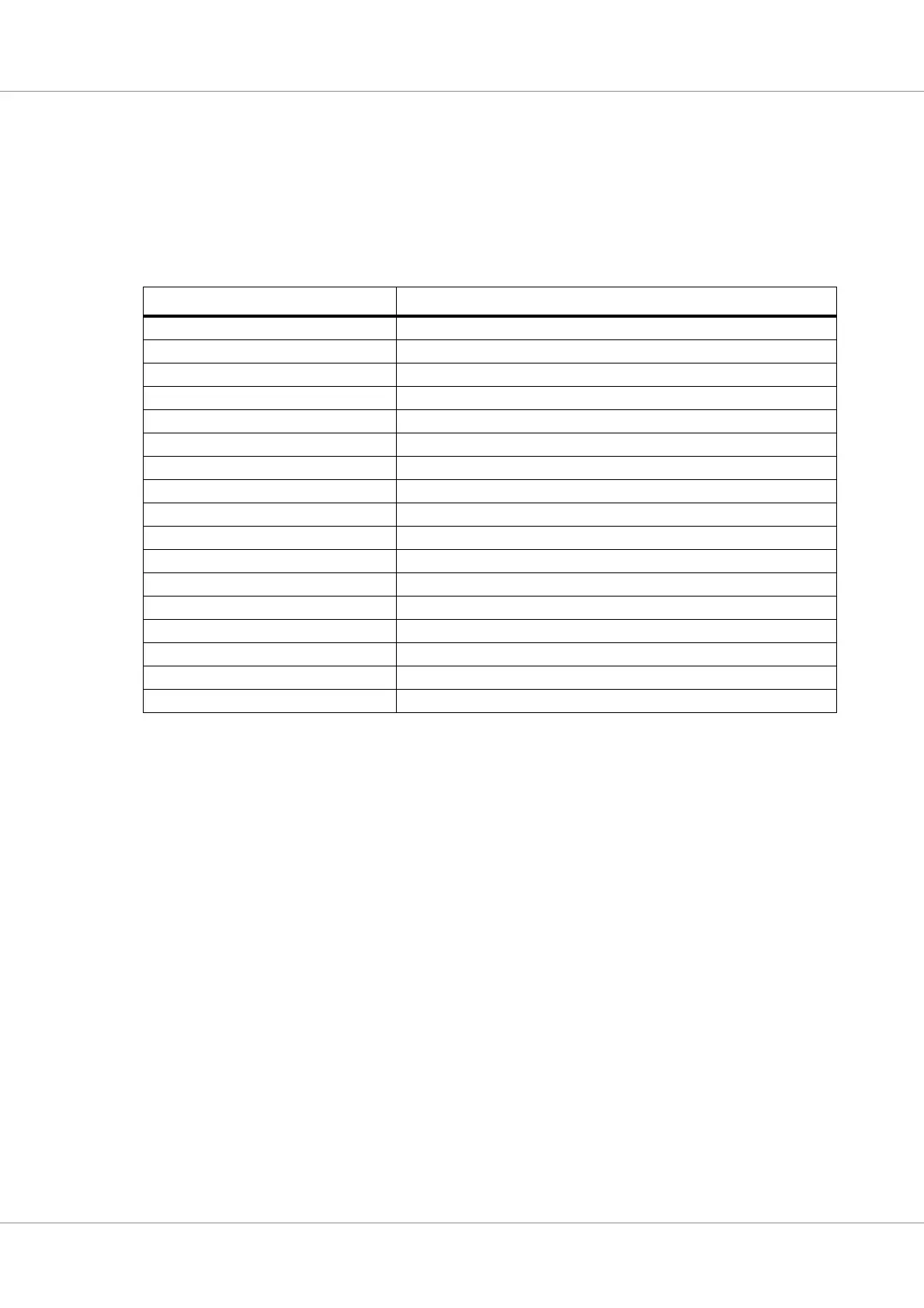

In addition to the address, a SPARC processor also generates an 8-bit address space identifier (ASI),

providing up to 256 separate, 32-bit address spaces. During normal operation, the LEON3 processor

accesses instructions and data using ASI 0x8 - 0xB as defined in the SPARC standard. Using the

LDA/STA instructions, alternative address spaces can be accessed. The table shows the ASI usage for

LEON3. Only ASI[5:0] are used for the mapping, ASI[7:6] have no influence on operation.

For historical reasons there are multiple ASIs that flush the cache in different ways.

Writing to ASI 0x10 will flush the data cache and the instruction cache.

Writing to ASI 0x11 will flush the data cache only.

Writing to ASI 0x13 will flush the data cache and the instruction cache.

Writing to ASI 0x18, will flush both the MMU TLB, the I-cache, and the D-cache. This will block

execution for a few cycles while the TLB is flushed and then continue asynchronously with the cache

flushes continuing in the background.

4.2.13 Power-down

The processor can be configured to include a power-down feature to minimize power consumption

during idle periods. The power-down mode is entered by performing a WRASR instruction to

%asr19:

wr %g0, %asr19

During power-down, the pipeline is halted until the next interrupt occurs. The processor clock is

gated, reducing power consumption from dynamic switching of logic and clock net.

Table 16. ASI usage

ASI Usage

0x01 Forced cache miss

0x02 System control registers (cache control register)

0x08, 0x09, 0x0A, 0x0B Normal cached access (replace if cacheable)

0x0C Instruction cache tags

0x0D Instruction cache data

0x0E Data cache tags

0x0F Data cache data

0x10 Flush instruction and data caches

0x11 Flush data cache

0x13 Flush instruction and data caches

0x14 MMU diagnostic data cache context access

0x15 MMU diagnostic instruction cache context access

0x18 Flush MMU TLB and instruction and data caches

0x19 MMU registers

0x1C MMU bypass

0x1D MMU diagnostic access

0x1E MMU snoop tags diagnostic access

Loading...

Loading...