GR712RC-UM, Jun 2017, Version 2.9 72 www.cobham.com/gaisler

GR712RC

7 AHB Status Registers

7.1 Overview

The AHB status registers store information about AMBA AHB accesses returning an error response.

The AHB status registers consists of a failing address register capturing the address of the failed

access, and a status register providing information about the access type.

7.2 Operation

The registers monitor AMBA AHB bus transactions and store the current HADDR, HWRITE,

HMASTER and HSIZE internally. The monitoring is activated after reset and until an error response

(HRESP = “01”) is detected. When an error is detected, the status and address register contents are

frozen and the New Error (NE) bit is set to one. At the same time, interrupt 1 is generated. To restart

error monitoring, the NE bit must be cleared by software.

To be able to monitor error rates in on-chip and off-chip memories, the AHB status registers also latch

the address and control signals when a correctable error occurs in the off-chip memory controller, or

in the on-chip RAM module. Such errors do not cause an error response on the AHB bus, but can still

be detected through dedicated sideband signals. When such a correctable error is detected, the effect

will be the same as for an AHB error response, with the only difference that the Correctable Error

(CE) bit in the status register is set to one. When the CE bit is set, the interrupt routine can either scrub

the failing address or just register the error for statistical use. The NE bit should then be cleared to

restart error monitoring.

7.3 Registers

The core is programmed through registers mapped into APB address space.

Table 37. AHB Status registers

APB address Registers

0x80000F00 AHB Status register

0x80000F04 AHB Failing address register

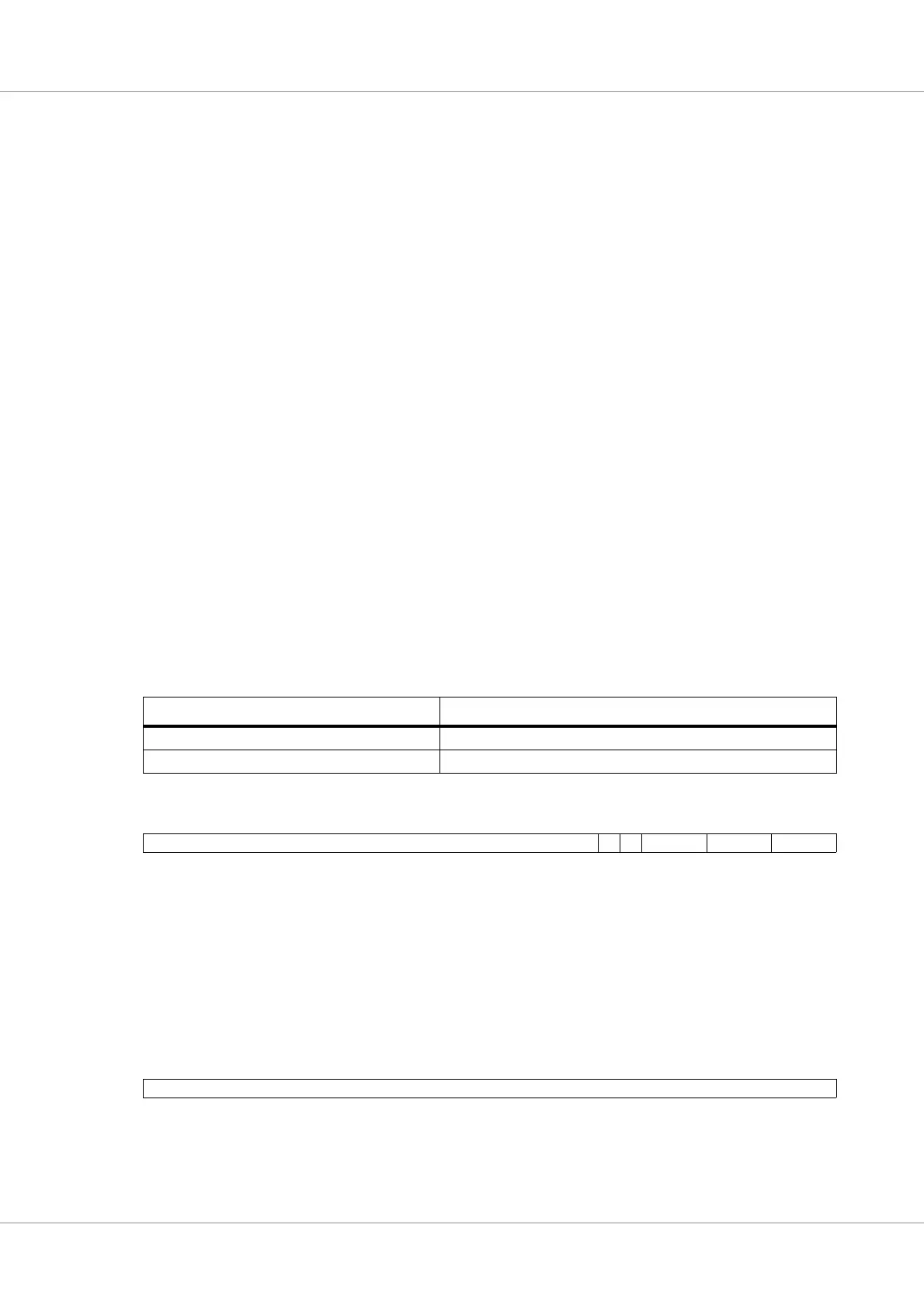

Table 38. AHB Status register

31 1098 7 6 32 0

RESERVED CE NE HWRITE HMASTER HSIZE

31: 10 RESERVED

9 CE: Correctable Error. Set if the detected error was caused by a single error and zero otherwise.

8 NE: New Error. Deasserted at start-up and after reset. Asserted when an error is detected. Reset by

writing a zero to it.

7 The HWRITE signal of the AHB transaction that caused the error.

6: 3 The HMASTER signal of the AHB transaction that caused the error.

2: 0 The HSIZE signal of the AHB transaction that caused the error

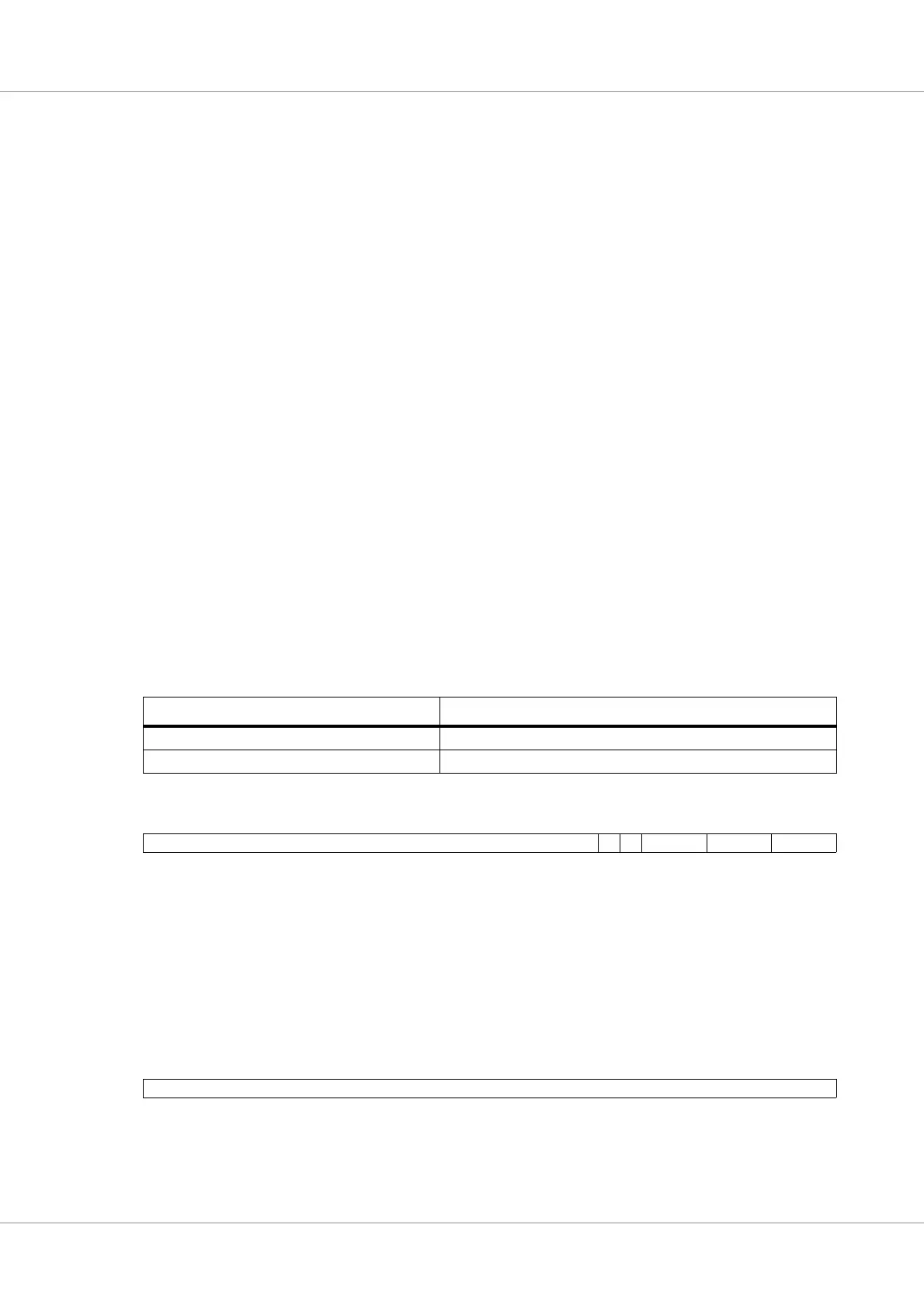

Table 39. AHB Failing address register

31 0

AHB FAILING ADDRESS

31: 0 The HADDR signal of the AHB transaction that caused the error.

Loading...

Loading...