GR712RC-UM, Jun 2017, Version 2.9 33 www.cobham.com/gaisler

GR712RC

CLK which is any multiple of 10 between 10-100 MHz (note that the required precision is 10 MHz +/

- 1 MHz).

The SpaceWire transmitter uses SDR output registers meaning that the bitrate will be equal to the

transmit clock. The SpaceWire input signals are sampled synchronously with DDR registers using the

transmit clock.

3.3 MIL-STD-1553

The B1553BRM core needs a 24, 20 or 16 MHz clock. The frequency used can be configured through

a register in the core. This clock can either be supplied directly to the B1553BRM core through the

1553CK pin, the system clock, or it can be generated through a clock divider that divides the system

clock and is programmable through the GPREG.

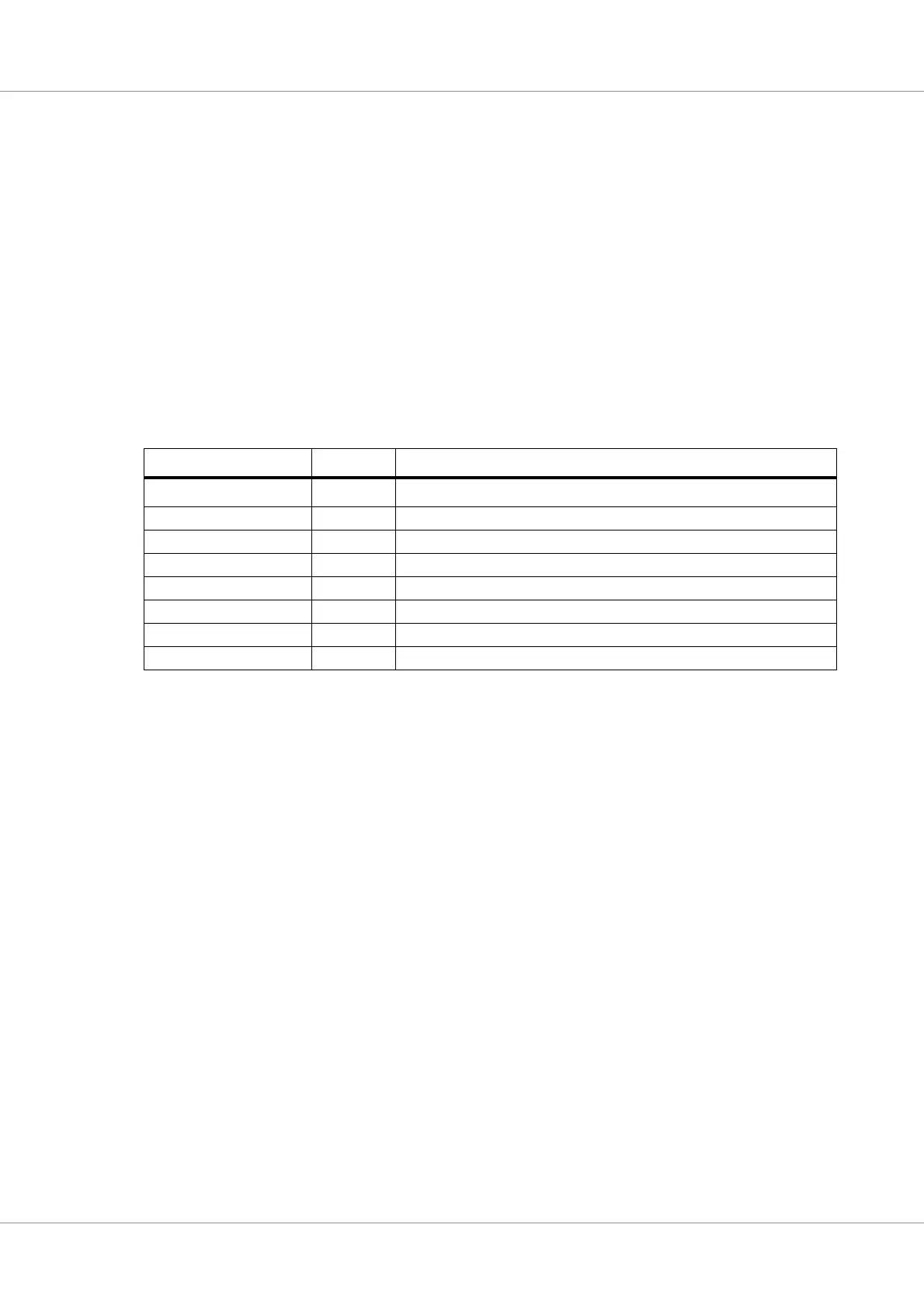

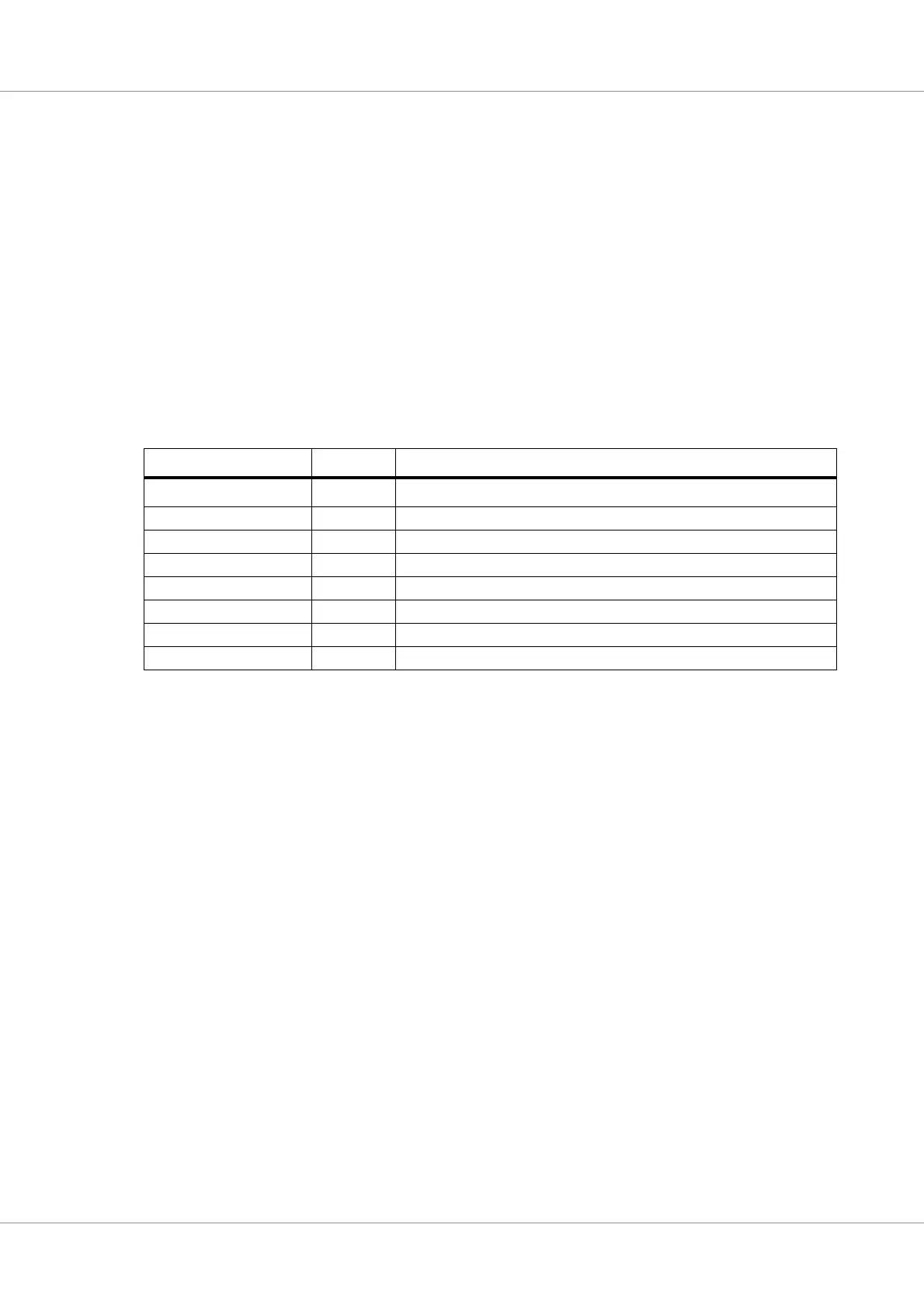

If the system clock is used to generate the BRM clock it must be one of the frequencies in the table

below:

Note 1: The system clock frequency must always be higher than BRM clock frequency, regardless of

how the BRM clock is generated.

Note 2: This specific case has not been validated.

3.4 Telemetry

The telemetry input clock frequency must be less than or equal to the system clock frequency. It is

possible to select either TMCLKI or system clock as input clock to the GRTM core.

The TMDO data signal is timed relative to TMCLKO.

3.5 Telecommand

The telecommand input signals are sampled using the system clock and the telecommand input clock

frequency must be less than or equal to the system clock frequency divided by eight.

3.6 Obsolete

Proprietary function not supported.

3.7 SLINK

The SLINK core is clocked by the system clock and has a built in clock divider. When using this inter-

face the system clock must be a multiple of 12 MHz if a 50% duty cycle is necessary. If the SLINK

clock duty cycle does not need to be 50% any multiple of 6 MHz is possible.

Table 12. MIL-STD-1553 BRM frequencies

System clock (MHz) Division BRM frequency (MHz)

32 2

16

2)

40 2 20

48 2 24

64 4 16

80 4 20

96 4 24

120 6 20

144 6 24

Loading...

Loading...