GR712RC-UM, Jun 2017, Version 2.9 102 www.cobham.com/gaisler

GR712RC

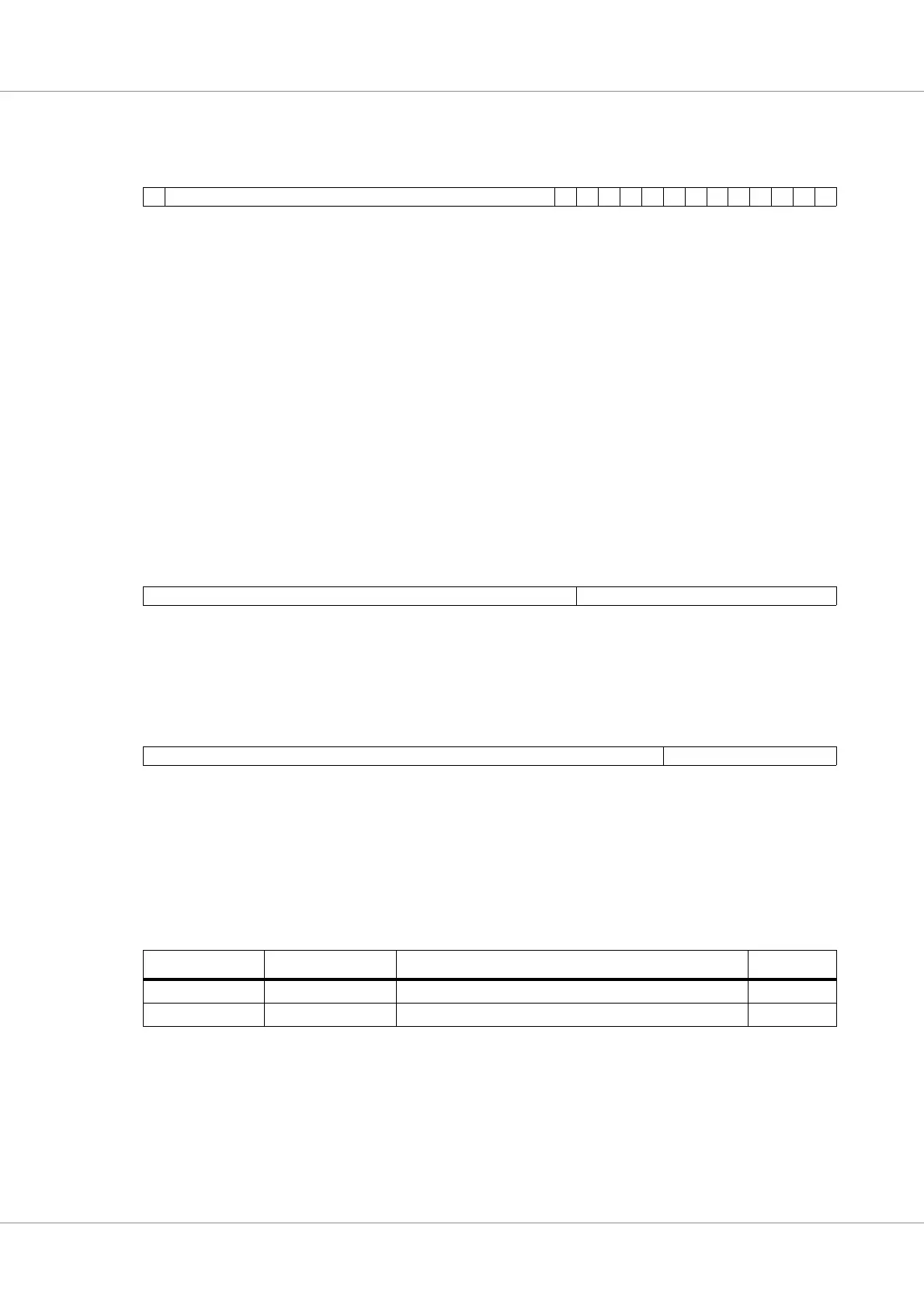

15.7.3 UART Control Register

Table 80. UART control register

15.7.4 UART Scaler Register

Table 81. UART scaler reload register

15.7.5 UART FIFO Debug Register

Table 82. UART FIFO debug register

15.8 Signal definitions

The signals are described in table 83.

31 30 131211109876543210

FA RESERVED 0 DB RF TF 0 LB 0 PE PS TI RI TE RE

31 FIFOs available (FA) - Set to 1, read-only. Receiver and transmitter FIFOs are available.

30: 13 RESERVED

11 FIFO debug mode enable (DB) - when set, it is possible to read and write the FIFO debug register

10 Receiver FIFO interrupt enable (RF) - when set, Receiver FIFO level interrupts are enabled

9 Transmitter FIFO interrupt enable (TF) - when set, Transmitter FIFO level interrupts are enabled.

7 Loop back (LB) - if set, loop back mode will be enabled

5 Parity enable (PE) - if set, enables parity generation and checking (when implemented)

4 Parity select (PS) - selects parity polarity (0 = even parity, 1 = odd parity) (when implemented)

3 Transmitter interrupt enable (TI) - if set, interrupts are generated when a frame is transmitted

2 Receiver interrupt enable (RI) - if set, interrupts are generated when a frame is received

1 Transmitter enable (TE) - if set, enables the transmitter.

0 Receiver enable (RE) - if set, enables the receiver.

31 12 11 0

RESERVED SCALER RELOAD VALUE

11: 0 Scaler reload value

31 87 0

RESERVED DATA

7: 0 Transmitter holding register or FIFO (read access)

7: 0 Receiver holding register or FIFO (write access)

Table 83. Signal definitions

Signal name Type Function Active

UART_TX[5:0] Output UART transmit data line -

UART_RX[5:0] Input UART receive data line -

Loading...

Loading...