GR712RC-UM, Jun 2017, Version 2.9 168 www.cobham.com/gaisler

GR712RC

Note that the fields of the Mode register, which includes DIV16, FACT and PM, should not be

changed when the core is enabled. If the FACT field is set to 0 the core’s register interface is compat-

ible with the register interface found in MPC83xx SoCs. If the FACT field is set to 1, the core can

generate an SPICLK clock with higher frequency.

23.2.4 Operation (master-only)

Master operation will transmit a word when there is data available in the transmit queue. When the

transmit queue is empty the core will drive SPICLK to its idle state.

The core does not implement any slave select outputs. General purpose I/O pins can be used as slave

select signals, which will be controlled via the General Purpose I/O Port(s).

23.3 Registers

The core is programmed through registers mapped into APB address space.

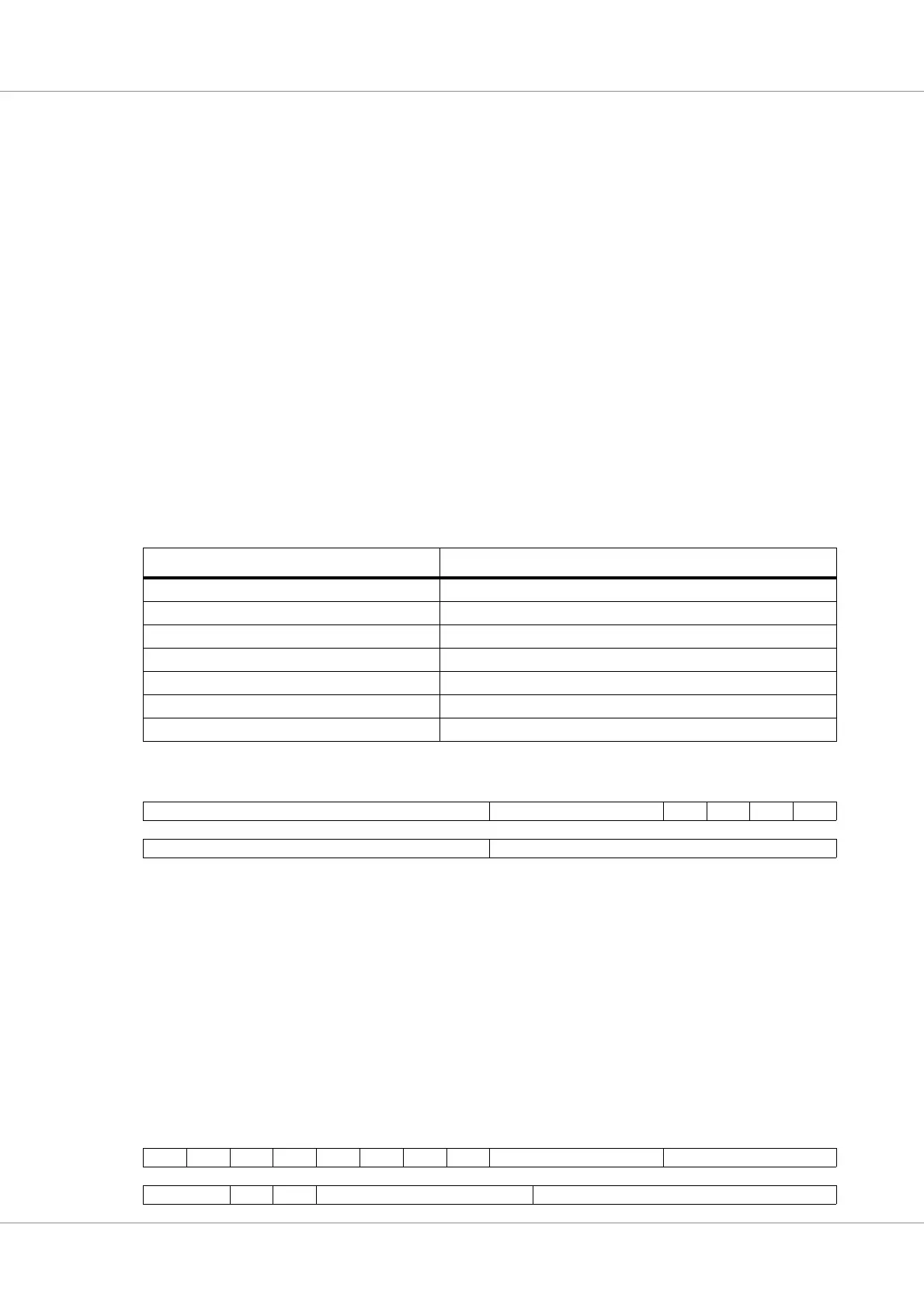

Table 172.SPI controller registers

APB address Register

0x80000400 Capability register

0x80000420 Mode register

0x80000424 Event register

0x80000428 Mask register

0x8000042C Command register

0x80000430 Transmit register

0x80000434 Receive register

Table 173. SPI controller Capability register

31 24 23 20 19 18 17 16

SSSZ RESERVED 0 0 0 SSEN

15 8 7 0

FDEPTH REV

31: 24 Slave Select register size (SSSZ) - If the core has been configured with slave select signals this field

contains the number of available signals. This value in this field (1) is not applicable as this imple-

mentation does not have dedicated slave select signals.

23: 20 RESERVED - The value of this field should not be used

16 Slave Select Enable (SSEN) - If the core has a slave select register, and corresponding slave select

lines, the value of this field is one. Otherwise the value of this field is zero. The value in this imple-

mentation is zero.

15: 8 FIFO depth (FDEPTH) - This field contains the depth of the core’s internal FIFOs, which is 16 for

this implementation. The number of words the core can store in each queue is FDEPTH+1, since the

transmit and receive registers can contain one word each.

6: 0 Core revision (REV) - This manual applies to core revision 2.

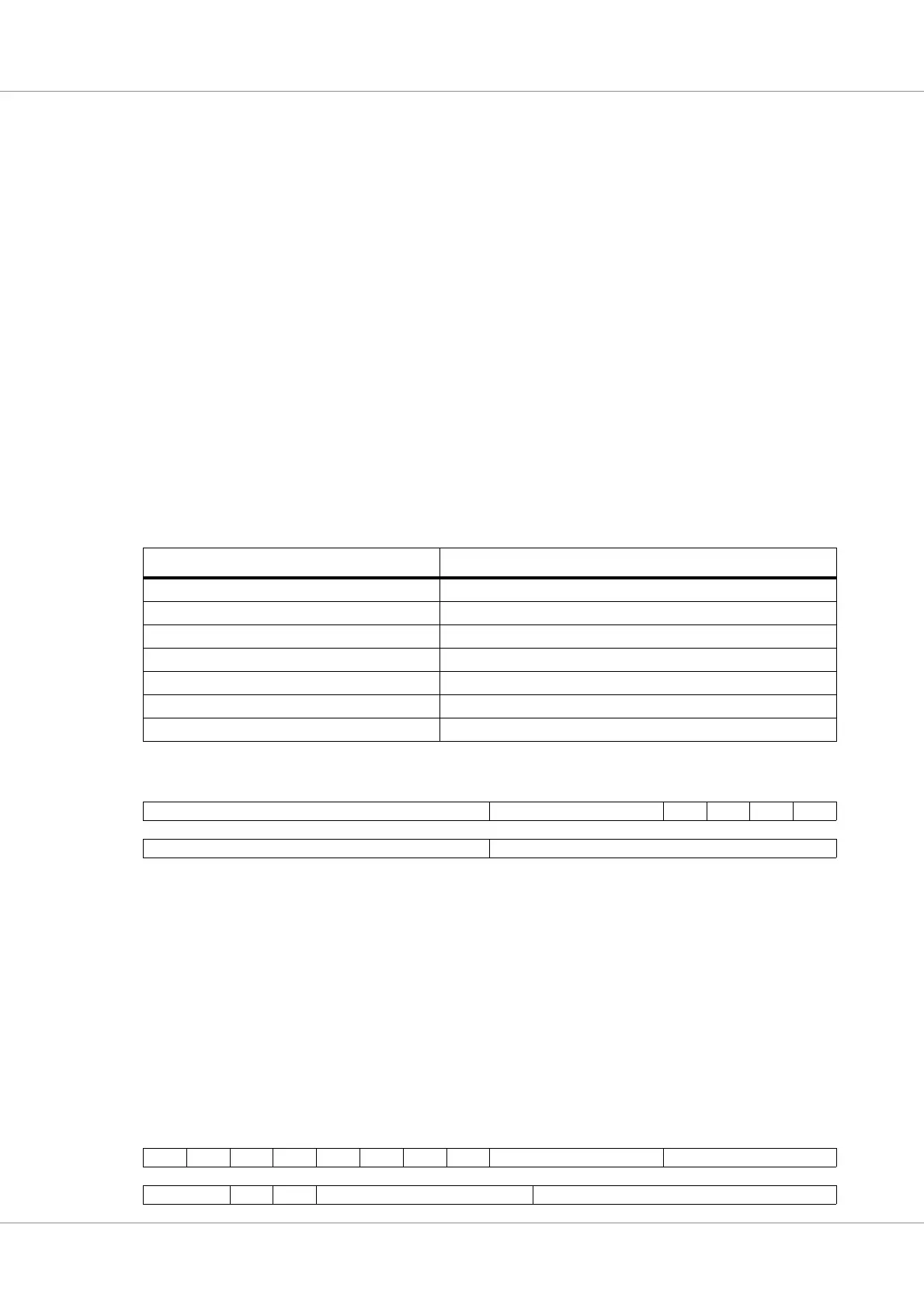

Table 174. SPI controller Mode register

31 30 29 28 27 26 25 24 23 20 19 16

0 LOOP CPOL CPHA DIV16 REV MS EN LEN PM

15 14 13 12 11 7 6 0

RESERVED FACT R CG RESERVED

SCKFrequency

AMBAclockfrequency

16 4 2 FACT–PM 1+

--------------------------------------------------------------------------------

=

Loading...

Loading...