GR712RC-UM, Jun 2017, Version 2.9 133 www.cobham.com/gaisler

GR712RC

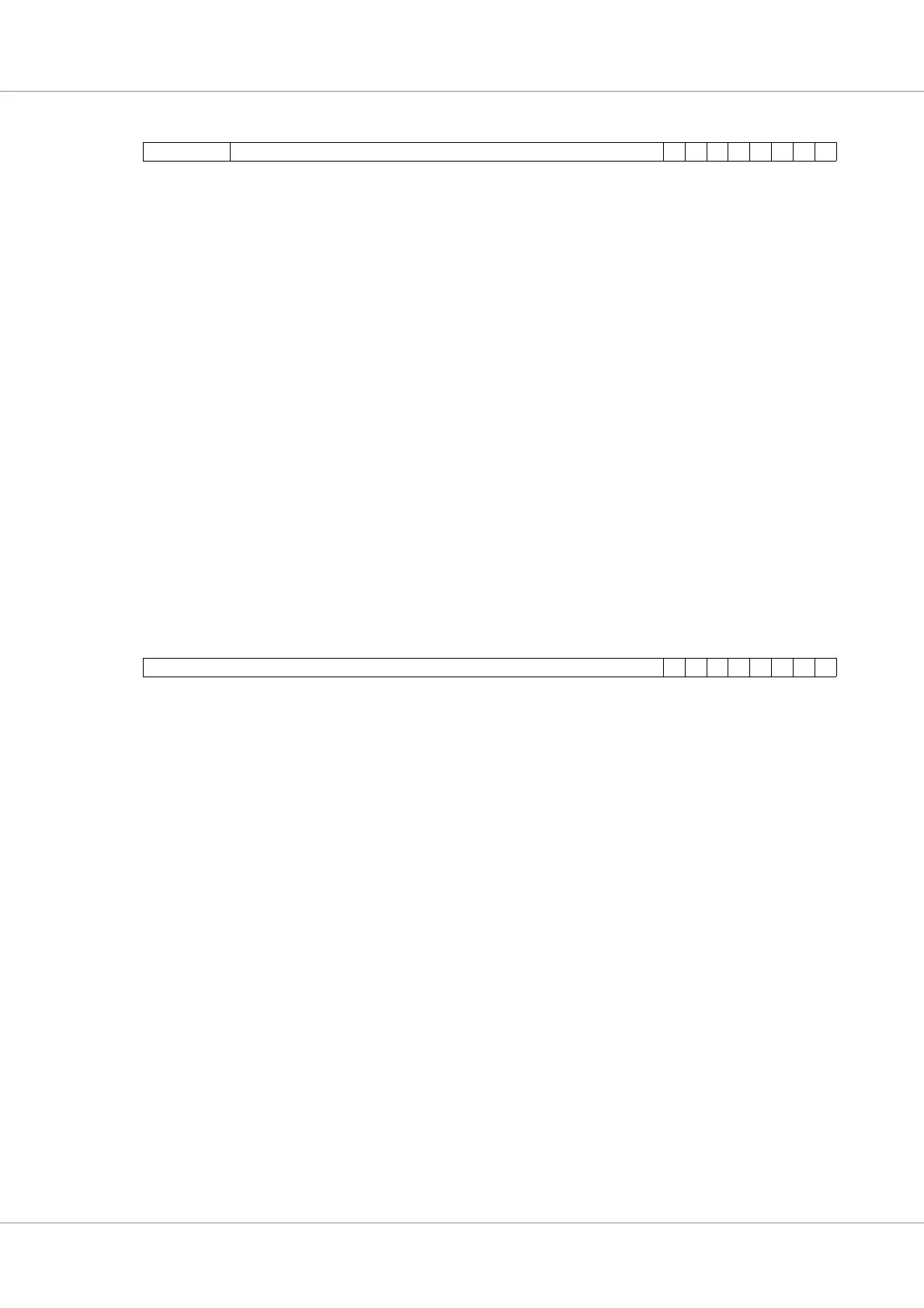

Table 112. GRETH control register

31 28 27 876543210

0000 RESERVED SP RS PM FD RI TI RE TE

27: 8 RESERVED

7 Speed (SP) - Sets the current speed mode. 0 = 10 Mbit, 1 = 100 Mbit. A default value is automati-

cally read from the PHY after reset. Reset value: ‘1’.

6 Reset (RS) - A one written to this bit resets the GRETH core. Self clearing.

5 Promiscuous mode (PM) - If set, the GRETH operates in promiscuous mode which means it will

receive all packets regardless of the destination address. Reset value: ‘0’.

4 Full duplex (FD) - If set, the GRETH operates in full-duplex mode otherwise it operates in half-

duplex. Reset value: ‘0’.

3 Receiver interrupt (RI) - Enable Receiver Interrupts. An interrupt will be generated each time a

packet is received when this bit is set. The interrupt is generated regardless if the packet was

received successfully or if it terminated with an error. Reset value: ‘0’.

2 Transmitter interrupt (TI) - Enable Transmitter Interrupts. An interrupt will be generated each time a

packet is transmitted when this bit is set. The interrupt is generated regardless if the packet was

transmitted successfully or if it terminated with an error. Reset value: ‘0’.

1 Receive enable (RE) - Should be written with a one each time new descriptors are enabled. As long

as this bit is one the GRETH will read new descriptors and as soon as it encounters a disabled

descriptor it will stop until TE is set again. This bit should be written with a one after the new

descriptors have been enabled. Reset value: ‘0’.

0 Transmit enable (TE) - Should be written with a one each time new descriptors are enabled. As long

as this bit is one the GRETH will read new descriptors and as soon as it encounters a disabled

descriptor it will stop until TE is set again. This bit should be written with a one after the new

descriptors have been enabled. Reset value: ‘0’.

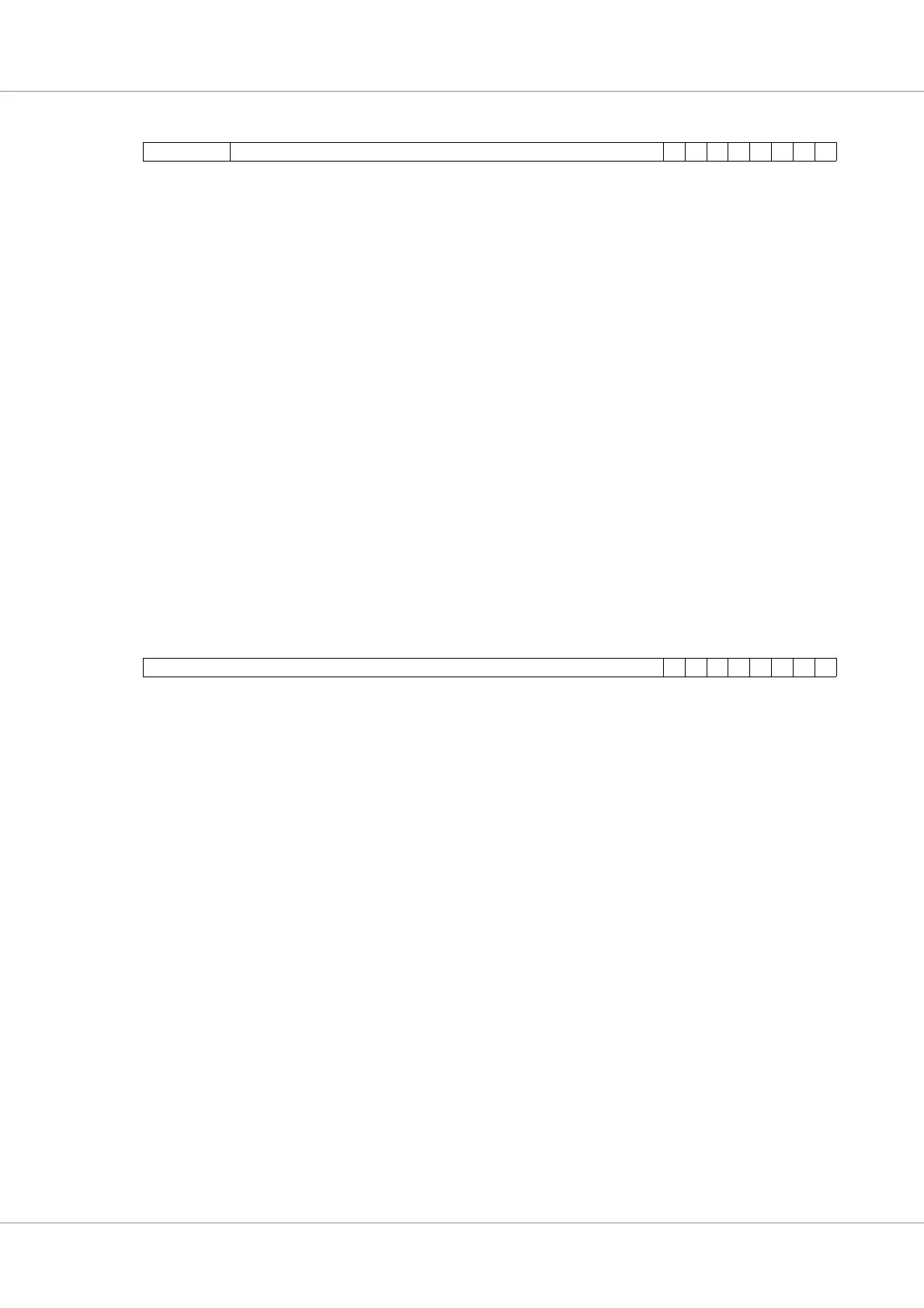

Table 113. GRETH status register

31 876543210

RESERVED IA TS TA RA TI RI TE RE

7 Invalid address (IA) - A packet with an address not accepted by the MAC was received. Cleared

when written with a one. Reset value: ‘0’.

6 Too small (TS) - A packet smaller than the minimum size was received. Cleared when written with a

one. Reset value: ‘0’.

5 Transmitter AHB error (TA) - An AHB error was encountered in transmitter DMA engine. Cleared

when written with a one. Not Reset.

4 Receiver AHB error (RA) - An AHB error was encountered in receiver DMA engine. Cleared when

written with a one. Not Reset.

3 Transmitter interrupt (TI) - A packet was transmitted without errors. Cleared when written with a

one. Not Reset.

2 Receiver interrupt (RI) - A packet was received without errors. Cleared when written with a one. Not

Reset.

1 Transmitter error (TE) - A packet was transmitted which terminated with an error. Cleared when

written with a one. Not Reset.

0 Receiver error (RE) - A packet has been received which terminated with an error. Cleared when writ-

ten with a one. Not Reset.

Loading...

Loading...