GR712RC-UM, Jun 2017, Version 2.9 164 www.cobham.com/gaisler

GR712RC

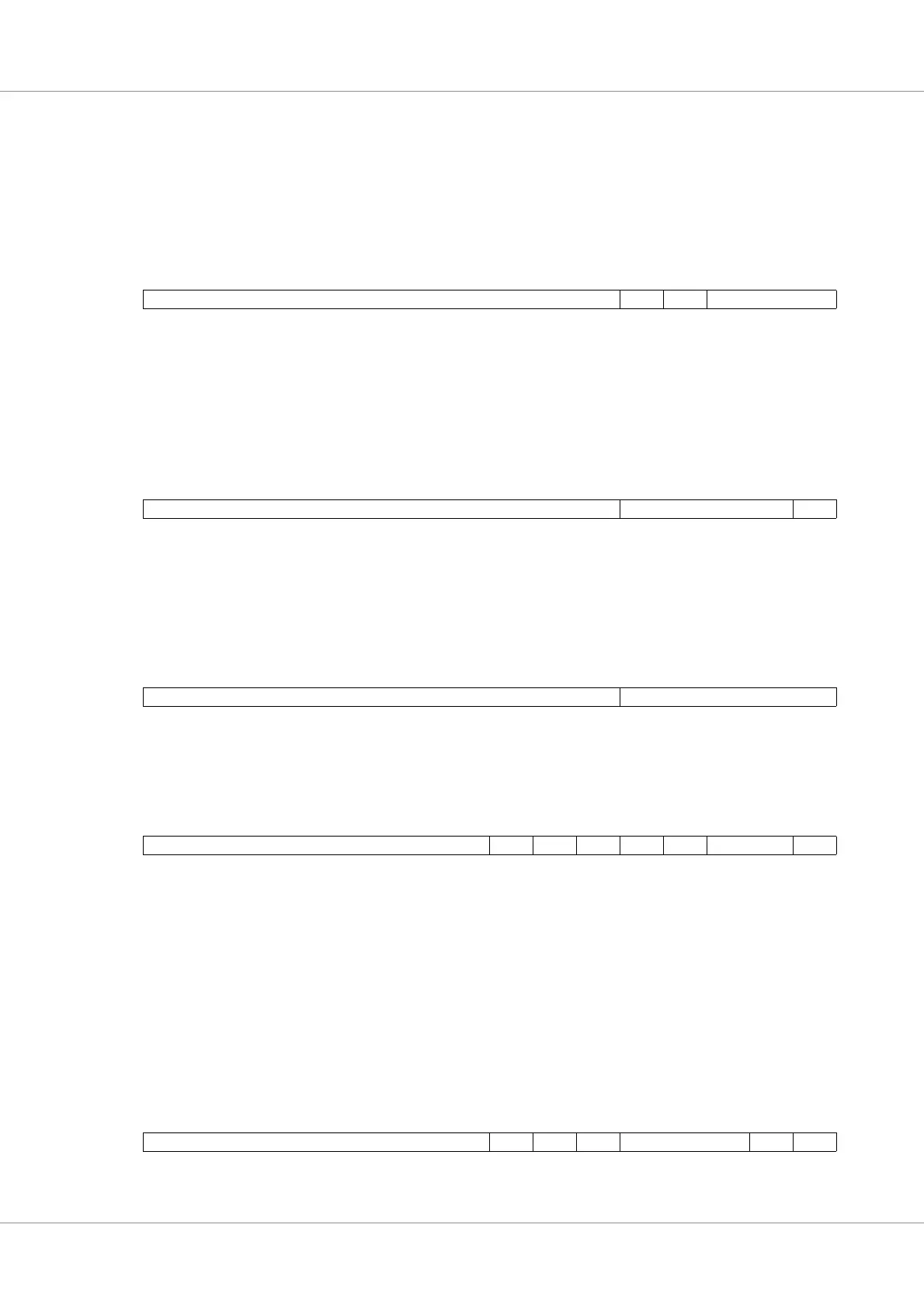

31: 16 RESERVED

15:0 Clock prescale - Value is used to prescale the I2CSCL clock line. Do not change the value of this

register unless the EN field of the control register is set to ‘0’. The minimum recommended value of

this register is 0x0003. Lower values may cause the master to violate I

2

C timing requirements due to

synchronization issues.

Table 166. I

2

C-master control register

31 8765 0

RESERVED EN IEN RESERVED

31: 8 RESERVED

7

Enable (EN) - Enable I

2

C core. The core is enabled when this bit is set to ‘1’.

6 Interrupt enable (IEN) - When this bit is set to ‘1’ the core will generate interrupts upon transfer

completion.

5:0 RESERVED

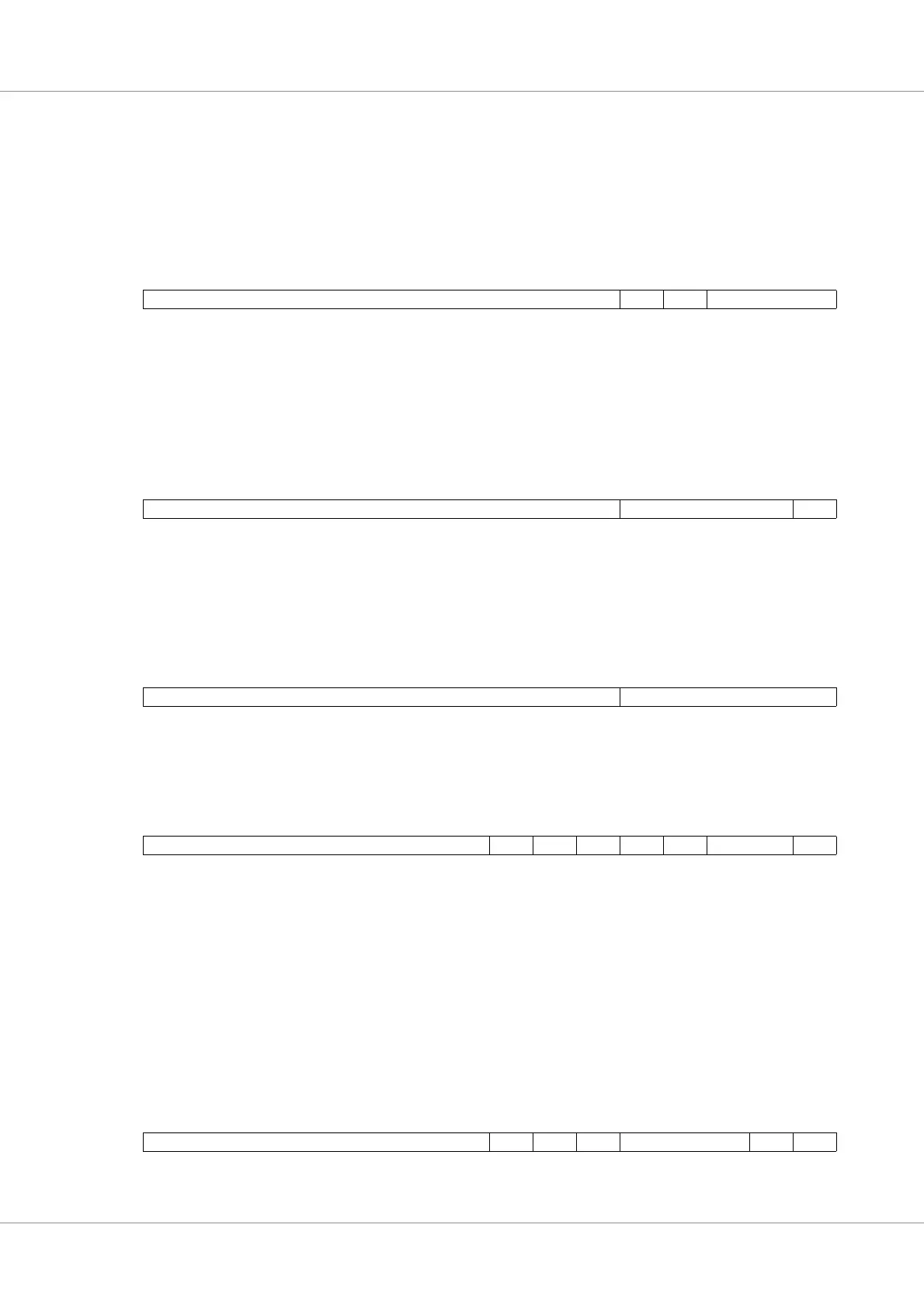

Table 167. I

2

C-master transmit register

31 87 10

RESERVED TDATA RW

31: 8 RESERVED

7:1

Transmit data (TDATA) - Most significant bits of next byte to transmit via I

2

C

0 Read/Write (RW) - In a data transfer this is the data’s least significant bit. In a slave address transfer

this is the RW bit. ‘1’ reads from the slave and ‘0’ writes to the slave.

Table 168. I

2

C-master receive register

31 87 0

RESERVED RDATA

31: 8 RESERVED

7:0

Receive data (RDATA) - Last byte received over I

2

C-bus.

Table 169. I

2

C-master command register

31 876543210

RESERVED STA STO RD WR ACK RESERVED IACK

31: 8 RESERVED

7

Start (STA) - Generate START condition on I

2

C-bus. This bit is also used to generate repeated

START conditions.

6 Stop (STO) - Generate STOP condition

5 Read (RD) - Read from slave

4 Write (WR) - Write to slave

3 Acknowledge (ACK) - Used when acting as a receiver. ‘0’ sends an ACK, ‘1’ sends a NACK.

2:1 RESERVED

0 Interrupt acknowledge (IACK) - Clears interrupt flag (IF) in status register.

Table 170. I

2

C-master status register

31 876543210

RESERVED RxACK BUSY AL RESERVED TIP IF

31: 8 RESERVED

Table 165. I

2

C-master Clock prescale register

Loading...

Loading...