GR712RC-UM, Jun 2017, Version 2.9 83 www.cobham.com/gaisler

GR712RC

[15:0]: Enter debug mode (EDx) - Force processor x into debug mode if any of processors in a multiprocessor system enters

the debug mode. If 0, the processor x will not enter the debug mode.

[31:16]: Debug mode mask. If set, the corresponding processor will not be able to force running processors into debug mode

even if it enters debug mode.

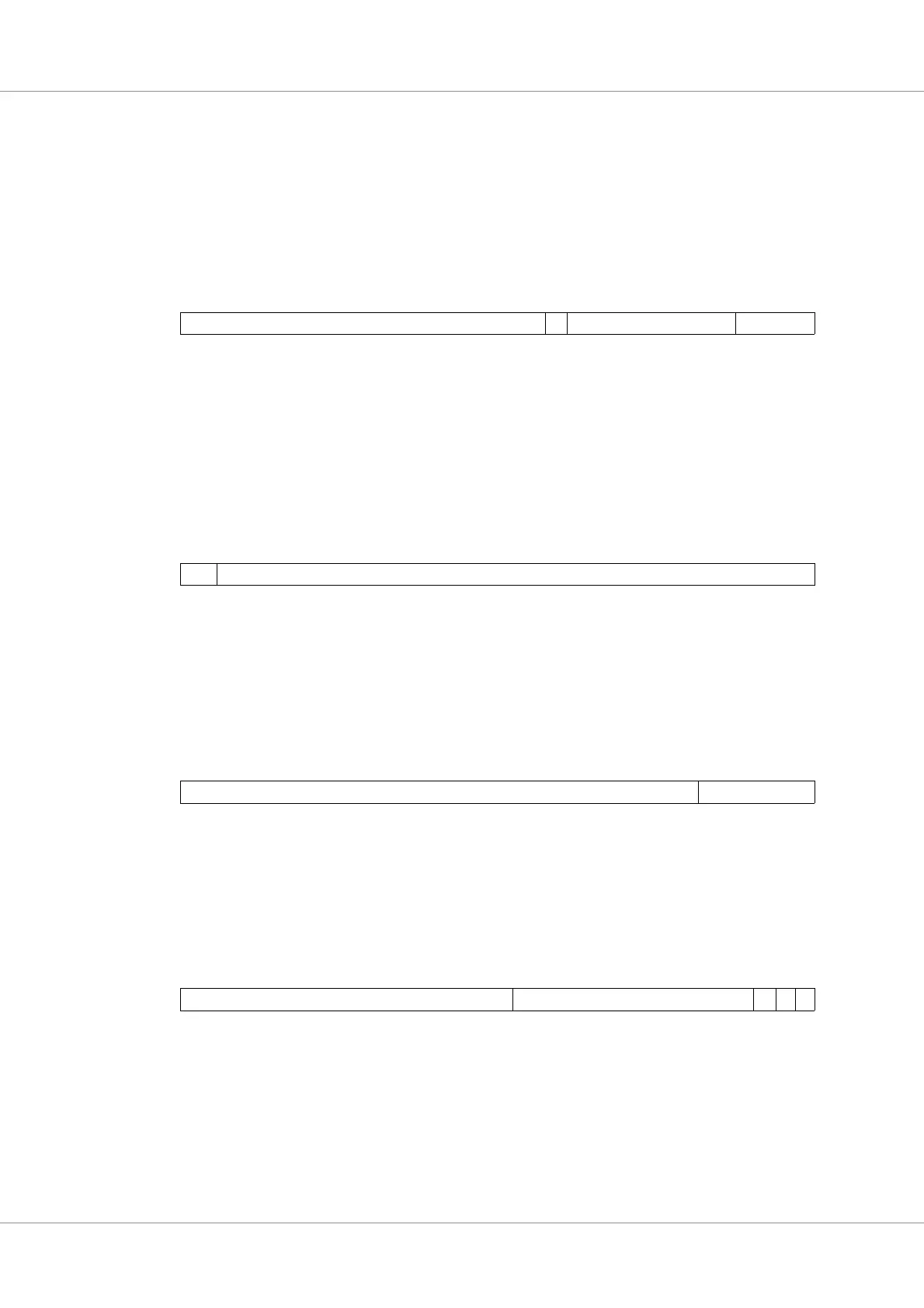

9.6.4 DSU trap register

The DSU trap register is a read-only register that indicates which SPARC trap type that caused the

processor to enter debug mode. When debug mode is force by setting the BN bit in the DSU break and

single step register, the trap type will be 0xb (hardware watchpoint trap).

[11:4]: 8-bit SPARC trap type

[12]: Error mode (EM). Set if the trap would have cause the processor to enter error mode.

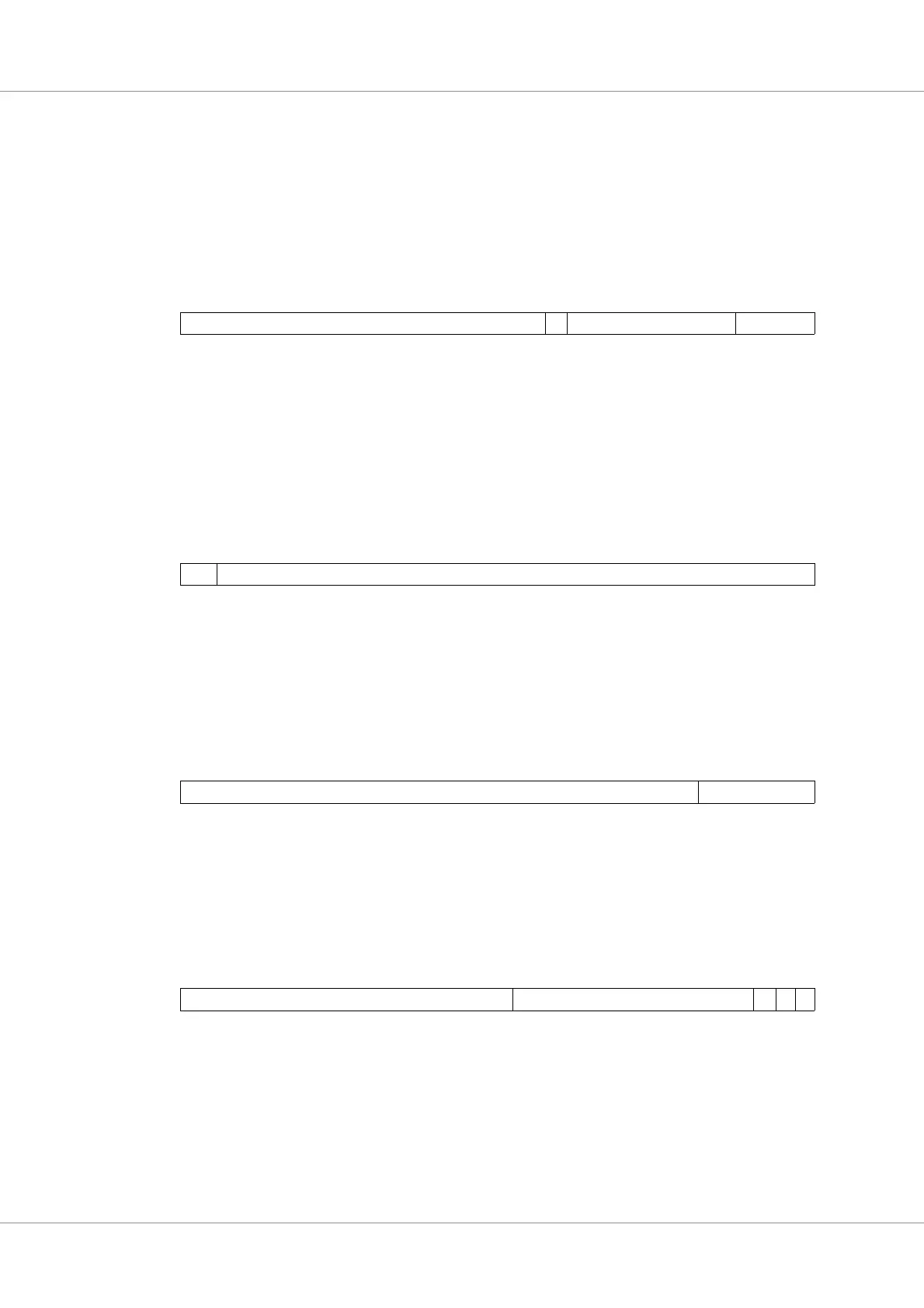

9.6.5 Trace buffer time tag counter

The trace buffer time tag counter is incremented each clock as long as the processor is running. The

counter is stopped when the processor enters debug mode, and restarted when execution is resumed.

The value is used as time tag in the instruction and AHB trace buffer.

9.6.6 DSU ASI register

The DSU can perform diagnostic accesses to different ASI areas. The value in the ASI diagnostic

access register is used as ASI while the address is supplied from the DSU.

[7:0]: ASI to be used on diagnostic ASI access

9.6.7 AHB Trace buffer control register

The AHB trace buffer is controlled by the AHB trace buffer control register:

[0]: Trace enable (EN). Enables the trace buffer.

[1]: Delay counter mode (DM). Indicates that the trace buffer is in delay counter mode.

[2]: Break (BR). If set, the processor will be put in debug mode when AHB trace buffer stops due to AHB breakpoint hit.

[31:16] Trace buffer delay counter (DCNT). Note that the number of bits actually implemented depends on the size of the

trace buffer.

Figure 46. DSU trap register

034

31

RESERVED

0000

11

TRAP TYPE

12

EM

13

Figure 47. Trace buffer time tag counter

0

31

DSU TIME TAG VALUE

29

00

Figure 48. ASI diagnostic access register

0

31

7

ASI

Figure 49. AHB trace buffer control register

01

31

DCNT

ENRESERVED

16

DM

2

BR

Loading...

Loading...